Дискретное фазосдвигающее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматического управления и контроля в каналах цифровых следящих систем. Целью изобретения является повышение помехоустойчивости. Дискретное фазосдвигающее устройство (ФСУ) содержит шину 1 "Кода", шину 2 "Запись", шину 3 "Пуск", опорный генератор 4, первый и второй делители 6, 5 частоты, первый и второй инверторы 7, 8, первый и второй регистры 9, 10 памяти, первый и второй D-триггеры 11, 12, логическую схему И 13, выходы первого и второго делителей частоты являются соответственно первым (управляемым) и вторым (опорным) выходами устройства. Особенностью изобретения является введение регистра 10, схемы И 13, делителя 5, инверторов 7, 8, которое позволяет с помощью второго делителя частоты и логической схемы И формирователь сигнал управления, по которому в каждом периоде формируемого ФСУ сигнала в первый делитель частоты из второго регистра памяти записывается код фазы, а совокупность второго инвертора, первого и второго D-триггеров и первого регистра памяти осуществляет синхронизацию смены информации на шинах "Кода" и "Пуск" с тактовым сигналом ФСУ. При этом за счет того, что сигнал управления формируется в каждом периоде и ФСУ управляется по фазе выходного сигнала, а не по ее приращению, повышается помехозащищенность. 2 ил.

COIO3 СО8ЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)ю G 01 R 25/04

ГОСУДАРСТВЕННЫ И КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4715305/21 (22) 04.07.89 (46) 30.07,91. Бюл. М 28 (71) Московское конструкторское бюро

"Компас" (72) Ю.Б.Розенберг, Г.Г.Дрейер и А.Ш.Перельман (53) 621.317.77 (088.8) (56) Авторское свидетельство СССР

N 1406748, кл. G 01 R 25/04, 1986. (54) ДИСКРЕТНОЕ ФАЗОСДВИГАЮЩЕЕ

УСТРОЙСТВО (57) Изобретение относится к импульсной технике и может быть использовано в устройствах автоматического управления и контроля в каналах цифровых. следящих ,систем. Целью изобретения является повышение помехоустойчивости. Дискретное фаэосдвигающее устройство (ФСУ) содержит шину 1 "Код", шину 2 "Запись", шину 3

"Пуск", опорный генератор 4, первый и второй делители 6,5 частоты, первый и второй инверторы 7,8, первый и второй регистры

„„5UÄÄ 1666970 А1

9,10 памяти, первый и второй D-триггеры 11, 12, логическую схему И 13, выходы первого и второго делителей частоты являются соответственно первым (управляемым) и вторым (опорным) выходами устройства.

Особенностью изобретения является введение регистра 10, схемы И 13, делителя 5, инвеоторов 7,8, которое позволяет с помощью второго делителя частоты и логической схемы И формировать сигнал управления, по которому в каждом периоде формируемого ФСУ сигнала в первый делитель частоты из второго регистра памяти записывается код фазы. а совокупность второго инвертора, первого и второго D-триггеров и первого регистра памяти осуществляет синхронизацию смены информации на шинах "Код" и "Пуск" с тактовым сигналом ФСУ. При этом за счет того, что сигнал управления формируется в каждом периоде и ФСУ управляется по фазе выходного сигнала, а не по ее приращению, превышается помехозащищенность. 2 ил.

1666970

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматического управления и контроля в каналах цифровых следящих систем, Целью изобретения является повышение помехоустойчивости.

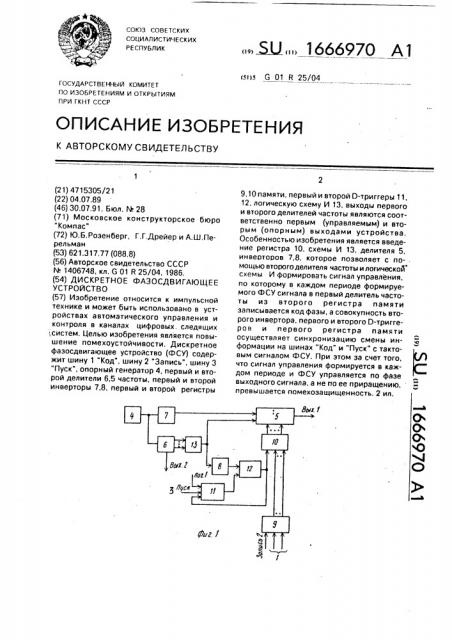

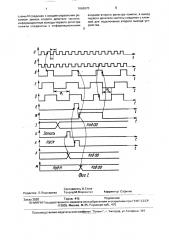

На фиг. 1 приведена структурная электрическая схема дискретного фазосдвигающего устройства; на фиг. 2 — изображены временные диаграммы сигналов в характерных точках устройства для варианта реализации ФСУ-фазосдвигающего устройства, в котором делители частоты выполнены на базе двухраэрядных двоичных счетчиков импульсов.

Дискретное фаэосдвигающее устройство (фиг.1) содержит шину 1 "Код", шину 2

"Запись", шину 3 "Пуск", опорный генератор 4, второй 5 и первый 6 делителичастоты, первый и второй инверторы 7, 8, первый 9 и второй 10 регистры памяти, первый 11 и второй 12 0-триггеры, логическую схему И

13. Выходы первого и второго делителей частоты являются соответственно первым (управляемым) и вторым (опорным) выходами устройства.

На тактовый С вход делителя б частоты, который реализуется на основе счетчика импульсов, с выхода генератора 4 поступают тактовые импульсы скважности q=2, эти же импульсы через инвертор 7 поступают на тактовый С вход делителя 5 частоты, который реализуется на основе счетчика импульсов с предварительной установкой заданного кода, например типа К155 ИЕ9.

Выходы первого и второго делителей частоты. например выходы последних разрядов, являются соответственно первым и вторым выходами устройства.

Выходы разрядов делителя 6 частоты соединены с соответствующими входами логической схемы И 13, а ее выход соединен с V-входом управления режимом записи делителя 5 частоты и через инвертор 8 соединен с тактовым С входом 0-триггера 12, Информационный вход D-триггера 12 соединен с выходом 0-триггера 11. Информационный вход D-триггера 11 соединен с потенциалом "Лог.1", его тактовый С вход соединен с шиной 3 "Пуск", а установочный

R-вход соединен с выходом 0-триггера 12 и тактовым С-входом регистра 10 памяти, Qвыходы соответствующих разрядов которого соединены с соответствующими разрядами информационного (установочного) входа делителя 5. D-входы соответствующих разрядов регистра 10 соединены с выходами соответствующих разрядов регистра Q, информационные 0-входы которого

20 соединены с шиной 1 "Кода" фазы, а тактовый С-вход соединен с шиной 2 "Запись".

При реализации данного устройства в некоторых случаях может оказаться целесообразным формировать сигнал "Пуск", используя сигнал "Запись". Для этого тактовый вход 0-триггера 11 необходимо соединить через инвертор с шиной 2 "Запись"

При этом триггер 11 будет устанавливаться в единичное состояние по заднему фронту сигнала "Запись", т.е. заведомо после эавершения переходного процесса в регистре

9.

Дискретное фазосдвигающее устройство работает следующим образом.

В исходном состоянии триггеры 11 и 12 находятся в состоянии "0".

Генератор 4 формирует на своем выходе тактовые импульсы скважности р-2. Эти импульсы поступают на тактовый С-вход делителя б частоты и через инвертор 7 — на тактовый С-вход делителя 5 частоты. Оба делителя частоты выполнены на основе цифровых счетчиков одинаковой емкости.

25 3а счет инвертора 7 активный фронт тактовых импульсов на входе делителя 5 сдвинут на Т/2 (Т вЂ” период тактовых импульсов) по .отношению к активному фронту тактовых импульсов на входе делителя б (фиг. 2а, б).

30 3а счет этого счет импульсов (смена состояний) делителей 5 и 6 (счетчиков) происходит с временным сдвигом, равным Т/2, При достижении делителя б состояния "1 во всех разрядах на выходе логической схе35 мы И 13 формируется импульс, поступающий на V-вход управления режимом записи делителя 5 (фиг.2в). Ilo активному фронту первого же импульса, поступающего на тактовый вход делителя 5, во время действия

40 управляющего сигнала на его V-входе делитель 5 из регистра 10 перепишется содержащийся в нем код фазы.

Следующий тактовый импульс на входе делителя 6 изменит его состояние, что при45 ведет к завершению формирования управляющего сигнала V на выходе схемы И 13.

При этом делитель 5 переводится в режим счета, и следующий и последующие тактовые импульсы на его С-входе суммируются

50 с числом, записанным в делитель 5 во время действия управляющего сигнала на его Vвходе.

Описанный процесс повторяется пери1 одически с частотой F = -Т где Т вЂ” период пТ тактовых импульсов; и — коэффициент деления делителей б и 5.

Результатом описанной выше принудительной записи в делителе 5 содержимого регистра 10 является синхронизация дели1ГГ69, 0 теля 5 опорным сигналом, формируемым делителем 6.

Фаза сигнала на выходе делителя 5 по отношению к опорному сигналу в зависимости от кода в регистре 10 может принимать 5 любое из и дискретных значений, Если обэ делителя выполнены на основе двоичных ф/ счетчиков. то и = 2, где N — число разрядов счетчиков, т.е. дискрет фазы Лробеспечиваемый фазосдвигающим устройством, со- 10

2;г ставляет величину Л р = ——

r>

Фэза <р сигнала на выходе ФСУ по отношению к опорному сигналу определяется выражением 15

7Г ."г

p=Ê + — —, 2N 1 2N где k -- число. задаваемое в регистр 10.

Второй член в выражении (1) определяет постоянный фазовый сдвиг, обусловленный временным сдвигом на Т/2 тактовых импульсов делителей 5 и 6.

Запись кода фазы с шины 1 кодл (фи».2з) в регистр 10 осуществляется следуюгцим образом.

Первоначально код фазы с шины 1 записывается в регистр 9 импульсом, поступающим на его тактовый С-вход с шины 2

"Запись" (фиг, 2и).

Сигнал "Пуск" (фиг. 2к), который формируется после импульса "Запись", поступает на тактовый вход триггера 11. По его переднему фронту триггер 11 устанавливается в единичное состояние (фиг.2е). Задним фронто1л выходного сигнала схемы И 13 триггер 12 устанавливается в единичное состояние (фиг.2ж) и своим выходны л сигналом осуществляет запись кода фазы в регистр 10 иэ регистра 9 (фиг. 2ж,л»). Таким образом, смена кода на информационных 40 входах делителя 5 всегда происходит в течение интервала времени, когда делитель 5 находится в режиме счета (сигнал управления на V-входе ранен нулю).

Таким образом, смена кода фазы в регистре 10. как и в прототипе, синхрониэованэ тактовым сигналом генератора 4. «то исключает сбои в работе ФСУ при смене кода фазового сдвига несмотря нэ то, что сигналы управления ФСУ "Запись" и "Пуск" эсинхронны по отношени»о к его тактовому сигналу.

Как видно из приведенного выше описания, управление данным диск ретны л фазосдвигающим устроиством осуществляется по фазе, а не по приращению фазы как это имеет место 8 прототипе. Следствием такого управления являегся отсу»ствие нэкопления ошибки»»1 и единичных сбоях в

ФСУ.

Так, например, ложное срабать1вание триггера 11, вызванное помехой по шине

"Пуск", не приведет к сдв»»гу фазы выходного сигнала ФСУ, если при этом не искажена

» нформация в регистре 10.

Искажение информации в регистре 9 не приведет к сдвигу фазы выходного сигнала в о»сутствие сигнала "Пуск".

Од»»овременное воздейсгвие помех по шинам "Запись" и "Г!уск" может привести к искажению информации в регистре 10 и соответствующему сдвигу фазы выходного сигнала ФСУ. Однако в следующем we цикле обращения внешнего устройства к ФСУ (по шинам 1-3) этот фазовый сдвиг будет скорректирован.

Таким образом, в данном устройстве не происходит накопления ошибки, обусловленной его ложныл» срабатыванием вследствие по лех по шинам управления, что повышает помехоустойчивость.

Формула изобре ения

Дискретное фазосдвигающее устройство, содержащее опорный ге>»ератор и первый делитель частоты, соединенные последовательно, первый регистр памяти, первый и второй информационные входы которого соответственно являются клеммами для подключения шин "Код" и "Запись", первый и второи 0-»риггеры, информационный выход первого D-Tðèïeðà соединен с информационным входом в»орого D-триггера, информационный выход второго 0-триггера соеди»»ен с установо»ным R-входом первого О-триггера, информационный Овход первого D-триггера является клеммой для подключения шины с потенциалом

"Лог.1", а тактовый является клеммой для подключения шины "Пуск", клемму для подключения первого выхода устройства, о тл и ч а ю щ е е с я тем, что, с целью повышения помехоустойчивости, в него введены второй регистр па ляти. логическая схема И, второй делитель частоты, клемма для псдключения второ о выхода устройства и первый и второи инверторы, причем выход опорного генератора соединен последовательно с первым инвертором тактовым входом второго делителя частоты, выход которого соединен с клеммой первого выхода устроиства, выходы разрядов первого делителя частоты последовательно соединены с логи«ескои схемой И, вторым инвертором, тактовым входом второго 11триггера, тактовым входом второго регистра памяти и информационными входами второго делителя «эстоты, выход логической

1ббб970

Составитель В,Ежов

Редактор Л.Лошкарева Техред М.Моргентал Корректор О.Ципле

Заказ 2520 Тираж 415 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г, Ужгород, ул.Гагарина, 101 схемы И соединен с входом управления режимом записи второго делителя частоты, информационные выходы первого регистра памяти соединены с информационными входами второго регистра памяти, а выход первого делителя частоты соединен с клеммой для подключения второго выхода устройства.