Устройство для формирования синхроимпульсов

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для управления и выработки синхронизирующих импульсных последовательностей и одиночных импульсов. Отличительной особенностью устройства является то, что оно позволяет получить четыре серии различных импульсных последовательностей, а также одиночные импульсы, вырабатываемые при запуске устройства. При этом устройство работает только во время, необходимое пользователю, начало которого определяет сигнал на входе 24, а конец - сигнал на входе 26. Целью изобретения является расширение функциональных возможностей за счет обеспечения переменного периода между импульсами в заданном интервале времени. Поставленная цель достигается за счет введения элементов И - НЕ 7, 8, элемента НЕ 6, элементов И - НЕ 9 - 12, элементов И 15 - 18, элементов ИЛИ 19 - 22, триггера 3 и регистра 4. 4 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)5 G 06 F 1/04

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1 о (;Ь 4

О

6д

° ааеаЪ

2б (21) 4741274/24 (22) 04.08.89 (46) 30.07.91, Бюл. N 28 (71) Научно-производственное объединение

"Агат" (72) Ю.А, Буслаев, Н.Ю. Дйдух и А,А. Драгунов (53) 681.3(088.8) (56) Авторское свидетельство СССР

М 1223218. кл, G 06 F 1/04, 1983, Авторское свидетельство СССР

Vb 781801, кл. G Oi F 1/04, 1982. (54) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ

СИНХРОИМПУЛЬ СОВ (57) Изобретение относится к вычислительной технике и может быть использовано для управления и выработки синхронизирующих импульсных последовательностей и

„„5U„„1667039 А1 одиночных импульсов. Отличительной особенностью устройства является то, что оно позволяет получить четыре серии различных импульсных последовательностей, а также одиночные импульсы, вырабатываемые при запуске устройства. При этом устройство работает только во время, необходимое пользователю, начало которого определяет сигнал на входе 24, а конец — сигнал на входе 26.

Целью изобретения является расширение функциональных возможностей за счет обеспечения переменного периода между импульсами в заданном интервале времени.

Поставленная цель достигается за счет введения элементов И вЂ” НЕ 7 и 8, элемента НЕ

6, элементов И вЂ” НЕ 9 — 12, элементов И 15—

18, элементов ИЛИ 19 — 22, триггера 3 и регистра 4. 4 ил.

1667039

10 l5

27-30, выход 31 готовности к работе, выходы 32-34 одиночного импульса 35-47 — свя- 25

Изобретение относится к вычислительной технике и может быть использовано для управления и выработки синхрониэирующих импульсных последовательностей и

ОДИНОЧНЫХ ИМПУЛЬСОВ.

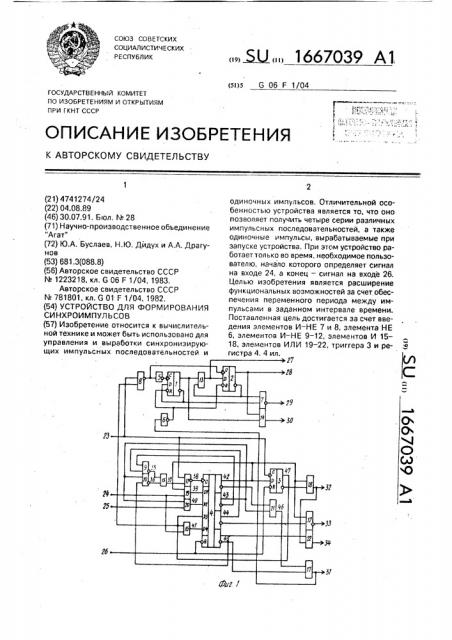

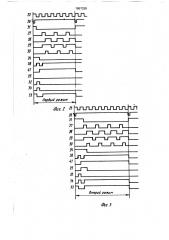

Цель изобретения — расширение функциональных возможностей за счет Обеспечения переменного периода между импульсами в заданном интервале времени, На фиг; 1 приведена структурна схема ! устройства; на фиг. 2 и 3- временные диаграммы первого и второго режимов работы устройства соответственно; на фиг. 4 — временная диаграмма формирования импульсов на выходах регистра и третьего триггера.

Устройство содержит триггеры 1-3, регистр 4, элементы HE 5 и 6, элементы И вЂ” НЕ

7-12, элементы И 13 — 18, элементы ИЛИ 19—

22, тактовый вход 23, вход 24 запуска, вход

25 разрешения переменного периода, вход

26 начальной установки, тактсвые выходы зи между элементами устройства.

Устройство работает следующим образом.

Первый режим работы, Временная диаграмма этого режима приведена на фиг. 2. На фиг, 4 приведена подробная временная диаграмма работы регистра 4, триггера 3 и прилегающих к ним элементов 9, 10, 11, 15, 16, 19, 20, 21, После включения питания по входу 26 подается сигнал "Сброс" отрицательным перепадом, 3гот сигнал устанавливает в нулевое состояние регистр 4 и триггер 3, На выходе 31 появляется сигнал "Готов к работе", который запрещает работать триггерам t и 2., Чтобы устройство качало работать, на вход

24 поступает положительный импульс, минимальная длительность которого должна соответствовать одному периоду синхрочастоты. Этот сигнал через элемент ИЛИ 19 поступает на первый информационный вход регистра. запись осуществляется первым же отрицательным импульсом синхрочастоты. На вход 25 подается логический ноль, на вход 26 — логическая единица, Записанный по первому информационному входу регистра 4 сигнал устанавливает в единичное состояние триггер 3, На прямом выходе триггера 3 появляется логическая единица, которая разрешает прохождение синхрочастоты на триггеры 1 и 2. Вследствие этого на выходы 27-30 поступают сформированные последовательности импульсов. Одновременно с этим на выходах 32 и 34 появятся по одному поло35

50 жительному импульсу, длительность которых равна длительности отрицательного импульса синхрочастоты, На выходе 33 появится одиночный импульс отрицательной полярности, длительность которого равна длительности периода синхрочастоты.

Информация (фиг. 4) записанная на регистр по сигналу разрешения записи, устанавливает всю управляющую часть устройства в постоянное состояние, которое разрешает работать формирующей части устройства все необходимое время. При этом одиночные импульсы, снимаемые с выходов 32-34, не вырабатываются.

Сигнал, поступающий по входу 26, является сигналом об окончании работы и переводит устройство в исходное состояние, т,е. останавливает выработку сигналов, снимаемых с выходов 27 — 30, и вырабатывает сигнал на выходе 31 Готов к работе", Второй режим работы.

Временная диаграмма этого режима приведена на фиг. 3. После включения питания по входу 26 подается сигнал "Сброс", который устанавливает регистр 4 и триггер

3 в начальное, нулевое, состояние, На выходе 31 появляется импульс положительной полярности "Готов к работе". Через некоторое время после появления этого сигнала на вход 24 можно подавать импульс положительной полярности, минимальная длительность которого должна быть равна двум периодам синхрочастоты. Запись в регистр

4 осуществляется первым же отрицательным импульсом сихрочастоты.

Записанный на регистр 4 сигнал переписывается на триггер 3, в результате чего на одном из входов элемента И вЂ” НЕ 8 появляется логическая единица, которая пропускает синхрочастоту через элемент И-HE 8 на входы триггеров 1.и 2. На выходах 27-30 появляются сформированные импульсные последовательности. Таким образом, работа в первый период синхрочастоты аналогична работе формирователя в первом режиме, К концу первого периода синхрочастоты на вход 25 приходит импульс положительной полярности, который записывается на регистр 4 по второму информационному входу вторым сигналом разрешения записи регистра 4. В результате на втором прямом выходе регистра 4 появляется сигнал, который, не нарушая работы триггеров 1 и 2, формирует дополнительный сигнал на выходе 34, Работа управляющей части схемы в этом режиме подробно показана на фиг. 4, Отличие второго режима от первого состоит в том, что сигнал, приходящий на вход

25, позволяет сформировать еще один до1667039

15

55 полнительный, одиночный импульс на выходе 34, Формула изобретения

Устройство для формирования синхроимпульсов, содержащее два триггера, первый элемент НЕ, два элемента И, причем выход первого элемента И соединен с информационным входом первого триггера и является первым тактовым выходом устройства, инверсный выход первого триггера соединен с первым входом первого элемента

И, прямой выход первого триггера соединен с первым входом второго элемента И и является вторым тактовым выходом устройства, выход второго элемента И является третьим тактовым выходом устройства, и рямой выход второго триггера соединен с вторыми входами первого и второго элементов

И, инверсный выход второго триггера соединен с информационным входом второго триггера, синхровход которого соединен с выходом первого элемента Н Е, вход которого соединен с синхровходом первого триггера, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения переменного периода между импульсами в заданном интервале времени, в него введены третий триггер, второй элемент НЕ, четыре элемента И, шесть элементов И-НЕ, четыре элемента ИЛИ и регистр, причем прямой выход первого разряда регистра соединен с информационным входом третьего триггера, с первым входом первого элемента ИЛИ, с первым входом первого элемента

И вЂ” НЕ и с первым входом третьего элемента

И, второй вход которого соединен с инверсным выходом третьего триггера, выход третьего элемента И соединен с первым входом второго элемента ИЛИ и является первым выходом одиночного импульса устройства, выход второго элемента ИЛИ является вторым выходом одиночного импульса устройства, инверсный выход первого разряда регистра соединен с первым входом третьего элемента ИЛИ, прямой выход второго разряда регистра соединен с вторым входом третьего элемента ИЛИ, с первым входом второго элемента И вЂ” НЕ и с первым входом четвертого элемента ИЛИ, выход третьего элемента ИЛИ соединен с первым входом четвертого элемента И, инверсный выход второго разряда регистра соединен с первым входом третьего элемента И-НЕ, второй вход которого соединен с прямым выходом третьего разряда регистра, инверсный выход третьего разряда которого соединен с вторым входом первого элемента

И вЂ” Н Е, прямой выход четвертого разряда регистра- соединен с вторым входом второго элемента ИЛИ, с вторым входом второго элемента И-НЕ, выход которого соединен с первым входом пятого элемента И, второй вход которого соединен с выходом третьего элемента И вЂ” НЕ, выход пятого элемента И соединен с первым входом четвертого элемента И-НЕ, второй вход которого соедиН8Н с синхровходом третьего триггера, с первым входом пятого элемента И вЂ” НЕ и является тактовым входом устройства, инверсный выход четвертого разряда регистра соединен с вторым входом четвертого элемента И, выход которого соединен с входом второго элемента НЕ и является выходом признака готовности работы устройства, выход первого элемента И-НЕ является третьим выходом одиночного импульса устройства, вход сброса в "0" регистра соединен с входом сброса "0" третьего триггера и является входом начальной установки уст.ройства, второй вход четвертого элемента

ИЛИ является входом разрешения переменного периода выходных импульсов устройства, второй вход первого элемента ИЛИ соединен с первым входом шестого элемента И и является входом запуска устройства, прямой выход третьего триггера соединен с вторым входом шестого элемента И, с информационным входом третьего разряда регистра и с вторым входом пятого элемента И вЂ” НЕ, выход которого соединен с синхровходом первого триггера, вход сброса в

"0" которого соединен с входом сброса в "0" второго триггера и с выходом второго элемента НЕ, инверсный выход первого триггера соединен с первым входом шестого элемента И вЂ” НЕ, второй вход которого соединен с инверсным выходом второго триггера, выход шестого элемента И вЂ” НЕ является. четвертым тактовым выходом устройства, выход четвертого элемента И-НЕ соединен с синхровходом регистра, информационный вход первого разряда которого соединен с выходом первого элемента ИЛИ, выход четвертого элемента ИЛИ соединен с информационным входом третьего разряда регистра, выход шестого элемента И соединен с информационным входом четвертого разряда регистра.

В

У

zg

zg

ГУ

Ю

Я

38

47

Я

5Я

3667039

1667039

В

М

Ц

Ц

Ы

О

57

58 ф

lj:I

Составитель Н, Торопова

Техред M.Ìoðãåíòàë Корректор M.Äåì÷èê

Редактор Н. Химчук

Производственно-издательский комбинат "Патент", r. Ужгород, ул.Гагарина, 101

Заказ 2523 Тираж 396 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5