Устройство для деления

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой вычислительной технике и предназначено для использования в универсальных и специализированных вычислительных устройствах. Целью изобретения является сокращение аппаратурных затрат при реализации в устройстве для деления оперативного обнаружения ошибок вычислений. Оперативное обнаружение ошибок вычислений заключается в проведении повторного вычисления со сдвинутыми операндами и сравнении его результатов с результатами первого вычисления. При этом устройство для деления характеризуется временной и аппаратурной избыточностью. Поставленная цель достигается тем, что при повторном вычислении делитель сдвигается на один разряд вправо, делимое сдвигается на два разряда вправо. Такая организация сдвигов операндов позволяет сократить аппаратурную избыточность при реализации устройства. Устройство для деления позволяет обнаружить все ошибки вычислений в матрице деления с восстановлением остатка, если ее неисправность ограничена неисправностью одной ячейки матрицы. В состав устройства входят вычислительные ячейки 6, элементы НЕ 7, регистры 8, 10 частотного и остатка, компараторы 9, 11 частного и остатка, элемент 12 ИЛИ, входы 1.1 - 1.N делителя, входы 2.(-M + 1) - 2.N делимого, выходы 3.1 - 3.M частного, выходы 4.1 - 4.N остатка, выход 5 контроля правильности вычислений, первый и второй управляющие входы 13, 14 устройства. 2 ил.

СОЮЗ СОВЕТСКИХ сОциАлистичесних

РЕСПУБЛИК

„.80 l667ßÄ7 (5 ) г 06 F ?/52, 11/О 3

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н A ВТОРСКОЬЮ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ пО изоБРетениям и ОтнРытиям

ПРИ ГКНТ СССР (21 ) 4687 f 52 724 (22) 05.05.89 (46) 30.07.91. Бюл. N 28 . (71) Харьковский автомобильно-дорожный институт им. Комсомола Украины (72) В.В. Шатилло, С.Н. Прохоров и Л.С. Явиц (53) 681 ° 325 (088.8) (56) Карцев М.А., Брик В.А. Вычислительные системы и сиихронная арифметика. И.: Радио и связь, 1981, с. 224, рис. 5.1.2.

Patel Т.Н., Fung 1 .У. Concurrent

Error Detection in Multiplay and

Divide Arrays. IEEE Transactions on

Computers, 1983, v. с. 32., М 4, р. 417 422, fig. 5. (54) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ (57) Изобретение относится к цифровой вычислительной технике и предназначено для использования в универсальных и специализированных вычислительных устройствах. Целью изобретения является сокращение аппаратурных затрат при реализации в устройстве для деления оперативного обнаружения ошибок вычислений. Оперативное обнаружение ошибок вычислений заключается в проведении повторного вычисления со слвинутыми Операндами и сравнении его результатов с результатами первого вычисления. При этом устройство для деления характеризуется временной и аппаратурной избыточностью. Поставленная цель достигается тем, что при повторном вычислении делитель сдвигается на один разряд вправо, делимое сдвигается на два разряда вправо. Такая организация сдвигов операндов позволяет сократить аппаратурную избыточность при реализации устройства. Устройство для деления позволяет обнаружить все ошибки вычислений в !

16670 матрице деления с восстановлением остатка, если ее неисправность ограничена неисправностью одной ячейки матрицы. В состав устройства входят вы" числительные ячейки 6, элементы HE 7, регистры 8,10 частного и остатка, компараторы 9,11 частного и остатка, 57 элемент ИЛИ 12, входы 1.1-1.п делителя, входы 2. (-m+1) — 2.п делимого, выходы 3.1-3..m частного, выходы 4.1—

4.п остатка, выход 5 контроля правильности вычислений, первый и второй управляющие входы 13,14 устройства.

2 ил.

Вычислительная яч йка 6 устройства описывается следующей системой уравнений,50 г = х(9 à (уС+ b), u =xg+ib+ h

Ь значение J1: ãè÷åñ.êîé величи55 ны на входе I 5; на входе на входе 1, ; на входг. "0; где хИзобретение относится к цифровой вычислительной технике и предназначено для использования в универсальных и специализированных вычислительных устройствах.

Цель изобретения — сокращение аппаратурных затрат при реализации в устройстве для деления оперативного обнаружения ошибок вычислений.

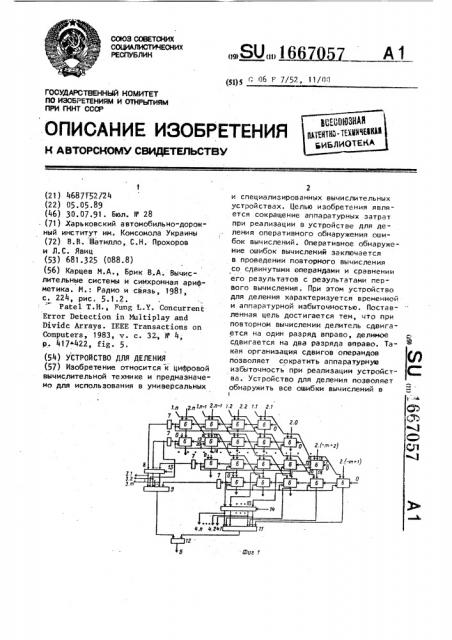

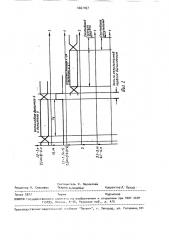

На фиг.1 изображена функционапьная схема устройства для деления; на фиг.2 — временная диаграмма работы устройства.

На фиг.1 обозначены входы l. 1.п делителя устройства, входы 2(-m+

+1)-2 делимого устройства, выходы

3.1-3.m частного устройства, выходы

4.1-4.п остатка устройства, выход 5 контроля правильности вычислений, вычислительная ячейка 6, элемент HF

7, регистр 8 частного, компаратор 9 частного регистр 10 остатка, компа35 ратор 11 остатка, элемент ИЛИ 12, первый и второй управляющие входы

13,14 устройства (тактовые входы регистров частного и остатка), соответственно первый, второй и третий информационные входы 15-17 вычислительной ячейки 6, первый й,второй выходы

18,19 вычислительной ячейки 6, управляющий вход 20 вычислительной ячейки 6.

z — на выходе 18;

u — на выходе 19; вычислительной ячейки 6 устройства для деления.

Устройство для деления позволяет обнаружить любую ошибку вычислений, если неисправность устройства ограни- . чивается неисправностью одной вычислительной ячейки либо одного элемента НЕ, генерирующего бит частного.

Устройство для деления работает следующим образом.

С целью обнаружения ошибок вычислений проводятся для вычисления. В первом вычислении делимое Х, делитель Y . В повторном вычислении делимое Х 2, делитель Y. 2 . Первое вычисление начинается с момента установки разрядов делителя на входах 1.21.п и разрядов делимого на входах

2,(-тп+3) -2.п, а на входы 2 (-в+1), 2i(-m+2), 1.1 в первом вычислении подаются сигналы "0".

Через время Т> переходного процесса в иатрице деления частное и остаток от первого вычисления устанавливаются соответственно на выходе частного матрицы и на первых информационных выходах вычислительных ячеек предпоследнего ряда и на соединенных с ними информационных входах регистров частного и остатка.

В момент времени Тя иа входы 13 и 14 устройства подаются импульсы записи, по которым производится запись в регистры частного и остатка соответственно частного и остатка от первого вычисления. По окончании записи матрица деления готова к повторному вычис-:. лению. Повторное вычисление начинается с момента установки разрядов делителя на входах. 1.1-1.(п-1) и разрядов делимого на входах 2,(-п+1)2,(n-2), а на входы 1.и. 2.n„2, (n-1) в повторном вычислении подаются сигналы "0".

1667 О

Через вреия Т переходного процесса в матрице деления частное и остаток от повторного вычисления устанав ливаются на выходах соответственно

5 частного и остатка матрицы деления и на соединенных с ними входах первых операндов компараторов частного и остатка, на входах вторых операндов которых установлены соответственно сдвинутые на один разряд вправо частное и на два разряда вправо остаток от первого вычисления.

Через время Т суимарной задержки сигналов в компараторе и элементе

ИЛИ на выходе 5 появляется сигнал, индицирующий правильную работу устройства, если результаты двух вычис лений совпали, либо ошибку вычислений, если результаты вычислений не совпали. формула и з о б р е т е н и я

Устройство для деления, содержащее матрицу пч(тп+1) вычислительных ячеек, (где и-1 — разРядность делителя, n + m — 2 — разрядность делимого, m — разрядность частного), m + 1 элементов НЕ, регистры частного и остатка, компараторы частного и остатка, причем первый информационный вход (i, j) é вычислительной ячейки (i = 2,...,п, ) = ?,.... m) соединен с первым выходом (i-1, j -1)-й вычислительной ячейки, первые информационные. входы (К,1) -х и (1, 1)-х вычислительных ячеек (где 1 = 1,..., 35

m+1) соединены с входаии соответствующих разрядов делимого устройства, второй информационный вход (i-1,1)-х и (п,1)-х вычислительных ячеек соединены с входами соответствующих разря"

40 дов делителя устройства, второй ин-,формационный вход (п,j) é вычислительной ячейки соединены с входом, логичес7

6 кого нуля устройства, третий информационный вход (i,1) -й вычислительной ячейки соединены с вторым выходом (i 1, 1)-й вычислительной ячейки, второй выход и-й вычислительной ячейки 1-й строки соединен с входом

1-го элемента НЕ и с управляющими входами всех вычислительных ячеек 1-й строки, управляющие входы (I 1)-х вычислительных ячеек соединены с входаии логического нуля устройства, выходы (j-1)-х элементов НЕ соединены с информационными входами регистра частного, выходы разрядов которого соединены с входаии разрядов первого операнда компаратора частного, входы разрядов второго операнда которого соединены с выходами j-х элементов НЕ, первые выходы (i-1, m)-х вычислительных ячеек соединены с информационными входами регистра остатка, вь ходы разрядов которого соединены

- входами разрядов первого операнда компаратора частного, входы разрядов второго операнда которого соединены с выходами с первой по (и-2) -й вычислительной ячейки (m+1)-й строки, о тл и ч а ю щ е е с я тем, что, с целью сокращения аппаратурных затрат, устройство содержит элемент ИЛИ, первый и второй входы которого соединены с выходаии компараторов частного и остатка соответственно, выход элеиента ИЛИ соединен с выходом контроля. правильности вычислений устройства, входы разрешения записи регистров частного и остатка соединены с первыи и вторым управляющими входами устройства, выходы разрядов регистра частного соединены с выходами частного устройства, выходы разрядов регистра остатка соединены с выходами остатка устройства..

1667057

Составитель Н. Маркелова

Техред Л.Олийнык

Редактор О. Спесивых

Корректор Л. ПатайЗаказ 3977 Тираж Подписное

8НИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, 3-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина,101 »„

« «

Ф»

1 I

° к с

ЧЭ

:Ъ фЮ «»» фМ» ««« ч