Устройство для деления

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть применено в быстродействующих вычислительных устройствах для деления чисел. Целью изобретения является сокращение количества оборудования устройства. Устройство содержит два регистра 1, 2 остатка, регистр 3 делителя, регистр 4 старших разрядов делителя, регистр 5 частного, сумматор 11 принудительного округления делителя, узел 12 вычисления обратной величины, три коммутатора 6 - 8, три вычитателя 14 - 16, сумматор 17, элемент И 18, блок 13 умножения, блок 19 управления и введенные два коммутатора 9, 10. 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

1667060 А1 (я)з G 06 F 7/52

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4725104/24 (22) 01.08.89 (46) 30.07.91. Бюл. ЬЬ 28 (72) А.Г, Батюков и А.А. Шостак (53) 681.325 (08&.8) (56) Авторское свидетельство СССР

¹ 11442299111100, кл. 6 06 F 7/52, 1986.

Авторское свидетельство СССР

М 1541598, кл. G 06 F 7/52, 1988. (54) УСТРОЙСТ80 ДЛЯ ДЕЛЕНИЯ (57) Изобретение относится к вычислительной технике и может быть применено в быстродействующих вычислительных устройствах для деления чисел.. Целью изобретения является сокращение количества оборудования устройства. Устройство содержит два регистра

1, 2 остатка, регистр 3 делителя, регистр 4 старших разрядов делителя, регистр 5 частного, сумматор 11 принудительного округления делителя, узел 12 вычисления обратной величины, три коммутатора 6-8, три вычитателя 14 — 16, сумматор 17, элемент

И 18, блок 13 умножения, блок 19 управления и введенные два коммутатора 9, 10. 3 ил.

1667060

Изобретение относится к области вычислительной техники и может быть применено в быстродействующих вычислительных устройствах для выполнения операции деления чисел.

Целью изобретения является сокращение количества оборудования устройства.

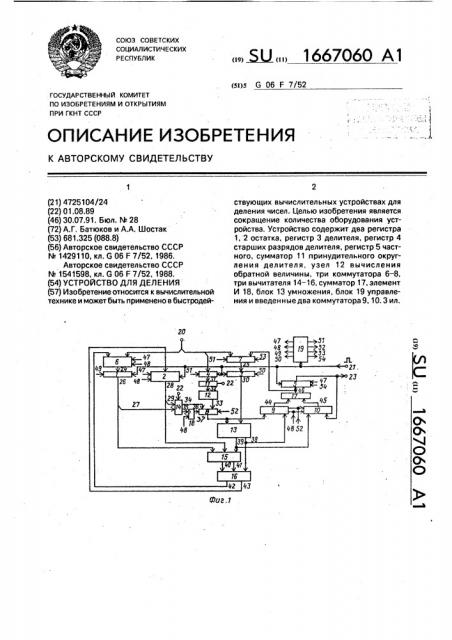

На фиг. 1 приведена структурная схема устройства; на фиг. 2 — функциональная схема блока управления, на фиг. 3 — микропрограмма работы устройства, Устройство для деления содержит (фиг. 1) первый и второй регистры 1, 2 остатка, регистр 3 делителя, регистр 4 старших разрядов делителя, регистр 5 частного, с первого по пятый коммутаторы 6-10; сумматор 11 принудительного округления делителя, узел 12 вычисления обратной величины, блок 13 умножения, с первого по третий вычитатели 14 — 16, сумматор 17, элемент И

18, блок 19 управления, вход 20 данных устройства, вход 21 синхронизации, вход 22 логической единицы устройства выход 23 частного, выходы 24 первого коммутатора 6, выходы 25 второго коммутатора 7, выходы

26 разрядов первого регистра 1 остатка, выходы 27 старших разрядов первого регистра

1 остатка, выходы 28 разрядов второго регистра 2 остатка, выходы 29 старших разрядов второго регистра 2 остатка, выходы 30 разрядов регистра делителя 3, выходы 31 регистра 4 старших разрядов делителя, выходы 32 сумматора 11 принудительного округления делителя, выходы ЗЗ узла 12 вычисления обратной величины, выходы 34 младших разрядов первого вычитателя 14, выход 35 старшего разряда первого вычитателя 14, выход 36 элемента И 18, выходы 37 третьего коммутатора 8, выходы 38 первой группы блока 13 умножения, выходы 39 второй группы блока 13 умножения, выходы 40 разности второго вычитателя 15, выходы 41 заема второго вычитателя 15, выходы 42 разности третьего вычитателя 16, выходы 43 заема третьего вычитателя 16, выходы 44 четвертого коммутатора 9, выходы 45 пятого коммутатора 10, выходы 46 сумматора 17, с первого по восьмой выходы 47-54 блока 19 управления.

БЛок управления (фиг, 2) содержит счетчик 55 и узел 56 памяти микрокоманд.

Рассмотрим функциональное назначение и реализацию основных узлов и блоков устройства для деления.

Формирование цифр частного и остатка на каждом такте работы устройства производится следующим образом. Пусть делимое Х и делитель Y есть положительные нормализованные двоичные дроби, т. е.

1/2< Х< 1 и 1/2 У< 1. В дальнейшем же (на следующих шагах деления), когда в роли делимого выступают промежуточные остатки, возможно нарушение нормализации делимого как влево, так и вправо. Пусть

5 Х1 значение старших (К+ 4) разрядов делимого (остатка), Y< — значение старших (К+ 3) разрядов делителя Y, Y< + 2 — значение

-(к+э принудительно округленных старших (К+ 3) разрядов делителя, С = 1/(Y t + 2iк ) )- эна10 чение обратной величины от Y1+ 2(+ ), Ci— значение старших (К+2) разрядов обратной величины С, (Х1 - р) — значение усеченного остатка, полученного приведением к однорядному коду старших разрядов двухрядно15 го кода остатка, где р = О, если в старшие разряды остатка Х при приведении его к однорядному коду поидет заем из младших разрядов и р -= 2(, если не придет, р—

-(к+ ) величина, на которую отличается значение

20 усеченного остатка, полученного приведением к однорядному коду старших разрядов двухрядного кода остатка, и принудительно уменьшенная на единицу младшего разряда, от значения усеченного остатка, получа25 емого приведением в однорядному коду всех разрядов двухрядного кода остатка. На подготовительном этапе деления формируется произведение делителя Y на значение старших (К+ 2) разрядов обратной величины, 30 т. е. W = Y . C>. При выполнении собственно деЛения следующий остаток вычисляется по формуле Х = Х - W . (X> — р). Промежуточное

1 значение частного Х" является суммой всех (X> — р), полученных на каждом такте собст35 венно деления и сдвинутых относительно друг друга на (К - 1) разрядов, при этом значение (X> - р), полученное на первом такте, образует старшие разряды промежуточного значения частного Х", После выполнения

40 собственно деления значение Х" умножается на значение С1. Старшие и разрядов этого произведения являются значением частного Z .

Для доказательства того, что частное 2

45 будет отличаться от частного Z = X/Y, полученного делением n — разрядных чисел, на величину, меньшую либо равную единице младшего разряда с весом 2"" ), достаточно доказать, что абсолютная погрешность 8

50 (разность между Z Х/Y и значением (Х1 - р)» хС1, полученным на первом такте собственно деления) не будет превышать 2"" 1и будет положительной, т, е.

Х . (и 1)

0 е= — -(Xi — р) С1(2

Пусть С2-С- С1, Х2=Х-Х1, У2=У- Y1— младшие части соответственно обратной величины, делимого и делителя, Maêñèìàë ьная погрешность будет, если р = 2 к + э

1667060 лимого Х с входа 20 данных устройства, когда на первом выходе 47 блока 19 управления формируется сигнал "1", либо значения поразрядных разностей двухрядного кода остатка Х, образованного на выходах 42 разности третьего вычитателя 16, когда на втором выходе 48 блока 19 управления формируется сигнал "1". С помощью второго коммутатора 7 осуществляется передача на

О информационные входы регистра 3 делителя либо делителя Y с входа 20 данных устройства, когда на пятом выходе 51 блока 19 управления формиоуется сигнал "1", либо значения Х" или W, образованного на выходах 46 сумматора 17, когда на седьмом выходе 53 блока 19 управления формируется сигнал "1". С помощью третьего коммутатора 8 осуществляется передача на его выходы 37 либо значения С> старших (К + 2) разрядов обратной величины от принудительно округленного значения старших (К+ 3) разрядов делителя, образованного на выходах 33 узла 12 вычисления обратной величины, когда на шестом выходе 52 блока

19 управления формируется сигнал "1", либо значения (X> — р) однорядного кода (К+ 4) старших разрядов остатка, поступающего с выходов 34 младших разрядов второго вычитателя 14, когда на выходе 36 элемента И

18 формируется сигнал "1". С помощью четвертого коммутатора 9 осуществляется передача на входы первого слагаемого сумматора 17 либо (К+ 4) разрядов промежуточного значения частного (X t - р), получаемых в каждом такте собственно деления и поступающих на входы младших разрядов информационных входов второй группы четвертого коммутатора 9 с выходов 37 третьего коммутатора 8 (на входы старших разрядов информационных вх цов второй группы коммутатора 9 подают "О"), когда на втором выходе 48 блока 19 управления формируется сигнал "1", либо значения первого ряда двухрядного кода произведения W или

Z, сформированного на выходах 38 блока 13 умножения и поступающего на информационные входы первой группы четвертого коммутатора 9, когда на шестом выходе 52 блока 19 управления формируется сигнал

"1". С помощью пятого коммутатора 10 осуществляется передача на входы второгослагаемого сумматора 17 либо значения второго ряда двухрядного кода произведения ЧЧ или Z, сформированного на выходах

39 блока 13 умножения и поступающего на информационные входы первой группы пятого коммутатора 10, когда на шестом выходе 52 блока 19 управления формируется сигнал "1", либо промежуточного значения частного Х", поступающего с выходов региС =2 +, Хг=2 + -2", Yz=0, Х=

=2Y-2", При этих условиях неравенство для я можно доказать, Первый регистр 1 остатка имеет два 5 разряда слева от запятой, остальные справа. В исходном состоянии в этом регистре хранится и — разрядный двоичный код делимого Х без знака, а в процессе деления,в каждом такте в него записывается значение 1 поразрядных разностей двухрядного кода очередного остатка, сформированное на выходах 42 третьего вычитателя 16. Второй регистр 2 остатка имеет два разряда слева от запятой, остальные справа от запятой. В 15 исходном состоянии этот регистр обнулен, а в процессе деления в него в каждом такте записывается значение .поразрядных заемов двухрядного кода очередного остатка, сформированное на выходах 43 третьего 20 вычитателя 16. Регистр 3 делителя в исходном состоянии хранит и — разрядный двоичный код делителя Y без знака, а к началу собственно деления в него записывается произведение W делителя Y на (К + 2) стар- 25 ших разрядов обратной величины С1, вычисленной по значению Y + 2 (+ .

Произведение И/ поступает в однорядном коде с выходов 46 сумматора 17. На последнем такте собственно деления в ре- 30 гистр 3 делителя записывается m (К - 1) + 5 разрядов промежуточного значения частного Х (m — число тактов собственно деления), образованного на выходах 46 сумматора 17.

Регистр 4 старших разрядов делителя (К+ 3) 35 разрядный и предназначен для хранения У1 (старших (К + 3) разрядов делителя Y без знака). Регистр 5 частного в исходном состо-. янии обнулен, а в процессе деления в него на каждом такте записывается накапливае- 40 мое значение частного Х, поступающее с выходов 46 сумматора 17. На последнем, такте работы устройства в регистр 5 записывается частное 2, которое поступает на выход

23 частного устройства. Предполагается, что 45 регистры 1 — 5 реализованы на основе двухтактных синхронных DV — триггеров. Запись информации в регистры производится по синхроимпульсу при наличии разрешающего потенциала на их V-входах. Кроме того, 50 второй регистр 2 остатка и регистр 5 частного вначале деления обнуляются путем подачи синхроимпульса с входа 21 синхронизации устройства на их синхровходы и разрешающего потенциала с первого выхо- 55 да 47 блока управления на их входы разрешения установки в нуль.

С помощью первого коммутатора 6 осу.ществляется передача на информационные . входы первого регистра 1 остатка либо де1667060 стра 5 частного на информационные входы второй группы пятого коммутатора 10 со сдвигом на (К вЂ” 1) разрядов в сторону старших разрядов (на входы (К - 1) младших разрядов информационных входов второй группы коммутатора 10 подаются и0", когда на втором выходе 48 блока 19 управления формируется сигнал н1". Коммутаторы 6 — 10 могут быть реализованы на элементах 2И—

2ИЛИ, Сумматор 11 принудительного округления делителя является комбинационной схемой. В нем осуществляется принудительное округление значения У1 старших (К+ 2) разрядов делителя путем прибавления единицы в его младший разряд, поступающей на вход переноса сумматора 11 принудлтельного округления делителя через вход 22 логической единицы устройства. На выходах 32 сумматора 11 образуется значение Y + 2

Узел 12 вычисления обратной величины производит вычисление значения С1 старших (К ч 21 разрядов обратнои величины С =

=1/(У1+ 2 . На выходах 33 узла 12 вычис-, +з) ления обратной величины формируется значение С старших (К+ 2) разрядов обратной величины С принудительно округленного усеченного делителя, В данном случае предполагается его реализация совместно с сумматором 11 принудительного округления делителя на ПЗУ. Ниже приведен фрагмент таблицы истинности для такой реализации при значении К = 4.

Первый вычитатель 14 комбинационного типа, Он осуществляет преобразование (К+ 5) старших разрядов двухрядного кода остатка, хранящегося в регистрах 1, 2 остатка, в однорядный код (два разряда слева от запятой и (К+ 3) разряда справа от запятой).

При этом в первом вычитателе 14 осуществляется принудительное уменьшение значения усеченного остатка на единицу младшего разряда, поступающего на вход заема первого вычитателя 14 через вход 22 логической единицы устройства, в результате чего формируется значение(Х вЂ” р). На выходах 34 младших . разрядов первого вычитателя 14 образуется однорядный код (К + 4) старших разрядов остатка (один разряд слева от запятой и (К+ ф3) разряда справа от запятой), а на выходе

35 старшего разряда первого вычитателя 14 образуется старший разряд остатка. Так как в устройстве при формировании частного используется значение старших разрядов ос" татка, полученное при приведении на первом вычитателе 14 к однорядному коду старших разрядов двухрядного кода остатка и принудительно уменьшенное на единицу младшего разряда, то становится возможным образование неправильного значения частного. Так, если значение старших разрядов приведенного к однорядному коду полноразрядного остатка равно нулю, то при формировании однорядного кода старших разрядов остатки на выходах 34 младших разрядов первого вычитателя 14 возможно получение значения, меньшего чем нуль на единицу младшего разряда, т. е.значения 1, 111...1. Но в этом случае на к+4

10 выходе 35 старшего разряда первого вычитателя 14 формируется единица. Если же значение старших разрядов приведенного полноразрядного остатка не равно нулю, на выходе 35 старшего разряда формируется

15 нуль. Для исключения возможности получения в первом случае неверного значения частного в устройстве предусмотрена блокировка (формирование значения старших разрядов остатка Х вЂ” р, равного нулю). Это

20 производится путем подачи на инверсный вход элемента И 18 единичного сигнала с выхода 35 первого вычитателя 14. В этом случае на выходе 36 элемента И 18 независимо от значения сигнала на его прямом

25 входе формируется сигнал и0", который запрещает прохождение значения Х1 — р с информационных входов второй группы третьего коммутатора 8 на его выходы 37 (формируется значение 0 00...0).В случае.

30 к когда на инверсный вход элемента И 18 подается сигнал н0", а на прямой вход подается сигнал и1н с второго выхода 48 блока 19 управления, значение старших разрядов ос35 татка X> — р с информационных входов второй группы третьего коммутатора 8 поступает на его выходы 37.

Блок 13 умножения и роизводит умножение содержимого регистра 3 делителя (на

40 подготовительном этапе — делителя У, âo вре- мя всех шагов собственно деления — произведения И/, а на последнем шаге работы устройства — промежуточного (значения частного Хн) на значение величины, сфармиро45 ванной на выходах 37 третьего коммутатора

8 (соответственно на С1, X>, -p>, С1). На его выходах 38, 39 первой и второй rpynn соответственно образуется произведение в двухрядном коде(соответственно W= Y C>, 50 (X>-р) W,Z =X С1).

С помощью второго и третьего вычитателей 15, 16 вычисляется очередной остаток по двухрядному коду предыдущего остатка

Х, поступающему на входы уменьшенного и

55 вычитаемого первой группы вычитателя 15 с выходов 26, 28 первого и второго регистров

1, 2 остатка соответственно и по двухрядному коду произведения W (Х1- р), поступающему на входы вычитаемого первой группы

1667060

10 третьего вычитателя 16 с выходов 38 первой группы блока 13 умножения и на входы вычитаемого второй группы второго вычитателя 15 с выходов 39 второй группы блока 13 умножения. Второй и третий вычитатели 15, 5

16 могут быть построены с использованием одноразрядных двоичных вычитателей и являются вычитателями без распространения заема. На выходах 42, 43 третьего вычитателя 16 очередной остаток Х = Х - W (Х1- р) 10 формируется в двухрядном коде в виде разности и заема. Вычитатели 15, 16 могут быть также реализованы на основе одноразрядных двоичных сумматоров с применением правил обработки информации в обратном 15 или дополнительном кодах. Для этого необходимо информацию, поступающую на входы вычитателей 15, 16 с выходов 38, 39 блока

13 умножения, проинвертировать и осуществить прибавление единиц в их младшие 20 разряды (при использовании дополнительного кода). В этом случае на выходах 42, 43, третьего вычитателя 16 очередной остаток образуется в двухрядном коде в виде суммы и переноса. Очередной остаток с выходов 42, 43 25 третьего вычитателя поступает со сдвигом на (К-1) разряд в сторону старших разрядов на информационные входы второй группы первого коммутатора 6 и на информационные входы второго регистра 2 остатка. 30

Сумматор 17 предназначен для выполнения операции суммирования с распространением переноса информации, поступающей с выходов 44, 45 четвертого 9 и пятого 10 комму(атаров, Он участвует в процессе накопле- 35 ния промежуточного значения частного, когда на первые управляющие входы четвертого и пятого коммутаторов 9, 10 подается сигнал "1" с выхода 48 блока 19 управления.

Это производится путем прибавления к про- 40 межуточному значению частного, храняще- муся в регистре 5 частного и сдвинутому на (К - 1) разрядов влево (в сторону старших разрядов), (К + 4) разрядов частного, сформированных на выходах 37 третьего комму- 45 татора 8. Сумматор 17 также участвует в процессе формирования однорядного кода произведения, полученного на выходах 38, 39 блока 13 в двухрядном коде, когда на вторые управляющие входы четвертого и пятого 50 коммутаторов 9, 10 подается сигнал "1" с выхода 52 блока 19 управления.

Блок 19 управления координирует работу узлов и блоков устройства при выполнении в нем операции деления чисел. Как и в 55 устройстве-прототипе он может быть реализован самыми различными методами и средствами. На фиг. 2 в качестве примера приведена реализация блока 19 на основе счетчика 55 узла 56 памяти микрокоманд.

Счетчик 55 накапливающего типа и предназначен для естественной адресации микрокоманд, Вход счета счетчика соединен с входом

21 синхронизации устройства. В качестве памяти 56 микрокоманд может быть применена быстродействующая постоянная память емкои — 1 стью (m + 3) 8, где m = — число тактов собственно деления Х ) — ближайшее целое, большее или равное Х). В самом начале работы устройства счетчик 55 устанавливается в некоторое исходное состояние, например в нуль (на фиг. 2 цепь установки счетчика 55 в исходное состояние не показана). Микропрограмма работы устройства представлена на фиг. 3.

Устройство для деления работает следующим образом.

Пусть на вход 20 данных устройства уже поступил и — разрядный двоичный код делителя Y (здесь предполагается, что делимое

Х и делитель Y правильные нормализованные положительные дроби), и счетчик 55 блока 19 управления установлен в исходное нулевое состояние, По содержимому счетчика 55, которое служит адресом обращения к памяти 56 микрокоманд, из памяти 56 микрокоманд считывается микрокоманда "1", которой соответствуют управляющие сигналы У50, У51 (фиг. 3), В результате этого соответственно на четвертом и пятом выходах 50, .

51 блока 19 управления устанавливаются уровни "1". Под действием этих управляющих сигналов второй коммутатор 7 пропускает на информационные входы регистра 3 делителя делитель Y с входа 20 данных устройства, а регистр 3 делителя и регистр 4 старших разрядов делителя подготовлены к приему информации, так как на их входах разрешения записи присутствуют потенциалы "1". С приходом первого импульса на вход синхронизации устройства производится запись делителя Y в регистр 3 делителя и старших разрядов делителя У1 в регистр 4 старших разрядов делителя, а также установка счетчика 55 блока 19 управления в состояние "1".

Во втором такте работы устройства из узла 56 памяти микрокоманд считывается микрокоманда "2", которой соответствуют управляющие сигналы У47, У49, У50, У52, У53. В результате этого соответственно на первом, третьем, четвертом, шестом и седьмом выходах 47, 49, 50, 52, 53 блока 19 управления устанавливаются уровни "1". Под действием этих управляющих сигналов первый коммутатор 6 пропускает на информационные входы первого регистра 1 остатка делимое Х с входа 20 данных устройства, первый регистр 1 остатка подготовлен к приему информации, третий коммутатор 8 пропускает на входы

1667060 первой группы блока 13 умножения значение старших разрядов обратной величины

С1, сформированное на выходах 33 узла 12 вычисления обратной величины. На выходах

38, 39 первой и второй групп блока 13 умножения формируется произведение W = Y С1 в двухрядном коде, которое поступает на информационные входы первой группы четвертого и пятого коммутаторов 9, 10, настроенных на пропуск этой информации на

; выходы 44, 45 управляющим сигналом с выхо, да 52 блока 19 управления, Сумматор 17 при водит к однорядному коду это произведение.

Под действием управляющего сигнала с выхо да 53 блока 19 управления второй коммутатор

7 пропускает на информационные входы реги-! стра 3 делителя значение произведения W в

, однорядном коде с выходов 46 сумматора 17.

Под действием управляющего сигнала с выхода 50 блока 19 управления регистр 3 дели теля подготовлен к приему информации. (Кроме этого, второй регистр 2 остатка и ре, гистр 5 частного настроены на обнуление, С приходом второго импульса на вход 21 син( хронизации устройства производится за,пись делимого Х и произведения W в регистры соответственно 1, 3, а также обнуление регистров 2, 5 и установка счетчика 55 блока 19 управления в состояние "2". На этом заканчивается подготовительный этап работы устройства, включающий два такта, и начинается собственно деление, в процес се которого в течение m тактов формируется (m(K — 1)+ 5)двоичных цифр промежуточного значения частного X".

В первом такте собственно деления из, памяти 56 микрокоманд считывается микро команда "3", которой соответствуют управляющие сигналы У48, У49, У54, и соответственно на втором, третьем и восьмом выходах 48, 49, 54 блока 19 управления устанавливаются уровни "1", Под действием этих управляющих сигналов третий коммутатор 8 пропускает на свои выходы 37 значение {X1 — р) с выходов

34 первого вычитателя 14, если на выходе 35 старшего разряда первого вычитателя 14 сформирован сигнал "0", и нуль в противном случае, четвертый и пятый коммутаторы 9, 10 пропускают на входы сумматора 17 соответственно значение (Xl - р) с выходов 37 третьего коммутатора 8 и накапливаемое промежуточное значение частного Х, подаваемое на информационные входы второй группы пятого коммутатора 10 со сдвигом на (К - 1) разряд влево (в сторону старших разрядов). Регистр 5 частного настроен на прием информации, поступающей с выходов 46 сумматора 17. Кроме того, на выходах

38, 39 первой и второй групп блока 13 умножения формируется произведение W (Х1—

-р) в двухрядном коде. С помощью вычитателей 15, 16 на выходах 42, 43 разности и заема вычитателя 16 формируется значение

5 Х-W (X) — р) в двухрядном коде, которое в дальнейшем служит остатком и подается на информационные входы первого регистра 1 остатка через коммутатор 6 и на информационные входы второго регистра остатка со

10 сдвигом на (К - 1) разряд влево (в сторону старших разрядов). Первый и второй регистры 1, 2 остатка настроены на прием информации. С приходом третьего импульса на вход 21 синхронизации устройства в первый

15 и второй регистры 1, 2 остатка записывается двухрядный код следующего остатка, в регистре 5 частного накапливается промежуточное значение частного, а счетчик 55 блока 19 управления устанавливается в состояние "3".

20 Аналогичным образом устройство работает и в других тактах собственно деления.

Отметим только, что на последнем такте собственно деления (микрокоманда m+ 2 на фиг. 3) накопленное промежуточное значе25 ние частного Х с выходов 46 сумматора 17 поступает на информационные входы регистра 3 делителя через второй коммутатор 7.

Регистр 3 делителя под действием управляющего сигнала с выхода 50 блока 19 управ30 ления подготовлен к приему информации. С приходом импульса с входа 21 синхронизации устройства промежуточное значение частного записывается в регистр 3 делителя, а счетчик 55 блока 19 управления устанавли35 вается в состояние "m + 2".

На последнем (m + 3) такте деления из узла 56 памяти микрокоманд считывается микрокомэнда m+3, которой соответствуют управляющие сигналы У52, У54 и соответст40 венно на шестом и восьмом выходах 52, 54 блока 19 управления устанавливаются уровни "1". Под действием этих управляющих сигналов третий коммутатор 8. пропускает на входы первой группы блока 13 умноже45 ния значение старших разрядов обратной величины С1, Коммутаторы 9, 10 пропускают на входы сумматора 17 двухрядный код произведения Х" С1 с выходов 38, 39 первой и второй групп блока 13 умножения. Сумматор

50 17 формирует однорядный код произведения

X С1, поступающий на информационные входы регистра 5 частного, который подготовлен к приему информации единичным сигналом на выходе 54 блока 19, С приходом импульса

55 нэ вход 21 синхронизации устройства произведение X" . С записывается в регистр 5 частного, п старших разрядов его являются разрядами частного Z и поступают на выход

23 частного устройства.

16

1667060

47 48 4У Я 51 5l Я 54. юг. 5

Составитель Н. Маркелова

Редактор О. Спесивых Техред М.Моргентал Корректор О, Кравцова

Заказ 2524 Тираж 396 Подписное

ВНИИПИ Государственного. комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Г1роизводственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

Значение разрядов регистра старших разрядов делителя на адресных входах ПЗУ

0, 1000000

О, 1000001

О, 1000010

0 1111110

О, 1111111

Значение старших разрядов обратной величины

1, 1111

1, 11110

1, 11101

1, 00000

1, 00000

1667060

Формула изобретения входами уменьшаемого третьего вычитателя, входы вычитаемого первой группы которого соедиУстройство для деления, содержащее нены с выходами первой группы блока умдва регистра остатка, регистр делителя, ре- ножения, вход синхронизации устройства гистр частного, регистр старших разрядов 5 соединен с синхровходами первого и второделителя, сумматор принудительного округ- го регистров остатка, регистра делителя, реления делителя, узел вычисления обратной гистра старших разрядов делителя, величины, элемент И, три коммутатора, три регистра частного и блока управления, первычитателя, сумматор, блок умножения .и вый выход блока управления соединен с . блок управления, причем информационные 10 первым управляющим входом первого комвходы регистра старших разрядов делителя мутатора и входами установки в "0" второго и информационные входы первой группы регистра остатка и регистра частного, втопервого и второго коммутаторов соединены рой выход блока управления соединен с с входом данных устройства, выходы первого вторым управляющим входом первого комкоммутатора соединены с информационны- 15 мутатора, с прямым входом элемента И и ми входами первого регистра остатка,выхо- входом разрешения записи второго репистра ды старших разрядов которого соединены с остатка, третий и четвертый выходы блока входами уменьшаемого.первого вычитате- управления соединены с входами разрешеля, входы вычитаемого которого соединены; ния записи первого регистра остатка и регис выходами старших разрядов второго реги- 20 стра делителя соответственно, пятый выход стра остатка, вход заема первого вычитате- блока управления соединен с входом разреля соединен с входом логической единицы . шения записи регистра старших разрядов устройства и входом переноса. сумматора делителя и первым управляющим входом и ринудительного округления, информаци- второго коммутатора, шестой выход блока онные входы которого соединены с выхо- 25 управления соединен с вторым управляюдом регистра старших разрядов делителя, щим входом третьего коммутатора, о т л ивыходы сумматора принудительного Округ- ч а ю щ е е с я тем, что, с целью сокращения ления соединены с входами узла вычисле- количества оборудования, устройство сония обратной величины, выходы которого держит четвертый и пятый коммутаторы, присоединены с информационными входами 30 чем выходы первой группы блока умножения первой группы третьего коммутатора, инфор- соединены с информационными входами мационныевходывторойгруппыкоторогосо- первой группы четвертого коммутатора, инединены с выходами младших разрядов формационные входы второй группы котопервого вычитателя, выход старшего разря- рого соединены с входами первой группы, да которого соединен с инверсным входом 35 блока умножения, выходы второй группы элемента 1, выход которого соединен с пер- которого соединены с входами первой групвым управляющим входом третьего комму- пы пятого коммутатора и с входами вычитататора, выходы которого соединены с емого второй группы второго вычитателя, входами первой группы блока умножения, выходы заема которого соединеныс входами входы второй группы которого соединены с 40 вычитаемого второй группы третьего вычитавыходами регистра делителя, информаци- теля, выходы разрядов регистра частного соонные входы которого соединены с выхода- единены с выходами частного устройства и ми второго коммутатора, информационные информационными входами второй группы входы второй группы которого соединены с пятого коммутатора. выходы четвертого и выходами сумматора и с информационными 45 пятого коммутаторов соединены с входами входами регистра частного, выходы разрядов первой и второй групп сумматора соответпервого регистра остатка соединены с вхо- ственно, второй выход блока управления содами уменьшаемого второго вычитателя, единен с первыми управляющими входамй входы вычитаемого первой группы которого четвертого и пятого коммутаторов, вторые соединены с выходами разрядов второго ре- 50 управляющие входы которых соединены с гистраостатка,информационныевхюдыкото- шестым выходом блока управления, седьрого соединены с выходами заема третьего мой выход которого соединен с вторым упвычитателя, выходы разности которого сое- равляющим входом второго коммутатора, динены с информационными входами вто- восьмой выход блока управления соединен рой группы первого коммутатора, выходы 55 с входом разрешения записи регистра частразности второго вычитателя.соединены с ного.