Вероятностный интегратор

Иллюстрации

Показать всеРеферат

Изобретение относится к измерительной технике. Цель изобретения - повышение точности. Изобретение позволяет повысить точность измерения математического ожидания методом статистических испытаний. При этом повышение точности достигается адаптацией диапазона вспомогательного случайного процесса к математическому ожиданию измеряемого случайного сигнала с центрированием этого процесса на величину текущей оценки математического ожидания измеряемого случайного сигнала параллельно с использованием знакового метода оценивания среднего в зоне нечувствительности метода статистических испытаний. Интегратор содержит блок сравнения 1, блоки усреднения 2, 4, блок 3 масштабирования, блок умножения 5, блок 6 вычисления диапазона вспомогательного сигнала, аналоговые блоки 8, 9 памяти, блоки 10, 12 сложения, блок 11 вычитания, ключ 13, блок 14 знаковой оценки среднего, генератор 15 тактовых импульсов. 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (s1)s G 06 F 7/70

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

0 (;Ь

С)

Ос

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4749363/24 (22) 23.06.89 (46) 30.07.91. Бюл. hb 28 (75) О.П. Танцоров и Н.Г. Черногуз (53) 681.3 (088.8) (56) Авторское свидетельство СССР

М 1328814, кл. G 06 F 7/70, 1986. (54) ВЕРОЯТНОСТНЫЙ ИНТЕГРАТОР (57) Изобретение относится к области измерительной техники. Цель изобретения — повышение точности. Изобретение позволяет повысить точность измерения математического ожидания методом статистических испытаний, При этом повышение точности достигается адаптацией диапазона вспомо1 (19) (11) гательного случайного процесса к математическому ожиданию измеряемого случайного сигнала с центрированием этого процесса на величину текущей оценки математического ожидания измеряемого случайного сигнала параллельно с использованием знакового метода оценивания среднего в зоне нечувствительности метода статистических испытаний.

Интегратор содержит блок сравнения 1, блоки усреднения 2, 4, блок 3 масштабирования, блок умножения 5, блок 6 вычисления диапазона вспомогательного сигнала, аналоговые блоки 8, 9 памяти, блоки 10, 12 сложения, блок 11 вычитания, ключ 13, блок

14 знаковой оценки среднего, генератор 15 тактовых импульсов. 3 ил.

1667064

Изобретение относится к области измерений, контроля и управления и может найти применение в информационно — измерительной технике, радиотехнике и приборостроении.

Цель изобретения — повышение точности

Принцип действия интегратора заключается в следующем. Заданному отклонению д середины диапазона h генерируемого вспомогательного равномерно распределенного процесса, от математического ожидания измеряемого случайного сигнала, соответствует оптимальное значение Л == pi при котором погрешность стохастического интегрирования (усреднения) минимальна, Поэтому, используя центрирование вспомогательного процесса по текущей оценке математического ожидания измеряемого случайного сигнала, можно повысить точность стохастического интегрирования. Однако по мере уменьшения д соответственно будет уменьшаться Л = +pi и при некотором

Л = 6ppi близком к нулю процесс интегрирования практически остановится. Чтобы обес. печить интегрирование при малых значениях

Л,когда текущие наблюдения не попадают в пределы Л = hopi необходим учет этих наблюдений с помощью метода, не связанного с шириной диапазона Л (например, метода знакового интегрирования). С этой целью в интеграторе одновременно реализованы оба метода усреднения: при попадании текущих значений измеряемого процесса в пределы диапазона они обрабатываются методом статистических испытаний, а при попадании вне предела указанного диапазона — знаковым методом; в качестве результирующего значения используется взвешенная сумма обоих типов оценок.

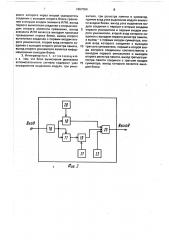

Эмпирическая зависимость между h u отклонением д получена экспериментальным путем и описывается регрессионным уравнением hopi =0,27 +5,6IBl — 1,54!д1, На фиг, 1 приведена структурная схема интегратора; на фиг. 2 — функциональная схема блока вычисления диапазона вспомогательного сигнала; на фиг. 3 — функциональная схема блока знаковой оценки среднего.

Интегратор содержит (фиг, 1) блок 1 сравнения, блок 2 усреднения, блок 3 масштабирования, блок 4 усреднения, блок 5 умножения, блок 6 вычисления диапазона вспомогательного сигнала, генератор 7 шума, аналоговые блоки 8-9 памяти, блок 10 сложения, блок 11 вычитания, блок 12 сложения, ключ

13, блок 14 знаковой оценки среднего, генератор 15 тактовых импульсов.

Блок 6 (фиг. 2) содержит узел 16 определения абсолютного значения, умножители щего устройства 1 поступает на вход блока

2 усреднения,. работающего по принципу усредняющего звена с постоянной времени х1, где т1 — время скользящего интервала

35 усреднения измеряемого сигнала при условии, что ®pi на этом интервале остается практически неизменным.

Значение с выхода блока 2 усреднения поступает на первый вход блока 3 масштаби40 рования, осуществляющего масштабирование усредненного на интервале z1 значения измеряемого сигнала в соответствии с

Л = pi,выходное значение которого поступает на второй вход блока 3 масштабиро45 вания с выхода блока 8. Напряжение с выхода блока 3 масштабирования равно

0выхз = (ОвхзИвых2щвх - 0,5) hopi, Напряжение с выхода блока 4 усреднения поступает на вход блока 11 вычитания и на вход блока

9. На другой вход блока 11 вычитания поступает напряжение с выхода блока 9, равное значению текущей оценки Si-1 на предыдущем участке интервала скользящего усред55 нения ц, Напряжение с выхода блока 11 вычитания поступает на вход блока 6 вычитания.

Блок 6 работает, непосредственно реализуя вычисления в соответствии с указанным.выражением.

17 — 19, регистры 20-22 памяти, сумматор 23, блок 14 (фиг. 3) содержит умножители 24, 25, вычитатель 26, сумматор 27, элементы 28, 29 сравнения, элемент ИЛИ 30, усреднители

31, 32, вычитатель 33, регистры 34, 35 памяти

Интегратор работает следующим образом, Измеряемый сигнал поступает одновременно на вход ключа 13 и на вход блока 14.

В случае, когда измеряемый сигнал ri в зоне диапазона Л = ®pi а логический сигнал Р с выхода блока 14 отсутствует, тем самым разрешая роботу метода статистических испытаний и запрещая знаковый метод, 1 проходит через ключ 13 на вход блока 1 сравнения. При этом на другой вход блока 1 с выхода блока 10 сложения поступает равномерно распределенный в диапазоне

Л= Рорс/2+ Sa - hopi/2+ $ ) центрированный на величину Si случайный у сигнал. На другой вход блока 10 сложения поступает напряжение St с выхода блока 9, который хранит текущую оценку математического ожидания измеряемого сигнала. Блок 1 выполняет следующую логическую операцию

0; ri pc

x=

1; i> с.

Логический сигнал g с выхода сравниваю1667064. Случай запрещения метода статистиче- аналогового блока памяти и выходом второских испытаний и разрешения знакового ме- го блока усреднения, являющимся выходом тоданаступаетприусловии )гс-Я I> App< /2. интегратора, выход генератора тактовых

Приэтомнавходпервыйблока1черезключ импульсов соединен с синхровходами пер13 под управлением сигнала, вырабатывае- 5 ваго и второго аналоговых блоков памяти, могосвыходаблока14,поступаетнапряжение вход обнуления второго аналогового блока с выхода блока 9, равное величине центриро- памяти и вход задания начального значения вания Яь первого аналогового блока памяти являютВ блоке 14 элемент 28 сравнения вы- ся соответственно входами обнуления и заполняет следующую логическую операцию 10 дания начального значения диапазона

1; -Лорс /2 + St >ll/T вспомогательного сигнала интегратора, выL1= ход блока вычитания соединен с входом

0; Л.„/г+ Я, В/ блока вычисления диапазона вспомогательЭлемент 29 сравнения выполняет сле- ного сигнала, выход которого соединен с дующую логическую операцию 15 информационным входом первого аналого1; -Apt /2 + St > rt вого блока памяти, отличающийся

L2= тем, что, с целью повышения точности, в

0; hopt /2 + St г него дополнительно введены второй блок

Напряжение с выхода умножителя 25, сложениЯ, блок знаковой оценки сРеднего и равное

20 ключ, причем первый информационный

Лз 1" 1" вход ключа соединен с информационным

0вых25 3 -1 1 — — 3 L2CI4

5 <1 и входом блока знаковой оценки среднего и

О О является информационным входом интеграявляется выходны напряжением блока 14, тора, вход задания порога и информационкоторое поступает на выход блока 14 и с 25 ный выход блока знаковой оценки среднего него поступает на вход блока 12 сложения. соединены соответственно с выходом перВ момент включения в блок 8 заносится вого аналогового блока памяти и первым начальноезначение(возможномаксимальное) входом второго блока сложения, второй

Л,аблок9обнуляется. Синхронновключается вход и выход которого соединены соответи генератор 15 тактовых импульсов, который 30 ственно с выходом блока масштабирования выдаетстрогосинхронизированнуюрегулярную и входом второго блока усреднения, выход последовательность импульсов с периодом по- второго аналогового блока памяти соединен вторения, равным интервалу скользящего ус- с вторым информационным входом ключа и реднения ту поступающих на синхровходы входом опорного сигнала блока знаковой блоков 8 и 9. 35 оценки среднего, выход признака превышения порога которого соединен с управляюФормула изобретения щим входом ключа, выход которого

1. Вероятностный интегратор,содержа- соединен с вторым входом блока сравнещий блок сравнения, два блока усреднения, ния, блок масштабирования, два аналоговых 40 2, Интегратор по и. 1, о т л и ч а ю щ и йблока памяти, первый блок сложения, блок с я тем, что блок знаковой оценки среднего вычитания, генератор шума, генератор так- содержит два умножителя, два регистра патовых импульсов, блок умножения, блок вы- мяти, сумматор, два вычитателя, два элечисления диапазона вспомогательного мента сравнения, два усреднителя и сигнала, причем выход "Больше" блока 45 элемент ИЛИ, причем первые входы первосравнения через первый блок усреднения го и второго элементов сравнения подклюсоединен с информационным входом блока чены к информационному входу блока, вход масштабирования, входзадания коэффици- уменьшаемого первого вычитателя и.перентамасштабированиякоторогосоединенс вый вход сумматора подключены к входу выходом первого аналоговогоблока памяти 50 опорного сигнала блока, первый вход пери первым входом первого блока умножения, вого умножителя является входом задания второй вход и выход которого соответствен- порога блока, второй вход умножителя соено соединены с выходом генератора шума и динен с выходом первого регистра памяти, первым входом блока сложения, выход ко- . а выход — с входом вычитаемого первого торого соединен с первым входом блока 55 вычитателяи вторымвходомсумматора,высравнения, а второй вход блока сложения ход которого соединен с вторым входом соединен с выходом второго аналогового первогоэлементасравнения, выходкотороблока памяти и входом вычитаемого блока госоединенс первым входомэлемента ИЛИ вычитания, вход уменьшаемого которого со- и через первый усреднитель с входом вычиединен с информационным входом второго таемого второго вычитателя, вход уменьша1667064 емого которого через второй усреднитель соединен с выходом второго блока сравнения и вторым входом элемента ИЛИ, выход первого вычитателя соединен с вторым входом второго элемента сравнения, выход, элемента ИЛИ является выхОдом признака превышения порога блока, выход второго вычитателя соединен с первым входом второго умножителя, второй вход которого со, единен с выходом второго регистра памяти, выход второго умножителя является информационным выходом блока.

3. Интегратор по и. 1, о т л и ч а ю щ и йс я тем, что блок вычисления диапазона вспомогательного сигнала содержит узел определения выделения модуля, три умножителя, три регистра памяти и сумматор, причем вход узла выделения модуля является входом блока, выход узла выделения модуля соединен с первым и вторым входами

5 первого умножителя и первым входом второго умножителя, второй вход которого соединен с выходом первого регистра памяти, а выход — с первым входом сумматора, второй вход которого соединен с выходом

10 третьего умножителя, первый и второй входы которого соединены соответственно с выходом первого умножителя и выходом второго регистра памяти, выход третьего регистра памяти соединен с третьим входом

15 сумматора, выход которого является выходом блока.

1667064

Составитель В. Орлов

Редактор О. Спесивых Техред M.Ìîðãåíòàë Корректор О. Кравцова

Заказ 2524 Тираж 395 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж 35, Раушская наб„4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101