Устройство для масштабирования чисел

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и предназначено для использования в быстродействующих цифровых устройствах, функционирующих в непозиционных системах счисления и реализующих различные немодульные операции, такие как деление, умножение дробей, масштабирование, перевод чисел в двоичную систему счисления. Целью изобретения является расширение области применения за счет выполнения операции масштабирования в модулярном коде. Устройство содержит блок элементов задержки, блок вычисления интервального индекса числа, элемент задержки, первый и второй регистры сдвига, регистр модулярного кода числа, регистр интервального индекса, первый и второй блоки мультиплексоров, первый и второй блоки хранения констант, блок управления, первый и второй блоки элементов ИЛИ со связями. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)ю G 06 F 7/72 с

Р

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Ф

° °

° °

Ъ (Ь

0с 4

О (Tс (Ь

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4744557/24 (22) 28.09,89 (46) 30.0?.91. Бюл. М 28 (71) Научно-исследовательский институт прикладных физических проблем им, А.Н. Севченко (72) А.А. Коляда, В.К. Кравцов, И.Н. Куколь и

M.Þ. Селянинов (53) 681.3 (088.8) (56) Авторское свидетельство СССР

hL 1510097, кл. Н 03 M 7/18, 1987.

Авторское свидетельство СССР

М 1305678, кл. G 06 F 7/72, 1986. (54) УСТРОЙСТВО ДЛЯ МАСШТАБИРОВАНИЯ ЧИСЕЛ (57) Изобретение относится к вычислительной технике и предназначено для использования в быстродействующих цифровых

„„ Ы „„1667066 А1 устройствах, функционирующих в непозиционных системах счисления и реализующих различные немодульные операции, такие как деление, умножение дробей, масштабирование, перевод чисел в двоичную систему счисления. Целью изобретения является расширение области применения за счет выполнения операции масштабирования в модулярном коде. Устройство содержит блок элементов задержки, блок вычисления интервального индекса числа, элемент задержки, первый и второй регистры сдвига, регистр модулярного кода числа, регистр интервального индекса, первый и второй блоки мультиплексоров, первый и второй блоки 14 и 15 хранения констант, блок управления, первый и второй блоки элементов ИЛИ со связями. 2 ил.

1667066

Изобретение относится к вычислительной технике и предназначено для использования в быстродействующих цифровых устройствах, функционирующих в непозиционных системах счисления и реализую- 5 щих различные немодульные операции.

Целью изобретения является расширение области применения за счет выполнения операции масштабирования в модулярном коде. 10

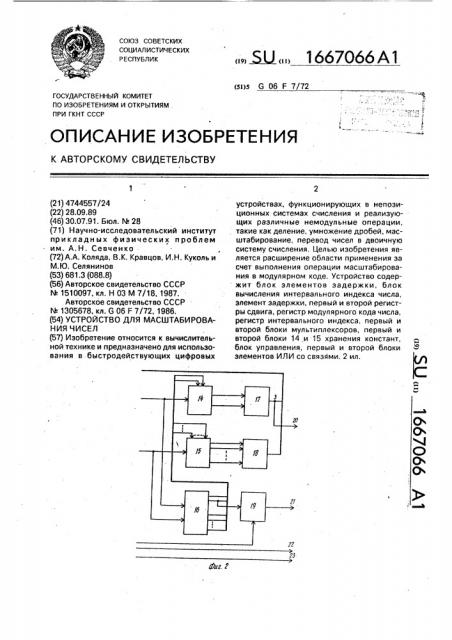

На фиг. 1, 2 представлена схема устройства для масштабирования чисел.

Устройство содержит информационный вход 1 устройства, вход 2 сигнала начала работы устройства, вход 3 масштаба устрой- 15 ства, вход 4 начальной установки устройства, тактовый вход 5 устройства, блок 6 элементов задержки, блок 7 вычисления интервального индекса числа, элемент 8 задержки, первый регистр 9 сдвига, регистр 20

10 модулярного кода числа, регистр 11 интервального индекса, первый и второй блоки 12 и 13 мультиплексоров, первый и второй блоки 14 и 15 хранения констант, блок 16 управления, первый и второй блоки 25

17 и 18 элементов ИЛИ, второй регистр 19 сдвига, выход 20 кода результата устройства, выход 21 двоичного кода остатка устройства, выход 22 сигнала окончания работы устройства, выход 23 сигнала готовности ус- 30 тройства.

Блок 6 элементов задержки представляет собой цепочку из Т-1 последовательно соединенных регистров разрядностью L бит, вход первого и выход (Т - 1)-го из кото- 35 рых являются соответственно входом и выходом блока 6 элементов задержки; Т =

)Iog2Kf, К вЂ” число оснований модулярной сик стемы счисления; L = g Bi здесь и ниже 40

i=1

В! - )Iogzmt(, е1, m2, ..., тк — основания модулярной системы счисления, являющиеся попарно простыми целыми числами, т, е. (m), mj - 1, I, ) = 1, 2, ..., К, Ф j; see модули

m1, m2, ..., ек полагаются нечетными; через

)Х(обозначается наименьшее число, не меньшее Х.

Блок 7 вычисления интервального индекса числа служит для определения за Т 50. тактов по входному модулярному коду (Ж1Ф,Щчисла х б Щ-М + -M + 2, ..., М - 1} машинного интервального индекса числа"!к(Х) по формуле

\ -i I-™,"." I.. I::,I..I.. «i где М = тоМк-1, m — вспомогательный модуль, выбираемый из условий вк > 2m< + К к — 1

-2,mo> К-1;М!,к- =Мк- /тьМк- = Д а ;

1=1 2=! Xlm, I=1,2, ..., К-1,через(У)т обозначается наименьший неотрицательный вычет, сравнимый с величиной Y no модулю m.

Структурно блок 7 вычисления интервального индекса числа аналогичен параллельно — конвейерному блоку суммирования вычетов по модулю гпк и реализуется с помощью)К/2(постоянйых запоминающих устройств, J-e из которых получает сумму по модулю гпту(2) - 1)-ro и (2Д-го слагаемых правой части формулы (1) O = 1, 2, ..., К/2; для определенности К полагается четным), регистров и сумматоров по модулю my,.

Разрядность первого регистра 9 сдвига составляет и + Т+ 1 бит, где n = )logzM(.

Разрядности регистра 10 модулярного кода числа и регистра 11 интервального индекса составляют соответственно L и йк бит.

Первый и второй блоки 12 и 13 мультиплексоров содержат L и Вк мультиплексоров соответственно.

Первый блок 14 хранения констант содержит К узлов памяти для хранения констант соответственно по модулям m1, mz, ..., вк системы счисления и служит для хранения всевозможных„значений цифр модулярного кода чисел Х = (Х/2), где через (X) обозначается целая часть числа Х. При этом

i-й узел памяти первого блока 14 хранения констант реализуется на основе долговременного запоминающего устройства, которое обладает емкостью 2 .слов разрядностью 2BI бит и в его память по адресу gi б (О, 1...„mi-1) записывается пара величин

Р/ 2(2)= < М/Р ф,)Щ@ф, )>=1,2...„К, (2) где

Wi((2(ä) /(g)-s+1) !2! mi,s=1,2.(3)

Компонента набора вычетов (2) с номером vg(1, 2) формируется на т -м выходе l-ro узла памяти для хранения констант по модулю пц. Если при этом единичный сигнал на м-м управляющем входе выдачи кода I-ro узла памяти отсутствует, то поступление с его "го выхода ненулевой информации блокируется. Адресные входы, а также первые и вторые выходы всех узлов памяти в совокупности соответственно составляют адресный вход, первый и второй выходы первого блока 14 хранения констант; J-e управляющие входы выдачи кода всех узлов памяти объединены и подключены x J-any(!1, 2) управляющему входу первого блека 14 хранения констант.

1667066

Второй блок 15 хранения констант служит для хранения значений интервально индексной характеристики )<«(Х), где Х = (X/2), Х = (т1,,(2 „... Ук ) — произвольный элемент рабочего диапазона D. Второй блок 15 хранения констант реализуется на основе дол- 5 говременного запоминающего устройства, обладающего емкостью 2 к слов разрядностью р . By, бит (р = К + cl,

W (I) =< Wy((!),М/к (I), ..., ЧЧк Р (!) >,(4) где

/)+>

0(™ê)Èt- /m при -<+«j и 1ы„и <«+ к-«>< - +Я

/)(I-1(<Я(<;««)+«><Ä «p«Ь= «!«-; p> а <«+е 1 (5)

/)/ - (<)- к) / < +«) +«>

1 «! >< —: р << <; ««<к-««« -<«i 2

«<«< „(Ц

«,) )(1) — интервальный индекс числа "1", 20

Компонента набора вычетов (4) с номером v формируется íà v — м выходе второго блока 15 хранения констант (иа(1, 2...„р)), Если при этом единичный сигнал на 1> — м управляющем входе выдаче кода второго 25 .блока 15 хранения констант отсутствует, то поступление с его выхода ненулевой информации блокируется.

Блок16управления.реализован аналогично узлу анализа прототипа и по интервально-моду 30 лярному коду (К), g2 „, " )< — 2, к — 1, )к(Х)) числа Ф0 вырабатывает требуемую последовательность управляющих сигналов. На выходах блока 16 управления с первого no (P + 2)-й ежетактно генеяируются тв твеннобул - 35 вы величины 9, V, сг1 02,..., îj, определяемые соотношениями

Ч ((>=!)(/, = Ч 15) 0 = (/l «> пp(>< < = >! — я

Р)

Q h ) и р и т. = и .<. » -, где к

« «:Å÷;-я(с-<)«<:-< —:q, „„„

j--> к- (8) +.,СЛ,,, «<<; «.+ C4, = Ô «)+<) «<--«;.<- р (-« > > р в остальных случаях при этом Ч = (," !, к — 1 )2, J= 1, 2, ..., К-1; . = (I(X)/2. А!,к-1 g М j,ê-1 ш), g) = (Х)гп), I(X) — интервальный индекс числа Х, опреде50 ляемыи соотношением

A Л т<х) = л

< к (х) если ) „(х) < гп „- и) - к .2., Л О

I<«(X) - rn«если ).к(х)><т<«-гп„+ к-2; (cjj;+сй„ f 2, ec/(j«((<(),к- <,: четно

М1= (j)j < < ) 2,>

J = 1, 2, ..., К-1;,и I,K-1=j М,K-11

О, в противном случае; ! = 1, 2, ..., k-1, через Х обозначается отрицание булевой величины Х.

Первый блок 17 элементов ИЛИ содержит L двухвходовых элементов ИЛИ.

Второй блок 18 элементов ИЛИ содержит Вк р-входовых элементов ИЛИ.

Разрядность второго регистра 19 сдвига составляет и+1 бит.

Рассмотрим, как работает устройство для масштабирования чисел. По сигналу

Гу т. = 1, подаваемому с входа 4 устройства, первый регистр 9 сдвига обнуляется, тем самым устройство приводится в исходное рабочее состояние.

В целях формирования управляющих сигналов на сигнальных выходах 22 и 23 устройства содержимое первого регистра 9 сдвига ежетактно сдвигается в сторону младших разрядов по сигналу Гт = 1, подаваемому с тактового входа 5 устройства.

При инициации в устройстве очередной операции содержимое первого регистра 9 сдвига логически складывается с подаваемым на

его информационный вход двоичным кодом числа 2 с входа 3 масштаба устройства, т+! где I — номер требуемого масштаба, Sl 2 (!

= 1, 2, ..., и + 1). В результате (Т + I - 1)-й разряд первого регистра 9 сдвига устанавливается в единичное состояние, На первом такте операции масштабирования модулярной код () <,, р,..., gy, ) масштабируемого числа X с информационного входа 1 устройства передается в блок 6 элементов задержки, а также поступает в блок

7 вычисления интервального индекса числа, где в ходе очередных Т тактов, считая текущий, в соответствии с форм.(l) вычисляется машинный интервальный индекс (к(Х) числа.

Кроме этого, на первом такте управляющий сигнал Г- 1, подаваемый с входа 2 устройства, поступает в элемент 8 задержки.

На T-м такте сигнал Г- 1 с выхода элемента 8 задержки подается на управляющие входы первого и второго блоков 12 и

13 мультиплексоров, поэтому появляющие1667066 ся в данном такте на выходах блока 6 элементов задержки и блока 7 вычисления интервального индекса числа модулярный код (ф, ф,..., gy, ) и характеристикэ1к<Х) через вторые информационные входы первого и второго блоков 12 и 13 мультиплексоров соответственно поступают в регистр 10 модулярного кода числа и регистр 11 интервального индекса.

На каждом из последующих тактов операции масштабирования выполняются одни и те же действия. В ходе (Т+ r + 1)-го такта(г= О, 1, ...,1-1) блок 16управления по модулярному коду (ф, уф,..., ф ) и машинному интервальному индексу !к(Хг) числа Xr (при г = О полагается Хо = Х и ( ф ) =pi, I = 1, 2, ..., К), подаваемым íà его первый и второй входы с выходов регистров

10 и 11 модулярного кода числа и интервального индекса соответственно, вырабатывает сигналы тл(г),%(г), оИ,...zzzz оф, олределяемые соотношениями вида (6) — (8). Призна«/ ки Ч) ") и Ч) ") четности числа Xr c первого и второго выходов блока 16 управления подаются соответственно на первый и второй управляющие входы выдачи кода первого блока 14 хранения констант, на адресный вход которого из регистра 10 модулярного кода числа поступают цифры кода

° ° ° ° г) г) Г) )

Сигналы с последних р выходов блока 16 управления подаются на соответствующие управляющие входы выдачи кода второго блока 15 хранения констант, а на его адресный вход из регистра 11 интервального индекса поступает„ интервальноиндексная характеристика IqXr). Если Xr четно(Ф - 1 и Ч ") = О), то на первом выходе первого блока 14 хранения констант сформируется модулярный код (+ 8 + 6 + ) == УУ() (2(г) Wfiz) (Q ))......,...муару)(2гкг))иса х - (xrzz) . (см. (2), (3)), а на втором выходе — код {О О, ..., О). Если же Хг является нечетным (Ч /r) = О, V /r) = 1), то код нуля формируется на первом выходе первого блока 14 хранения констант, а код числа Хг+1, совпадающий в данном случае с кодом. (((у()(2т )),w (Щг) ) „„, уук) (g) ) )(cM.(2)(3))-на ягором выходе. В обоих случаях на выхбде первого блока 17 элементов ИЛИ будет получен модулярный код()((), 2fi "),..., ф () ) числа Хг+1, который через первый информационный вход первого блока 12 мультиплексоров, на уйравляющий вход которого подается сигнал Г = О, пересылается в регистр 10 модулярного кода числа. Что касается сигналоа afi ), ат ),.„, ор),то как видно из (7) и (8), лишь один из них принимает единичное значение. Пусть этот сигнал имеет номер v Тогда на выходах второго блока 15 хранения контакт формируется нал ( бор величин<О, О, ..., О, Р/к (!к(Хг)), О, . „0T

10 !-я из которых представляет собой машинный интервальный индекс числа Хг+1, т. е.

W k )(1к(Хг))= !к(Х +1)(см. (4),(5), при I !к/Xr)).

Характеристика 1к(Хг+1), пройдя через второй блок 18 элементов ИЛИ и второй блок

13 мультиплексоров, поступает в регистр 11 интервального индекса.

Ежетактно содержимое второго регистра 19 сдвига по сигналу Г, = 1, подаваемому с тактового входа 5 устройства, сдвигается на один бит в сторону младших разрядов, после чего в его старший разряд записывается признак четности Ч "), генерируемый на втором выходе блока 16 управления. В результате по окончании (Т + r + 1)-ro такта операции в г+ 1 старших разрядах второго регистра 19 сдвига будет получен двоичный код величины

Г

Вг+1 =, Ча(1 ) 2

30 =о представляющий собой остаток I X I 2г+1 от деления X нэ 2

Согласно изложенному по истечении (T+

+ 2)-го такта на выходе первого блока 17

35 элементов ИЛИ сформируется модулярный код (2fi .;(а),...,)(к) ) искомого целочисленного приближения XI = (Х/21 к дроби

Х/2, а в l старших разрядах второго регист-!

40 ра 19 сдвига — двоичный код остатка К! =

=Х z ; при этом на выходе младшего разряда первого регистра 9 сдвига, а значит и на выходе 22 устройства появляется единичный сигнал, указывающий на то, что процесс

45 масштабирования завершен.

Инициация новой операции в устройстве может быть осуществлена уже на — м такте текущей операции, Признаком готовности устройства к выполнению операции служит единичный сигнал, генерируемый на выходе (Т+1)-го разряда первого регистра 9 сдвига, а соответственно и на выходе 23 устройства.

Формула изобретения устройство для масштабирования чисел, содержащее первый и второй регистры сдвига, регистр модулярного кода числа, регистр интервального индекса, первый и вто1667066

10 рой блоки хранения констант, первый и второй блоки мультиплексоров, блок управления, первый и второй блоки элементов ИЛИ, причем вход масштаба устройства и вход начальной установки устройства соединены соответственно с информационным входом и входом сброса первого регистра сдвига, вход разрешения сдвига которого соединен с тактовым входом устройства и с входом разрешения сдвига второго регистра сдвига, выход которого является выходом двоичного кода остатка устройства, выход первого блока мультиплексоров соединен с входом регистра модулярнаго кода числа, выход которого соединен с адресным входом первого блока хранения констант и с первым входом блока управления, первый и второй выходы которого соединены с соответствующими входами разрешения выдачи первого блока хранения констант, первый и второй выходы которого соединены с соответствующими входами первого блока эле.ментов ИЛИ, выход которого является выходом кода результата устройства, выход сигнала окончания работы которого соединен с выходом первого разряда первого регистра сдвига, выход второго блока мультиплексоров соединен с входом регист-. ра интервального индекса, выход которого соединен с адресным входом второго блока хранения констант и с вторым входом блока управления, второй выход которого соединен с информационным входом второго регистра сдвига, 1-й вход разрешения выдачи и I-й выход второго блока хранения констант

5 (! = 1 — К+ q+ 1; К вЂ” количество оснований;.

q — целая часть числа К/2) соединены соответственно с (l + 2 -м выходом блока управления и с 1-м входом второго блока элементов ИЛИ, выходы первого и второго

10 блоков элементов ИЛИ соединены с первыми информационными входами первого и второго блоков мультиплексоров соответственно, отличающееся тем,что,сцелью расширения области применения за счет

15 выполнения операции масштабирования в модулярном коде, оно содержит блок элементов задержки, блок вычисления интервального индекса числа и элемент задержки, причем информационный вход

20 устройства соединен с входами блока элементов задержки и блока вычисления интервального индекса числа, выходы которых соединены соответственно с вторыми информационными входами первого и второго

25 блоков мультиплексоров, управляющие входы которых соединены с выходом элемента задержки, вход которого соединен с входом сигнала начала работы устройства, выход сигнала готовности которого соединен с вы30 ходом () log2K (+ 1)-IG разряда первого регистра сдвига.

1667066

Составитель А.Клюев

Техред M.Ìoðãåíòàë Корректор О.Кундрик

Редактор О.Спесивых

Производственно-издательский комбинат "Патент", r. Ужгород, ул.Гагарина, 101

Заказ 2524 Тираж 398 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб„4/5