Система для контроля электронных устройств

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в системах автоматического контроля интегральных схем, а также цифровых блоков и устройств при их производстве и эксплуатации. Целью изобретения является повышение быстродействия устройства. С этой целью в устройство, содержащее блок задания тестов и анализа реакций, тактовый генератор, блок сравнения, распределитель импульсов, формирователь импульсов, счетчик импульсов, сдвиговый регистр и блок коррекции, введены блок оперативной памяти, одновибратор записи и счетчик адреса. 4 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛ ИСТИЧ Е СКИХ

РЕСПУБЛИК (51)5 G 06 F 11/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

0с

0с 4

О фь. (21) 4482320/24 (22) 13.09.88 (46) 30.07.91. Бюл, Q 28, (72) С.А. Бажанов, В. В, Мин газудинов и И.с.кац (53) 681.32(088,8) (56) Авторское свидетельство СССР

hh 696464, кл. 6 06 F 11/00, 1979.

Авторское свидетельство СССР

ЬЬ 978151, кл, G 06 F 11/00, 1982. (54) СИСТЕМА ДЛЯ КОНТРОЛЯ ЭЛЕКТРОННЫХ УСТРОЙСТВ (57) Изобретение относится к вычислительной технике и может быть использовано в

Изобретение относится к вычислительной технике и может быть использовано в системах автоматического контроля интегральных схем, а также цифровых блоков и устройств при их производстве и эксплуатации

Целью изобретения является повышение быстродействия устройства.

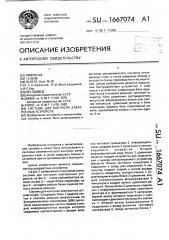

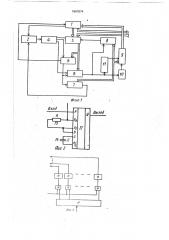

На фиг.1 изображена стурктурная схема системы для контроля электронных устройств; на фиг.2 — схема одновибратора записи; на фиг.3 — схема блока коррекции; на фиг.4- алгоритм работы блока задания тестов и анализа реакций.

Система для контроля электронных устройств (фиг.1) содержит блок 1 задания тестов и анализа реакций (аналогичный по функциональному назначению ЦВМ прототипа), выход признака теста и первый и второй информационные выходы которого соединены соответственно с входом запу-.

„, Б ) „„1667074 А1 системах автоматического контроля интегральных схем, а также цифровых блоков и устройств при их производстве и эксплуатации. Целью изобретения является повышение быстродействия устройства. С этой целью в устройство, содержащее блок задания тестов и анализа реакций, тактовый генератор, блок сравнения, распределитель импульсов, формирователь импульсов, счетчик импульсов, сдвиговый регистр и блок коррекции, введены блок оперативной памяти, одновибратор записи и счетчик адреса. 4 ил. ска тактового генератора 2, информационными входами блока 3 сравнения и контролируемого устройства, Второй информационный вход блока 3 сравнения является входом устройства для подключения к выходу контролируемого устройства (объекта). Выход тактового генератора 2 подключен к входу распределителя 4 импульсов, первый, второй и третий выходы которого соединены соответственно с управляющим входом блока 3 сравнения, входом синхронизации формирователя 5 импульсов и входом записи сдвигового регистра 6. Выход блока 3 сравнения подключен к информационным входам сдвигового регистра 6 и формирователя 5 импульсов, первый выход которого подключен к счетным входам сдвигового регистра 6 и счетчика 7. Второй выход формирователя 5 подключен к входу останова тактового ненератора 2, входу останова блока 1

1667074

Окончании переходных процессов в контролируемом устройстве блок 1 задания тестов и анализа реакций запускает генератор 2, который начинает вырабатывать последова1 ellbHocTb тактовых импульсов, Запустив генератор 2, блок 1 освобождается от процесса контроля данного устройства. Тактовые импульсы от тактового

råHåðàToðà поступают на распределитель 4 ймпульсов. Первый тактовый импульс поступает на управляющий вход блока 3 сравнения, второй вход которого подключен к

55 и выходу переполнения счетчика 7, а информационный выход счетчика 7 соединен с информационным входом блока 8 коорек ции и входом данных блока 9 оперативной памяти, -5

Выход сдвигового регистра 6 подкючен к управляющему входу блока 8 коррекции, управляющему входу одновибратора 10 записи и счетному входу счетчика 11 адреса.

Выход блока 8 коррекции подключен к 10 третьему информационному входу блока 3 ! ,сравнения. Выход счетчика 11 адреса под ключен к адресному входу блока 9, вход

,записи которого соединен с выходом одновибратора 10, Выход блока 9 подключен к 15

:информационному входу блока 1 задания тестов и анализа реакций.

Блок 9 оперативной памяти может. быть реализован на микросхемах типа 20 ,155РУ7 с разрядностью по шинам данных, равной разрядности счетчика 7.

Счетчик 11 адреса может Г ть выполнен на микросхемах типа 155И f с разряд,ностью, равной количеству каналов 25 . сравнения. Одновибратор 10 записи выпол нен на микросхеме 12 типа 155АГ1 (фиг.2), роме микросхемы 12, одновибратор 10 соI åðæèT резистор 13 и конденсатор 14.

Блок 8 коррекции аналогичен блоку кор- 30 некции известного объекта, Блок коррекции содержит (фиг.3) триг)еры 15, элементы И 16 и дешифратор 17, выходы которого подключены к первым входам соответствующих элементов И 16, вто- 35 ые входы элементов И 16 объединены ежду собой и являются управляющим вхоом блока 8 коррекции, а выходы элементов

16 подключены к входам "Установка 1" оответствующих триггеров 15, 40

Система работает следующим образом.

На каждом шаге тестовой последовательности блок 1 считывает из своей памяти очередной тестовый набор кода, состоящий из 1 и О, и выдает этот код на контролируемое устройство. Затем блок 1 передает в блок 3 сравнения эталонный набор кода, Ооответствующий требуемым ответным сигналам контролируемого устройства. По выходу контролируемого устройства. В результате первый тактовый импульс разрешает прохонкдение сигналов с выхода контролируемого устройства на блок 3 сравнения, где они сравниваются с эталонным набором кода, В блоке 3 формируется код, содержащий О в тех разрядах, где выходной сигнал контролируемого устройства совпадает с эталонным сигналом, и 1 в тех разрядах, где совпадения не происходят. Второй тактовый импульс поступает на вход записи сдвигового регистра 6 и разрешает перезапись. в последний содержимого блока 3 сравнения.

Третий и последующие тактовые импульсы с распределителя 4 импульсов поступают на вход синхронизации формирователя 5, вход которого подключен к выходу блока 3 сравнения. Если сигналы контролируемого устройства совпадают с эталонным набором кода, на втором выходе (срэвнение) формирователя 5 формируется сигнал, который запрещает дальнейшую работу тактового генератора 2 и поступает на вход останова блока 1. Если же сигналы контролируемого устройства не совпадают с эталонным набором кода, то формируется сигнал "Несравнение" на первом выходе формирователя 5. По каждому импульсу

"Несравнение" формирователя 5 содержимое сдвигового регистра 6 сдвигается на один разряд, а содержимое счетчика 7 увеличивается на 1. Если на выходе регистра 6 появляется сигнал "1", что свидетельствует о несовпадении сигнала контролируемого устройства с эталонным, то этот сигнал с выхода регистра 6 поступает нэ счетный вход счетчика 11, увеличиаая его содержимое qa 1, и на вход однсвибратора 10. Содержимое счетчика 7, соответствующее в этот момент номеру разряда кода. в котором произошло несовпадение, сигналом с выхода одновибратора 10 заносится в блок 9 по адресу на выходе счетчика 11.

При появлении следующего несовпадения разрядов кодов, т.е. "1" на выходе регистра 6, снова этот цикл повторяется и в следующую ячейку блс ка 9 записывается содержимое счетчика 7..

Сдвиги содержимого регистра 6 продолжаются до тех пор, пока в блок 9 не будет передан адрес последнего из несовпадэющих разрядов. После этого оставшиеся разряды кодов не опрашиваются, тактовый генератор 2 выключается и в блок 1 поступает сигнал останова. Это обеспечивается тем, что при каждом несовпадении разрядов кода происходит коррекция соответствующего разряда в блоке 3 сравнения, т.е.

1667074 состояние этого разряда с помощью сигналов блока 8 коррекции (фиг,3) принудительно устанавливается в "О".

Содержимое счетчика 7 подается на вход дешифратора 17, поэтому в каждый момент времени имеется разрешающий потенциал на одном иэ элементов И 16. При появлении "1" на выходе регистра 6 возбуждается вход "Установка 1" соответствующего триггера 15. Сигнал с выхода этого триггера 15 поступает в блок 3 сравнения и корректирует его, т.е. переводит из "1" в "О".

Таким образом. по мере продвижения содержимого регистра 6 происходит последовательная коррекция разрядов. в которых имеет место несравнение.

Алгоритм работы блока задания тестов и анализа реакций приведен на фиг.4.

По сигналу "Останов" блок 1 задания тестов и анализа реакций считывает последовательно содержимое блока 9, начиная с первого адреса до адреса с содержимым, равным О.

Содержимое ячеек блока 9, отличное от

О, соответствует номеру разряда, по которому зарегистрировано несовпадение, содержимое ячейки 9, равное 0 ° блок 1 воспринимает как отсутствие раЗрядов несравнения и переходит к анализу результатов или формированию и выдаче тестового набора.

Формула изобретения

Система для контроля электронных устройств, содержащая блок задания тестов и анализа реакций, тактовый генератор, блок сравнения, распределитель импульСов, формирователь импульсов, сдвиговый регистр, счетчик импульсов и блок коррекции. при этом выход признака теста и первый информационный выход блока задания тестов и анализа реакций соединены соответственно с входом запуска тактового

15

25. входом блока коррекции, выход сдвигового регистра подключен к управляющему входу блока коррекции, выход которого соединен

40 генератора и первым информационным входом блока сравнения, второй информационный выход блока задания тестов и анализа реакций и второй информационный вход блока сравнения являются выходом и входом устройства для подключения соответственно к входу и выходу объекта контроля. выход тактового генератора подключен к входу распределителя импульсов, первый, второй и третий выходы которого соединены соответственно с управляющим входом блока сравнения, входом синхронизации формирователя импульсов и входом записи сдвигового регистра, выход блока.сравнения подключен к информационным входам сдвигового регистра и формирователя импульсов, первый выход которого соединен со счетными входами сдвигового регистра и счетчика импульсов, второй выход формирователя импульсов объединен с выходом переполнения счетчика импульсов и подключен к входам останова тактового генератора и блока задания тестов и анализа реакций,.информационный выход счетчика импульсов соединен с информационным с третьим информационным входом блока сравнения, отличающаяся тем, что, с целью повышения быстродействия, она содержит блок оперативной памяти, одновибратор.записи и счетчик адреса, счетный вход и выход которого подключены соответственно к выходу сдвигового регистра и адресному входу блока оперативной памяти, вход данных, вход записи и выход которого соединены соответственно с информационным выходом счетчика импульсов, выходом одновибратора записи .и информационным входом блока задания тестов и анализа реакций, а вход одновибратора записи подключен к выходу сдвигового регистра.

1667074

1667074

0еродотка прерввдоная па сигналу. Остонод

Чтение очврвдноп данные аг Иу g

"налог доннеас йндиквнея 4wрворв

«несвдлоденив а аг еощасе для akckkggdmrd riprCkmnn

Фае,4

Составитель Г. Виталиев

Техред М.Моргентал Корректор О. Ципле

Редактор А. Лежнина

Закаэ 2525 Тираж 414 Подписное

ВНИИПИ Государственного комитета по иэобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

Последна

mkem г дебор аж блокп1 оиередного тгстодаге наЯра дыдвчп mepefavm тест дога набоРа на нвнтролируеное ycmprpcm8a дыдор аг ОЯ блока t отредноге втолонного нодара быдоча (лвяеда а> зталенногю Побора о устро стда сродиения d фвятрв ание и Ыдача сигнала .Запуск на гене ратор2 товтвдыг ннлвльсод

ВкИаннв пяврв ауця вт сиен ыо .дстонод от счетчнкв1нввф рнвявввлпвв . Ввв иввндвя вя вавнв вввса обряде а- Сагнол сп щоврыдо .дствнвд

Жюм 1от согнала