Вычислительная система

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в автоматизированных системах обработки информации. Целью изобретения является расширение функциональных возможностей системы за счет адаптивного перераспределения загрузки процессоров. Поставленная цель достигается тем, что в вычислительную систему, содержащую основной и дополнительный процессоры, введены блок контроля загрузки и блок переключения заявок. 1 з.п. ф-лы, 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19). (11) (51)5 G 06 F 15/16

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОбРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4730493/24 (22) 18.08.89 (46) 30,07.91, Бюл. М 28 (72) С.B.Àíäðååâ, С.B.ÊóçíåöîB, А.И.Пантюхин и B.Ñ.Ôèëàòîâ (53) 681.325 (088.8) (56) Авторское свидетельство СССР

N 1267429, кл. G 06 F 15/16, 1986.

Авторское свидетельство СССР

М 1168960, кл. G 06 F 15/16, 1985, Изобретение относится к вычислительной технике и может быть использовано в автоматизированных системах обработки информации.

Цель изобретения — расширение функциональнах возможностей путем адаптивного перераспределения загрузки процессоров.

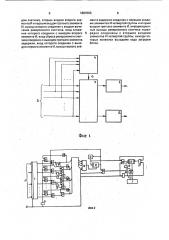

Ка фиг.1 представлена структурная схема вычислительной системы; на фиг.2 — функциональная схема блока контроля загрузки; на фиг.3 — функциональная схема блока переключения заявок.

Вычислительная система (фиг.1) содержит основной и дополнительный процессоры 1 и 2, блок 3 переключения заявок, блок

4 контроля загрузки, входы 5 заявок; связь

6 передачи кода загрузки.

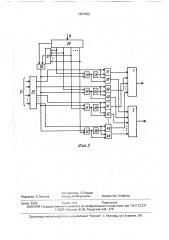

Блок контроля загрузки (фиг.2) содержит регистр 7, триггеры 8, элементы И 9, элементы HE 10, элементы И 11, 12, элементы 13 задержки, 11ифратор 14, генератор 15 импульсов, счетчик 16; элементы И 17, 18, элементы 19 и 20 задержки, реверсивный (54) ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА (57) Изобретение относится к вычислительной технике и может быть использовано в автоматизированных системах обработки информации. Целью изобретения является расширение функциональных возможностей системы за счет адаптивного перераспределения .загрузки процессоров.

Поставленная цель достигается тем, что в вычислительную систему, содержащую Основной и дополнительный процессоры, введены блок контроля загрузки и блок переключения заявок. 1 з.п, ф-лы, 3 ил. счетчик 21, группу элементов И 22, элемент

И 23, элемент 24 задержки.

Блок переключения заявок (фиг,3) содержит регистр 25, элемент И 26, элемент

ИЛИ 27, регистр 28, элементы И 29 — 32, элементы НЕ 33-36, элементы И 37-44.

Процессор 1 предназначен для обслуживания m типов заявок с параметрами т1;

Т (i = 0,1,...m-1),где т1 — продолжительность решения задачи по заявке i-го типа; T!— период поступления заявок 1-го типа на вход, О системы. С

Процессор 2 предназначен для обслуживания той части поступивших заявок, которые временно перегружают первый процессор.

Блок 4 контроля загрузки служит для формирования кода загрузки первого процессора. На его входы поступают заявки всех типов. Выходной сигнал устройства представляет собой код, знак которого свидетельствует о перегрузке (недогрузке) первого процессора, а значение кода

1667093 l0

15 определяет степень перегрузки (недогрузки).

Блок 3 переключения заявок служит для подключения поступивших на вход системы заявок на первый или второй процессоры.

Подключение производится в зависимости от знака и величины кода, поступающего с блока контроля загрузки.

Система работает следующим образом.

Поступающие на входы 5 системы заявки на обслуживание подаются на блок 3 переключения заявок и на блок 4 контроля загрузки. В блоке 4 контроля загрузки определяется сумма вида которая сравнивается с величиной То базового такта работы системы, Определяется значение где m — число источников заявок.

Если Л является отрицательной величиной, то это значит, что все поступившие задачи могут быть решены первым процессором в течение интервала времени Т .

Если Л является положительной величиной, то это свидетельствует о перегрузке процессора 1, т.е. поступившие на вход системы заявки не могут быть обслужены в очередном такте То, поскольку суммарная продолжительность решения поступивших заявок больше такта То. В этом случае блоком 3 осуществляется перекоммутация части заявок с процессора 1 на процессор 2, Формула изо ре гения

1, Вычислительная система, содержащая основной и дополнительный процессоры, информационные выходы которых являются выходами результатов решения задач системы, отличающаяся тем, что, с целью расширения функциональных возможностей за счет адаптивного перераспределения загрузки процессоров, в нее введены блок контроля загрузки и блок переключения заявок, причем входы с первого по m-й (m — число источников заявок) блока контроля загрузки соединены соответственно с входами с первого по m-й блока переключения заявок и являются входами заявок системы, выход кода загрузки блока контроля загрузки соединен с одноименным входом блока переключения заявок, выходы с первого по m-й первой группы

55 блока переключения заявок соединены соответственно с входами прерывания с первого по m-й основного процессора, выходы с первого по m-й второй группы блока переключения заявок соединены соответственно с входами прерывания с первого по m-й дополнительного процессора.

2. Система по п.1, отл и ч а ю ща я с я тем, что блок контроля загрузки содержит

m-разрядный регистр, группу из m триггеров, первую группу из m элементов И, группу из m-1 элементов НЕ, группу из rn элементов задержки, вторую группу из rn — 1 элементов И, третью группу из m — 2 элементов И, шифратор, генератор импульсов, счетчик, три элемента И, три элемента задержки, реверсивный счетчик, четвертую группу элементов И, причем входы установки регистра являются входами заявок блока, вход сброса регистра является входом базового такта блока и соединен с входами первого и второго элементов задержки, с первым входом шифратора, первыми входами первого и второго элементов И, выходы с первого по m-й регистра поразрядно соединены с первыми входами элементов И первой группы, выходы которых с первого по (m — 1)-й соединены. соответственно с входами элементов НЕ группы, инверсные выходы триггеров группы соединены соответственно с вторыми входами элементов И первой группы, третьи входы которых соединены с выходом переполнения счетчика, вторым входом первого элемента И и входом запуска генератора импульсов, выход второго элемента задержки соединен с входами сброса триггеров группы, входы установки которых соединены соответственно с выходами элементов задержки группы, входы которых соединены соответственно с входами с второго по m+1)-й шифратора, входы элементов задержки с второго по m-й группы соединены с выходами элемента И второй группы, вход первого элемента задержки группы соединен с выходом первого элемента И первой группы, выходы элементов И с второго по m-й первой группы соединены с первыми входами элементов И второй группы, выходы элементов НЕ с второго по (m — 1)-й группы соединены соответственно с первыми входами элементов И третьей группы, выход первого элемента HE группы соединен с вторыми входами элементов И второй и третьей групп, выход I-го (I = 1...(m — 2)) элемента И третьей группы соединен с вторыми входами (1+1)-х элементов И второй и третьей групп, выход шифратора соединен с входом установки счетчика, выход генератора импульсов соединен со счетным вхо166.7093. дом счетчика, вторым входом второго элемента И и первым входом третьего элемента

И, выход которого соединен с входом вычитания реверсивного счетчика, вход сложения которого соединен с выходом второго элемента И, вход сброса реверсивного счетчика соединен с выходом третьего элемента задержки, вход которого соединен с выходом первого элемента И, выход пеового элемента задержки соединен с первыми входами элементов И четвертой группы и вторым входом третьего элемента И, информационные выходы реверсивного счетчика пораз5 рядно соединены с вторыми входами элементов И четвертой группы, выходы которых являются выходами кода загрузки блока.

1667093

Составитель Б,Резван

Техред М,Моргентал Корректор И,Муска

Редактор С.Лисина

Заказ 2526 Тираж 413 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Рэушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101