Запоминающее устройство с исправлением ошибок

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при создании систем памяти при блочной организации считывания информации. Целью изобретения является повышение надежности устройства. Устройство содержит накопитель, регистр адреса, первый и второй коммутаторы, блок кодирования, блок коррекции, блок построчного контроля, блок обнаружения ошибок, сумматор, счетчик, группу элементов И. В режиме записи массива в устройстве формируются контрольные разряды по каждой строке (слову) и контрольная сумма массива. В режиме считывания данные о наличии ошибок при построчном контроле и текущая контрольная сумма массива поступают в блок обнаружения ошибок, формирующий сигналы корректируемой и некорректируемой ошибок. Для коррекции ошибок осуществляется повторное считывание массива. 3 ил.

COIO3 СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)5 G 11 С 29/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4675763/24 (22) 11,04.88 (46) 30,07.91, Бюл. Я 28 (72) О.В,Росницкий, В.Н.Ковалев, А.И.Са, вельев, О.Ф.Лашкова, Л.В.Алексеев, А.Д.Жучков и С.Б.Торотенков (53) 681.327,6 (088.8) (56) Авторское свидетельство СССР

t+ 1276145, кл. G 11 С 29/00, 1987.

Авторское свидетельство СССР

М 1297120, кл, G 11 С 29/00, 1987, (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С

ИСПРАВЛЕНИЕМ ОШИБОК (57) Изобретение относится к вычислительной технике и может быть использовано при создании систем памяти при блочной организации считывания информации. Целью

Изобретение относится к вычислительной технике и может быть использовано при создании систем памяти при блочной организации считывания информации.

Цель изобретения — повышение надежности устройства.

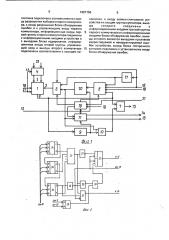

На фиг.1 приведена схема запоминающего устройства с исправлением ошибок; на фиг.2 — схема блока обнаружения ошибок; на фиг.3 — пример реализации сумматора, Устройство содержит накопитель 1 с адресными 2 и информационными 3 входами, регистр адреса 4, первый коммутатор 5, выходы 6 накопителя 1, блок коррекции 7, второй коммутатор 8, блок построчного контроля 9, группу элементов И 10, блок обнаружения ошибок 11, вход сброса 12, информационные выходы 13, выходы при Ы 1667156 А1 изобретения является повышение надежности устройства. Устройство содержит накопитель, регистр адреса, первый и второй коммутаторы, блок кодирования, блок коррекции, блок построчного контроля, блок обнаружения ошибок, сумматор, счетчик, группу элементов И. В режиме записи массива в устройстве формируются контрольные разряды по каждой строке (слову) и контрольная сумма массива. В режиме считывания данные о наличии ошибок при построчном контроле и текущая контрольная сумма массива поступают в блок обнаружения ошибок, формирующий сигналы корректируемой и некорректируемой ошибок. Для коррекции ошибок осуществляется повторное считывание массива. 3 ил. и знаков корректируемой 14 и некорректируемой 15 ошибок, информационные входы

16, блок кодирования 17, вход записи-считывания 18, счетчик 19, сумматор 20, вход обмена 21, адресные входы 22, вход 23 регистра адреса 4. Q3

Блок обнаружения ошибок 11 (фиг.2) со- О держит одноразрядные сумматоры 24, элемент ИЛИ-НЕ 25, элементы НЕ 26,27, триггер 28, элементы И 29,30, элемент И-НЕ

31 и элемент И-ИЛИ-НЕ 32.

На фиг.3 показан вариант выполнения сумматора 20, состоящего иэ триггеров 33, Устройство работает следующим образом.

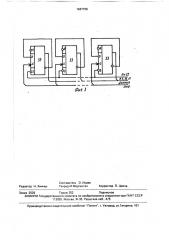

B режиме записи на вход 18 приходит сигнал записи, а информация поступает на входы 16 устройства и далее в блок кодиро1667156 счетчика подключены соответственно к входу разрешения выборки второго коммутатора, к входу разрешения блока обнаружения ошибок и к управляющему входу первого коммутатора, информационные входы первой группы второго коммутатора соединены с информационными входами устройства и с выходами блока кодирования, информационные входы второй группы, управляющий вход и выходы второго коммутатора подключены соответственно к выходам накопителя, к входу записи-считывания устройства и к входам группы сумматора, выходы которого соединены с информационными входами третьей группы

5 первого коммутатора и с информационными входами блока обнаружения ошибок, выходы которого являются выходами признаков корректируемой и некорректируемой ошибок устройства, выход блока построчного

10 контроля подключен к установочному входу блока обнаружения ошибок.

1667156

Редактор Н. Химчук

Корректор О. Ципле .

Заказ 2529 Тираж 352 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, К-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

Составитель О. Исаев

Техред M.Moðãåíòàë

Н е

@md.