Устройство для контроля и коррекции адресных сигналов памяти последовательного действия

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и предназначено для организации последовательной адресации ячеек памяти. Цель изобретения - повышение надежности устройства. Устройство содержит первый 1 и второй 2 адресные счетчики, элемент сравнения 3, дифференцирующий элемент 4, триггер 5, первый 6 и второй 7 элементы ИЛИ, блок анализа 8, управляемый генератор импульсов 9. Устройство позволяет восстановить очередной адрес обращения к блоку памяти при случайном сбое адресных счетчиков или при временном пропадании питающих напряжений. 4 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

0Р) ((() (я)5 G 11 С 29/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4739374/24 (22) 04.08,89 (46) 30.07.91. Бюл. М 28 (71) Пензенское производственное объединение "Электромеханика" (72) М.Л.Антокольский, Л,А.Антонов, А.В.Юматов и С.В. Кутырева (53) 681.327.6 (088.8) (56) Авторское свидетельство СССР

РЬ 1023399, кл. G 11 С 29/00, 1982.

Авторское свидетельство СССР

М 813504, кл. G 11 С 8/00, 1974. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И КОРРЕКЦИИ АДРЕСНЫХ СИГНАЛОВ ПАМЯТИ

ПОСЛЕДОВАТЕЛЬНОГО ДЕЙСТВИЯ (57) Изобретение относится к вычислительной технике и предназначено для организации последовательной адресации ячеек памяти. Цель изобретения — повышение надежности устройства. Устройство содержит первый 1 и второй 2 адресные счетчики, элемент сравнения 3, дифференцирующий элемент 4, триггер 5, первый 6 и второй 7 элементы ИЛИ, блок анализа,8, управляемый генератор импульсов 9. Устройство позволяет восстановить очередной адрес обращения к блоку памяти при случайном сбое адресных счетчиков или при временном пропадании питающих напряжений.

4 ил.

5 l0 I5

Изобретение относится к вычислительной технике и предназначено для Организа„ ии последоватег1ьной здресавии ячеек

ПЗМЯТИ, Цель изобретения — повышение нздеж-!

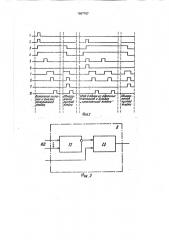

",ости устройства, На фиг,1 представлена блок-схема устройства; на фиг,2 — временная Дизгг1амма работы устройства при вялю 1ении питания или сбое одного из адресных сче.чиков; на фиг.3 — структурная схема блока анализа; на фиг.4 — структурная схема управляемого генератора.

УстроЙство содержит два адресных счетчика 1 и 2, элемент сравнения 3, дифференцирующий элемент 4, триггер 5, два элемента ИЛИ б и 7, Ьлак 8.= нализа состояния ячейки, у!,"ðàâëÿåìü!é генератор импульсов

9. Иа фиг,1 обозначено, 10 — лина питания, 11 — вход "Чтение/запись", ";2 — вход

"Сброс", I Ç вЂ” выход "Чтение", 14 — выход

"Разрешение", 15 — информацио-1ные вхоДы-выходы, 16 — здресн.1е входы ус гройства, В работе устройства принимают участие узлы и элементы, не входящие в em состав: бг1ок управления 17, элементы ИЛИ

18 и 19, блок памяти 20, автономный источник питания 21.

Блок анализа состояния ячейки представляет собой последовательно соединенные элементы ИЛИ-НЕ 22 и И 23 гфиг.3), Угравляемый генер .тор 9 (фи,4) содерNL»T Одновибратор 24, инвертор 25, генераTGp импульсов 26, первый 3flBMpHT ИЛИ 27, элемент И 28, четыре 0-триггера 29-3 . второй элемент ИЛИ ЗЗ, Устройство (фиг,1) работает следующим образом.

Перед записью производится установка всех ячеек блока памяти 20 в начальное состояние, для чего блок 17 управления формирует сигнал "Сброс" 12, устанавливающий здрес1-,ые счетчики 1 и 2 в нулевое состояние; код начального состояния, напоимер, ОО на шине "Данные" блока . 7 (в масштабе эзписы BBBMoé в дс1льнейшем информации этоГ код не должен ис" пользоваться}; сигнал Запись, который через лемен Г ИЛИ 1 8 п4)I т пав 1 н (»/строй ство как сигнал "Чтение-запись" 11, Код адреса с выхода адресноГО счетчика

1 по 1. !ине адреса 16 Г1оступае Г на ад1эесные входы блока памяти 20 и з блок 1 г управления, Сигнал "Чтение/запись" 11 через элемент ИЛИ 7 поступает нз вход управляемого генератора,), который на своем втором выходе фор ирует сигнал "Разрешение" ) 4, по кОтОрому Г1роизводится запись в нулеву1о ячейку начального состо" яния. Затем, по сигналу с четвертого выхода управляемого генератора 9 происходит увеличение состояния счетчиков 1 и 2. Далее, сигналы со второго и четвертого выходов генератора 9 осуществляется запись начального состояния ячейки блока памяти 20 с последовательно увеличивающимися адресами. Блок 17 управления анализирует коды адресов, выдаваемых по шине адреса

16, и после записи начального состояния в ячейку со старшим адресом массива снимает сигнал "Запись".

Установка блока памяти 20 в исходное состояние закончена и устройство может быть выключено. Сохранение при выключенном питании начального состояния ячеек так же, как и сохранение информации, которая будет записана в дальнейшем, может быть Обеспечено, например за счет авГономнОГО источника питаниЯ 21

После включения питания на вход дифференцирующего элемента 4 по шине питания 10 поступит сигнал.

Дифференцирующий элемент 4 сформулирует импульс, который установит триггер 5 в единичное состояние, а адресные счетчики 1 и 2 в нулевое. Сигнал с выхода триггера

5 по цепи сигнала "Чтение" 13 через элемент ИЛИ 19 поступит на вход "Чтение" блока памяти 20, а через элемент ИЛИ 7 на вход управляемого генератора 9, обеспечивая появление на его выходах импульсов: на первом — разрешения сравнения состояний адресных счетчиков 1 и 2,на втором — *Разрешение" 14, rio которому считываются данные из нулевой ячейки блока памяти 20 из вход блока 8; на третьем — разрешения анализа поступивших данных. Если считанные данные не соответствуют коду начального состояния, т.е, если в эту ячейку уже была произведена запись информации, блок 8 не выдаст сигнала. На четвертом выходе управляемого генератора 9 сформируется импульс счета, и состояние счетчиков 1 и 2 увеличится на 1, после чего повторится цикл чтения и анализа состояния следующей ячейки. При анализе состояния ячейки, запись в которую не производилась, блок 8, обнаружив код начальной установки, выдаст сигнал переключения триггера 5, После этого сигнал управления генератором 9 снимается. Адресные счетчики 1 и 2 останутся в состоянии, соответствующем адресу первой обнаруженной свободной ячейки (свободной Ячейки с младшим адресом), и устройство готово к записи в блок памяти 20 информации.

При записи информации блок 17 управления выдает данные, которые поступают на вход блока памяти 20. Одновременно

1667157 формируется импульс "Запись", который через элемент ИЛИ 18 поступает в цепь сигнала "Чтение/запись" 11 и далее через элемент ИЛИ 7 на вход управления управляемого генератора 9.

Элемент сравнения 3 по сигналу с первого выхода управляемого генератора 9 проводит сравнение состояния счетчиков 1 и 2, Если состояния этих счетчиков одинаковы, сигнал на выходе элемента сравнения 3 не формируется и сигналом "Разрешение"

14 производится запись данных, Далее, сигналом с четвертого выхода управляемого генератора 9 счетчики 1 и 2 переводятся в следующее состояние, т.е, формируется адрес следующей ячейки.

Если к моменту появления сигнала "3aпись" произошел сбой адресных счетчиков

1 и 2, то в этом случае, элемент сравнения 3 сформирует сигнал, который через элемент

ИЛИ 6 поступит на цепи установки в единичное состояние триггера 5 и в нулевое состояние счетчиков 1 и 2:

Далее происходит поиск первой незанятой ячейки памяти так же, как это было описано для случая включения питания.

Для исключения ложного срабатывания из-за разброса времени срабатывания счетчиков схема сравнения синхронизируется сигналом со втооого выхода генератора импульсов 9. В зависимости от того, какое содержимое имеет ячейка, запись информации в которую не производилась, могут быть предложены несколько вариантов построения блока 8. Если при стирании в ячейку памяти записывается код 00...00, блок анализа может представлять собой последовательно соединенные элементы

ИЛИ-НЕ 22 и И 23.

Работа управляемого генератора импульсов 9 начинается при поступлении на его вход сигнала управления, по фронту которого одновибратором 24 вырабатывается импульс, который через первый элемент

ИЛИ 27 проходит на вход первого триггера

29. Далее, триггерами 29 — 32 и вторым weментом ИЛИ 33 формируются последовательно сигналы 1 — 4 (соответственно, разрешение анализа состояния адресных счетчиков, разрешение обращения к блоку памяти 20, разрешение анализа считанных данных и увеличение состояния счетчиков).

Благодаря обратной связи выхода четвертого триггера 32 через элемент И 28 и первый элемент ИЛИ 27 обеспечивается циклическое формирование указанных сигналов в течение всего времени наличия на входе управляемого генератора 9 сигнала

55 управления. Если к моменту окончания анализа считанных данных сигнал на входе управляемого генератора 9 будет снят, то передача сигнала с выхода третьего триггера 31 через элемент И 28 на вход четвертого триггера 32 будет запрещена, формирования сигнала увеличения состояния счетчиков не произойдет и работа управляемого генератора 9 прекратится.

Синхронизация работы триггеров 29 — 32 производит я с помощью генератора импульсов 26, Формула изобретения

Устройство для контроля и коррекции адресных сигналов памяти последовательного действия, содержащее два адресных счетчика, элемент сравнения, дифференцирующий элемент, триггер, выходы первого адресного счетчика являются адресными выходами устройства и соединены с входами первой группы элемента сравнения, входы второй группы которого соединены с выходами второго адресного счетчика, первый вход сброса которого соединен с первым входом сброса первого адресного счетчика и является входом сброса устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности устройства, в него введены первый и второй элементы ИЛИ, блок анализа состояния ячейки,.управляемый генератор импульсов, первый выход которого соединен с управляющим входом элемента сравнения, выход которого соединен с первым входом первого элемента

ИЛИ, второй вход которого соединен с выходом дифференцирующего элемента, вход которого соединен с шиной питания устройства, выход первого элемента ИЛИ соединен с вторыми входами сброса первого и второго адресных счетчиков и с выходом установки триггера, вход сброса которого соединен с выходом блока анализа состояния ячейки, информационные входы которого являются информационными входами устройства, выход триггера является выходом чтения устройства и соединен с первым входом второго элемента ИЛИ, второй вход которого является входом записи-чтения устройства, выход второго элемента ИЛИ соединен с входом управляемого генератора, второй выход которого является выходом разрешения устройства, управляющий вход блока анализа состояния ячейки соединен с третьим выходом управляемого генератора, четвертый выход которого соединен с входами синхронизации первого и второго адресных счетчиков, «I

1 — .(,.i..w i=..fl

-1,.—,.3

L

- ч г

I аeeLL ooа ( П

3 ф . Г1 ., 1 и о@эL...(д Г Ц п..., п=г, L

1 L г — — — ..,П а - — ГЦ, . включение лила- дд щи I ,)" 1, ! жение 1ежлмакод и анализ игл и анализ 5 йО нейй 0 . мъж7ли

1 1 ю чие

I 4услай

1 Матчи

1 1

l i

,ЙОспчи l я. упблнениди учебки (37(ЖЩ/

i 1 1

@lJR g

- LL

1 о : з.

1 1 р- Сбой 6 одному одресньи 0ЬвруI

М .2:В Ю

Фиг. Ю

1667157

Редактор Н. Химчук

Заказ 2529 Тираж 348 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4f5

Производственно-издательский комбинат "Патент", r. Ужгород, ул.Гагарина, 101

Составитель М, Лапушкин

Техред M.Moðãåíòàë Корректор О, Ципле