Запоминающее устройство с автономным контролем

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для контроля запоминающих устройств. Целью изобретения является повышение достоверности контроля. Устройство содержит блок памяти 1, блок управления 2, группу сумматоров 3 по модулю два, первую и вторую группы триггеров 4, 5, сумматор 6, первый 7 и второй 8 счетчики. В устройстве осуществляется моделирование на элементах памяти накопителя генератора псевдослучайной последовательности. Устройство позволяет проводить контроль любых типов памяти произвольной выборки. 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (1 1) (s1)s 6 11 С 29/00

ГОСУДАРСТВЕ)+Ый КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ДРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4741281/24 (22) 14.08.89 . (46) 30.07.91. Бюл. М 28 (72) С.Л.Скалабан (53) 681.327.6 (088.8) (56) Авторское свидетельство СССР

N. 1472952, кл. G 11 С 29/00, 1987.

Авторское свидетельство СССР

М 1510013, кл. G 11 С 29/00, 1987. (54) ЗАПОМИНАК)ЩЕЕ УСТРОЙСТВО С

АВТОНОМНЫМ КОНТРОЛЕМ (57) Изобретение относится к вычислительной технике и может быть использовано для контроля запоминающих устройств. Целью изобретения является повышение достоверности контроля. Устройство содержит блок памяти 1, блок управления 2, группу сумматоров 3 по модулю два, первую и вторую группы триггеров 4, 5, сумматор 6, первый 7 и второй 8 счетчики, В устройстве осуществляется моделирование на элементах памяти накопителя генератора псевдослучайной последовательности. Устройство позволяет проводить контроль любых типов памяти произвольной выборки. 3 ил.

1667158

2О 5

ЗО

4О

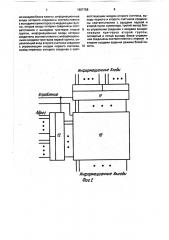

Изобретение относится к вычислительной технике и может быть использовано для контроля запоминающих устройств, Цель изобретения — повышение достоверности контроля, На фиг.1 представлена функциональная схема устройства; на фиг,2 — функциональная схема блока памяти; на фиг,3 -таблицы, поясняющие работу устройства.

Устройство (фиг,1) содержит блок памяти 1, блок управления 2, группу сумматоров

3 по модулю два, триггеры 4 первой группы, триггеры 5 второй группы„сумматор 6. первый счетчик 7, второй счетчик 8, На фиг,1 обозначен вход задания режима работы устройства 9.

Блок памяти 1 (фиг.2) состоит из контрслируемого накопителя 19, первого и второго мультипле":.Qopoâ 11, 12, Первый счетчик должен иметь коэффициент пересчета и, выбираемый из условия примитивности и неррояодимости полиномов Х"+Х+1 и X"+X + i, Блок управления 2 может быть реализован в виде автомата или микропрограммного устройства управления.

Информациончые выходы кснтролируеиого накопителя являются информационными выходами блока памяти 1, Входы первой группы первого мультиплексора 11 являются информационными входами Олока ffef«:и 1 (информация в режиме контроlf Я), В x o p f.-.f a т о р Q и г p y - f n u u e p a o r o мультиплексора 11 являются информационными входами в рабочем режиме. Выходы . первого мультиплексора (1 соединены с информационными входами контролируемого накопителя. Входы первой группы второго мультиплексора 12 являются адресными входами накопителя 10 (адрес в режиме контроля). Входы второй группы второго мультиплексора 12 являются адресными входами в рабочем режиме. ВыхОды втОрогО мультиплексора 12 соединены с адресными входами контролируемого накопителя, Управляющие входы контролируемого накопителя и мультиплексорсв "1, 12 Являются уг! раел яющими входа5ии ()йока памяти

Устройство работает следующим обраЗОМ, Рабочий режим.

С четвертого и пятого выходов блока 2 управления на управляющие входы блока памятг 1 поступают сигналы, которые переводят мультиплексоры 11 и 12 в режим приема сигналов со вторых входов. Таким образом, на адресные и информационные входы контролируемого накопителя поступают сигналы, соответствующие адресу и информации в рабочем режиме. Сигналы управления режимом работы контролируемого накопителя (запись, считывание, хранение) поступают также с выходов блока 2 управления, Режим контроля.

С четвертого и пятого выходов блока 2 управления на управляющие входы блока памяти 1 поступают сигналы, которые переводят мультиплексоры 11 и 12 в режим приема сигналов с первых входов. Таким образом, на адресные и информационные входы контролируемого накопителя поступают сигналы соответственно с выходов сумматора 6 и сумматоров 3 по модулю два.

С четвертого и пятого выходов блока 2 управления на управляющие входы блока памяти 1 поступает сигнал, который переводит контролируемый накопитель в режим чтения, С первого выхода блока памяти 1 на синхровходы триггеров 4 поступает синхроимпульс. Производится считывание информации, соответствующей текущей ячейке контролируемого накопителя в триггеры 4.

Текущая ячейка контролируемого накопителя определяется текущим состоянием счетчиков 7 и 8 и сумматором 6. С второго выхода блока 2 управления на управляющие входы счетчиков 7 и 8 поступает сигнал, устанавливающий режим "+1". Счетчик 7 переключается в следующее состояние. При наличии сигнала переноса на выходе счетчика 7 счетчик 8 также переключается в следующее "îñòîÿíèå. Таким образом, на адресных входах контролируемого накопителя устанавливается новый адрес, Определяемый состоянием счетчиков 7 и 8 и сумматором 6. С третьего выхода блока памяти 1 на синхровходы триггеров 5 поступает синхроимпульс. Производится считывание инфррмации, соответствующей текущей ячейке контролируемого накопителя в триггеры 5. С второго выхода блока 2 управления на управляющие входы счетчиков 7, 8 поступает сигнал, устанавливающий режим хранения. На информационных входах блока памяти 1 и соответственно контролируемого накопителя устанавливается информация, определяемая поразрядной суммой по модулю два содержимого триггеров 4, 5 в сумма орах 3 по модулю два. С четвертого и пятого выходов блока 2 управления на управляющие входы блока памяти

1 поступает сигнал, который переводит контролируемый накопитель в режим записи, Производится запись информации, присутствующей на информационных входах контролируемого накопителя 10 в текущую ячейку памяти.

Последовательность Операций, описанную в предыдущем абзаце, назовем шагом

1667158

10

55 первого этапа. Далее выполняется определенное число шагов первого этапа. С увеличением числа шагов первого этапа увеличивается достоверность контроля, На первом этапе контроля на элементах памяти блока памяти 1 моделируется генератор псевдослучайной последовательности, описанной полиномом Х"+Х+1, С выходов блока 2 управления на управляющие входы блока памяти 1 поступает сигнал, который переводит контролируемый накопитель в режим чтения. С первого выхода блока памяти 1 на синхровходы триггеров 4 поступает синхроимпульс, Производится считывание информации, соответствующей текущей ячейке контролируемого накопителя в триггеры 4.

Текущая ячейка контролируемого накопителя определяется текущим состоянием счетчиков 7 и 8 и сумматором 6. С второго выхода блока 2 управления на управляющие входы счетчиков 7 и 8 поступает сигнал, устанавливающий режим "-1", Счетчик? переключается в следующее состояние. При наличии сигнала переноса на выходе счетчика 7 счетчик 8 также переключается в следующее состояние, Таким образом, на адресных входах контролируемого накопителя устанавливается новый адрес, определяемый состоянием счетчиков 7, 8 и сумматором 6. С первого выхода блока памяти 1 на синхровходы триггеров 5 поступает синхроимпульс. Производится считывание информации, соответствующей текущей ячейке контролируемого накопителя в триггеры 5, С второго выхода блока 2 управления на управляющие входы счетчиков 7 и 8 поступает сигнал, устанавливающий режим "+1". Счетчик 7 переключается в следующее состояние. При наличии сигнала переноса на выходе счетчика 7 счетчик 8 также переключается в следующее состояние. Таким образом, на адресных входах контролируемого накопителя устанавливается новый адрес, определяемый состоянием счетчиков 7 и 8 и сумматором 6. На информационных входах блока памяти 1 и соответственно контролируемого накопителя устанавливается информация, определяемая поразрядной суммой по модулю два содержимого триггеров 4 и 5 в суммторах 3 по модулю два. С выходов блока 2 управления на управляющие входы блока памяти 1 поступает сигнал, который переводит контролируемый накопитель s режим записи.

Производится запись информации, присутствующей на информационных входах контролируемого накопителя в текущую ячейку памяти. Со второго выхода блока 2 управления на управляющие входы счетчиков 7 и

8 поступает сигнал, устанавливающий режим "-1", Счетчик 7 переключается в следующее состояние. При наличии сигнала в следуюгцее состояние, Таким образом, на адресных входа- контролируемого накопителя устанавливается новый адрес, определяемый состоянием счетчиков 7,и 8 и сумматором 6, Последовательность операций, описанную в предыдущем абзаце. назовем шагом второго этапа. Далее выполняется определенное число шагов второго этапа, Число шагов второго этапа должно быть равным числу шаго= первого этапа. На втором этапе контроля на элементах памяти блока памяти

1 моделируется генератор псевдослучайной последовательности, описываемой полино «Õ "+Х +1.

В конце второго этапа состояние ячеек блока памяти 1 и соответственно контролируемого накопителя должно соответствовать их состоянию до начала контроля s случае. если при контроле не пооизошла ошибка. Факт совпадения {несовпадениЯ) состояния ячеек памяти их состоянию до начала проверки говорит об отсутствии (наличии) ошибки.

В устройстве осуществляется моделирование ча элементах памяти накопителя генератора псевдослучайной последовательности, работа которого описывается полиномами X"+Õ+1 и X"+Õ" +1. Введение второго счетчика и сумматора обеспечивает то, что вышеуказанные полиномы будут примитивными и неприводимыми, Введение триггеров второй группы обеспечивает возможность контроля любых типов памяти произвольной выборки.

Формула изобретения

Запоминающее устройство с автономным контролем, содержащее блок памяти, первый счетчик, блок управления, первую группу триггеров, группу сумматоров по модулю два, первый выход блока управления соединен с входами синхронизации триггеров первой группы, выходы которых соединены соответственно с первыми входами сумматоров по модулю два группы; вход блока управления является входом задания режима устройства, второй выход блока управления соединен с управляющим входом

nepsoro счетчика, информационные выходы блока памяти соединены соответственно с информационными входами триггеров перВои группы и являются информационными выходами устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения достоверности контроля, в устройство введены вторая группа триггеров, второй счетчик и сумматор, выходы которого соединены с адресны1667158

Ин<рормсццанные Йормы ми входами блока памяти„информационные входы которого соединены соответственно с выходами сумматоров по модулю два группы, вторые входы которых соединены соответственно с выходами триггеров второй группы, информационные входы которых соединены соответственно с информационными входами триггеров первой группы, управляющий вход второго счетчика соединен с управляющим входом первого счетчика, выход переноса которого соединен с соответствующим входом второго счетчика, выходы первого и второго счетчиков соединены соответственно с входами первой и второй групп сумматора, третий выход бло5 ка управления соединен с входами синхронизации триггеров второй группы, четвертый и пятый выходы блока управления соединены соответственно с первым и вторым входами задания режима блока па10 мяти.

1667158

Редактор Н. Химчук

Заказ 2529 Тираж 345 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Я

Ь

3 Ф с

1 %

Ь . » ю Ъ

b (Ъ» с

Ъ

Ь

1 Ъ

Составитель M. Лапушкин

Техред M.Ìîðãåíòàë Корректор О. Ципле

Производственно-издательский комбинат "Патент", г. Ужгород, ул,Гагарина, 101