Устройство для контроля памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к запоминающим устройствам. Цель изобретения - повышение быстродействия устройства. Изобретение позволяет проводить проверку запоминающих устройств путем формирования сокращенных контролирующих тестов. Поставленная цель достигается введением в устройство третьего и четвертого регистров и группы элементов ИЛИ. Использование изобретения приводит к снижению времени проверки блоков памяти большой информационной емкости. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19у (11) (я)ю G 11 С 29/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) 739658 (21) 4745747/24 (22) 24.08.89 (46) 30.07.91. Бюл. М 28 .(71) Производственное объединение Комета" (72) В,С.Шевченко (53) 681.327 (088.8) (56) Авторское свидетельство СССР

3Ф 739658, кл. G 11 С 29/00, 1977, (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПАМЯТИ

Изобретение относится к запоминающим устройствам и является усовершенствованием изобретения по авт. св. М 739658.

Цель изобретения — повышение быстродействия устройства.

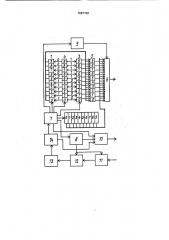

На чертеже изображена блок-схема устройства для контроля памяти.

Устройство содержит регистры 1-4, группу элементов ИЛИ 5, коммутатор 6, блок управления 7, блок формирования тестов 8, триггер 9, блок формирования импуль сов записи-чтения 10, приемный регистр 11, блок сравнения 12, блок останова 13, блок местного управления 14.

Разрядность адреса P проверяемой памяти состоит из разрядов регистра строк m и столбцов и в матрице памяти

P=m x n.

Для организации перебора адресов по кресту или строке (столбцу) в проверяющем тесте необходимо обеспечить воэможность автономного изменения соответствующей (57) Изобретение относится к запоминающим устройствам, Цель изобретения — повыше ни е быстродействия устройства1.

Изобретение позволяет проводить проверку запоминающих устройств путем формирования сокращенных контролирующих тестов. Поставленная цель достигается введением в устройство третьего и четвертого регистров и группы элементов ИЛИ. Использование изобретения приводит к снижению времени проверки блоков памяти большой информационной емкости. 1 ил. части m или и разрядов регистра адреса проверяемой памяти.

Разрядность всех четырех регистров 14, а также число элементов ИЛИ 5 и разрядность коммутатора 6 равны и соответствуют . максимально возможному числу разрядов д адреса для проверяемой памяти.

Разряды регистров 1 и 3 под воздействием выходов регистра 4 могут иметь два режима работы: счетный, если на их входы подается единичный потенциал с выхода со- . ответствующего разряда регистра 4 или ре- (Л жим принудительного удержания в единичном состоянии, которое не влияет на возможность работы в счетном режиме последующих разрядов данного регистра. Оба режима работы регистров 1 и 3 устанавливаются выходными потенциалами регистра

4, первый единичным, второй нулевым. При этом обеспечивается возможность счета, начиная с того разряда регистра, у которого первого имеется соответствующее разрешение. Таким образом задав позиционный

1667159 код в регистре 4, можно определить номер первого счетного разряда регистоов 1 и 3.

Устройство работает следующим ОбраЗОМ, При формировании адресных и Реходов типа крест из блока управления 7 на блок формирования тестов 8 и регистр 4 поступают установочные сигналы. Регистр 4 выдает на разряды регистров 1 и 3 единичные и нулевые уровни, например такие, как показано на чертеже: с прямых выходов 0-4 разрядов — единичные,nс :5-9 — нулевые(и наоборот, для инверсных выходов), На выходе разрядов регистров 1 и 3, принудительно установленных регистром 4 в режим удержания единичного состояния, присутствует "àêîé уровень, который разрешает прохождение через соответствующий элемент ИЛИ 5 группы сигналов того же разряда другого регистра, работающего в счетном режиме.

Проверка памяти начинается с исходного нулевого адреса, передаваемого коммутатором в регистр 2. На выходе элементов

ИЛИ 5 группы установлен адрес нулевогО столбца и первой строки. По сигналам из блоков управления 7 и формирования тестов 8 запускаются триггер 9 и блок формирования,импульсов записи-чтения 10, и по двум адресам, определяемым Регистром 2, Состаянием выходов элементов ИЛИ 5 группы и триггером 9, выполняется обращение, соответствующее данному тесту, Далее добавляется единица в регистр ", увеличивая адрес строки, и аналогичное Обращение производится по новой паре адресов.

АналОГичным Образом произвоДится обращение по остальным адресам нулевого столбца ДО Достиж8ниЯ регистром 1 аДреса, на единицу меньшего исходного, т.е. нулевого. Блок управления 7 прекращает добавление единицы в регистр 1 и начинается подача этих сигналов в регистр 3, который устанавливается в состояние адреса первогс столбца. После обращения по данной новой паре адресов произ одится обращение по другой паре адресов, отличающейся состоянием регистра 3 (адрес второго столбца), и т,д. до достижсния регистром 3 исходного состояния, равного ссстоянию регистра 1. Первый такт формирования адресных переходов оканчивается увеличением на еДиницу состОяниЯ р8Гистра 2 (происходит сдвиг, центра креста). Второй и последующие такты производятся аналоГично с добавлением единицы в реГистры 1 и 3 дО достижения ими исхОднОГО cocTQAния, равного состоянию части и регистра 2 для регистра 3 и части m регистра 2 для регистра 1. Характер обращения по каждому из адресов в проверяемой паре определяется блоком формирования импульсов записи-чтения 10, а обращенные к тому или иному адресу в паре — триггером 9 в зависимости от типа теста.

При необходимости изменения разрядности регистров из блока управления 7 в регистр 4 поступают сигналы на изменение состояния его разрядов.

Для формирования адресных переходов внутри строки или столбца в такте обращения перебор адресов производится только одним из регистров 1 или 3, второй же постоянно находится в состоянии, равном состоянию соответствующей части m или и регистра 2.

При формировании адресных переходов для тестов типа N2, где N=2,, разряды регистра 4 из блока управления 7 устанавливаются в одинаковое состояние и работает один из регистров 1 или 3 по полному объему адресов, образуя адрес, парный адресу регистра 2. Добавление единицы производится только в тот регистр 1 или 3, который работает в режиме счета.

Считанная из проверяемого блока памяти информация принимается на регистр

11, сравнивается с эталонной в блоке сравнения 12, который при наличии несовпадения запускает блок останова 13. Сигнал иэ блока останова 13 прекращает работу блока местного управления 14.

Устройство позволяет формировать более короткие тесты N, что приводит к снижению времени проверки блоков памяти большой информационной емкости.

Формула изобретения

Устройство для контроля памяти по авт. св. В 739658, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, в него введены третий и четвертый регистры адреса и группа элементов ИЛИ, причем выходы первого регистра адреса через первые входы элементов ИЛИ группы подключены к первому входу коммутатора, вторые входы элементов ИЛИ группы соедииены с выходами разрядов третьего регистра адреса, входы которого поразрядно соединены с инверсными входами четвертого регистра адреса, прямые выходы которого поразрядно соединвны с входами первого регистра адреса, вход четвертого регистра адреса подключен к одному из выходов блока управления.

1667159