Преобразователь двоичного кода в двоично-десятичный код и обратно

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может использоваться в цифровых информационно-вычислительных и управляющих системах. Преобразователь осуществляет прямое и обратное преобразование двоичного и двоично-десятичного кодов и формирование унитарного кода. При выполнении преобразователя на микросхемах серии К 555 количество используемых микросхем уменьшается на четыре корпуса, что позволяет упростить преобразователь. Преобразователь содержит элементы И - НЕ 1, 4 - 7, 9, 10, 18, формирователь 2 импульсов, элементы НЕ 3, 15, 16, 19, блок 11 двоично - десятичных счетчиков, блок 13 двоичных счетчиков. 2 ил.

C:Î1 13 СОЕ ЕТСКИХ

СО ИАЛИС ТИНЕ С К ИХ

PFСПУБЛИК

ГОСУДАРСТБЕННЫИ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

<1PI ГКНТ ГССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ 7

7 (21) 4747940/24 (22) 09.10.89 (46) 30.07.91, Бюл. N. 28 (71) Украинский научно-исследовательский институт станков и инструментов (72) И.Ю.Шнайдер и Л.В.Ганнель (53) 681.325 (088.8) (56) Приборы и техника эксперимента, 1982, М 2. с, 76-78.

Авторское свидетельство ГССР + 1229966, кл. Н 03 M 7/28, 1982. (54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КО

ДА В ДВОИЧНО-ДЕСЯТИЧ 4bliil КОД И ОЬРА ТНО (») Изобретение относится к импульснс

ТЕХНИКЕ И МпжЕГ ИГПОЛЬЗОВатЬСЯ В ЦИ->РО, ... ЙЛ, „1667260 А1 вых информационно-вычислительных и управляющих системах. Преобразователь осуществляет прямое и обратное преобразования двоичного и двоично-десятичного кодов и формирование унитарного кода. При выполнении преобразователя на микросхемах серии К 555 количество используемых микросхем уменьшается на четыре корпуса, что позволяет упростить преобразователь. Преобразователь содержит элементы И- НЕ 1,4 — 7, 9, 10, 18, формирователь 2 импульсов, элементы НЕ 3, 15, 16. 19, блок 11 двоично-десятичны, счетчиков бл, к 13 двоичных сче:ик; з. 2:;n.

1667260

Изобретение оносится к импульсной технике и может быть использовано в цифровых информационно-вычислительных и управляющих системах.

Целью изобретения является упрощение преобразователя.

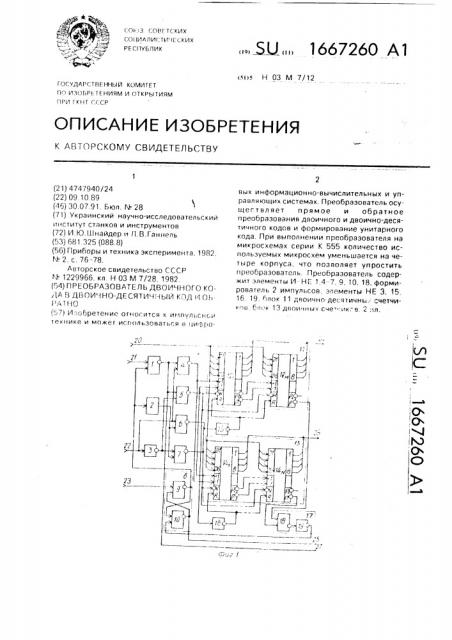

На фиг, 1 представлена функциональная схема преобразователя; на фиг. 2 — временные диаграммы, поясняющие его работу.

Преобразователь (фиг. 1) содержит пятый элемент И-НЕ 1, формирователь 2 импульсов, первый элемент НЕ 3, первый, третий, второй, четвертый элементы И-НЕ

4-7, триггер 8, выполненный на элементах

И-НЕ 9, 10, блок 11 двоично-десятичных счетчиков 121 — 12, блок 13 двоичных счетчиков 141-14г, второй, третий элементы НЕ

15, 16, элемент И 17, выполненный на элементе И вЂ” НЕ 18 и элементе НЕ 19, информационные входы 20, тактовый вход 21, вход

22 выбора режима, вход 23 "Пуск", выходы

24 двоично-десятичного кода, выходы 25 двоичного кода, выход 26 готовности u Btl ход 27 унитарного кода.

Преобразователь работает следующим образом.

Режим преобразования задается подачей на вход 22 уровня логического "0" для преобразования двоична-десятичного в двоичный код и уровня логической "1" для преобразования двоичного в двоично-десятичный код. В зависимости от режима преобразования при помощи формирователя 2, элементов И-НЕ 5, 6 происходит запись входной информации в соответствующий блок 11 или 13 счетчиков и обнуление сче1чиков блока 13 или 11, выдающих выходнои код, с последующим их заполнением.

8 качестве примера рассмотрим преобразование двоичного кода в двоично-десятичный.

8 исходном состоянии триггер 8, образованный элементами И-НЕ 9, 10, сброшен и уровень логического "0" с его первого выхода поступает на вход формирователя 2

После подачи уровня логического "0" на вход "Пуск", соответствующего отрицательному фронту тактовых импульсов, трипер 8 устанавливается в единичное состояние. Коротким импульсом с выхода формирователя

2 производится запись установленных на входах 20 данных, представленных в двоичном коде, в счетчики 14 и сброс счетчиков

12. Единичным уровнем с выхода элемента

И вЂ” НЕ 9 разрешается прохождение через элемент И-НЕ 1 тактовых импульсов, которые поступают на входы элементов И вЂ” НЕ 4, 5 и затем с выхода элемента И вЂ” НЕ 4 на вход сложения счетчика 121 и вход вычитания

50 счетчика 141. По каждому положительному перепаду тактовых импульсов происходит увеличение на единицу содержимого счетчиков 12 и уменьшение на единицу содержимого счетчиков 14. Процесс счета продолжается до тех пор, пока на выходе заема ("P- ) счетчика 141ч не появится уровень логического "0", свидетельствующий об обнулении счетчиков 14, который через элемент И 17 сбрасывает триггер 8 в исходное состояние. На выходе элемента И- НЕ

10 получен сигнал об окончании преобразования (готовности данных). Содержимое счетчиков 12 равно записанному числу в двоично-десятичном коде, B процессе счета на выходе элемента И НЕ 1 формируется унитарный код. Преобразование двоичнодесятичного кода в двоичный происходит анало ично.

На фиг. 2 представлена временная диаграмма при преобразовании 1исла "4" из двоичного кода II двоично-десятичный и 06ратно

На вход 21 поступают так овые импульchI, на входе 22 присутгтвует уровень логического "0" либо "1, свидетельствующий о режиме преобразования, неизменный на время преобразования. Появление нулевого уровня сигнала на входе 23 приводит к запуску преобразователя, т.е, к появлению единичного уровня на выходе элемента ИHF 9 и короткого импульса на выходе формирователя 2.

При поступлении положительного фронта тактового импульса происходит изменение содержимого счегчиков 12, 14. По отрицательному перепаду етвертого такто вого импульса на выходе элемента 11 17 появляется единичный уровень, который приводи г к сбросу триггера 8, блокирующего работу преобразователя до поступления следующего уровня логического "0" на вход

23.

Преобразователь выполнен на следующих микросхемах; двоичные счетчики 14-К555ИЕ6, двоично-десятичные счетчики 12—

К555ИЕ7, элемента И-НЕ К555ЛАЗ, элементы НŠ— К555ЛН1. Таким образом, преобразователь, кроме реверсивных счетчиков, имеет два корпуса К555ЛАЗ и один корпус К555ЛН1, независимо от количества разрядов преобразуемого кода, т.е, позволяет уменьшить количество используемых микросхем на четыре корпуса.

Формула изобретения

Преобразователь двоичного кода в двоично-десятичный код и обратно. содержащий блок двоично-десятичных с-1етчиков и

1667260 блок двоичных счетчиков, информационные входы которых являются информационными входами преобразователя, первые выходы блока двоично-десятичных счетчиков и блока двоичных счетчиков соединены соот- 5 ветственно с первым и вторым входами элемента И. вторые выходы являются соответственно выходами двоично-десятичного кода и выходами двоичного кода преобразователя, элементы НЕ, первый- 10 четвертый элементы И-НЕ, вход первого элемента НЕ объединен с первыми входами первого и второго элементов И-HE и является входом выбора режима преобразователя, выход первого элемента НЕ соединен с 15 первыми входами третьего и четвертого элементов И-НЕ, выходы первого и третьего элементов И вЂ” НЕ соединены соответственно с суммирующим и вычитающим входами блока двоично-десятичных счетчиков, 20 формирователь импульсов и триггер, о тл и ч а ю шийся тем, что, с целью упрощения преобразователя, в него введен пятый элемент И вЂ” НЕ, первый вход которого является тактовым входом преобразователя, вы- 25 ход пятого элемента И вЂ” НЕ соединен с вторыми входами первого и третьего элементов

И-НЕ и является выходом унитарного кода преобразователя, выход элемента И соединен с первым входом триггера, второй вход которого является входом пуска преобразователя, первый выход триггера соединен с вторым входом пятого элемента И вЂ” НЕ и входом формирователя импульсов, выход которого соединен с вторыми входами второго и четвертого элементов И-НЕ, второй выход триггера является выходом готовности преобразователя, выход второго элемента И—

НЕ соединен непосредственно с управляющим входом блока двоичных счетчиков и через второй эле ент НŠ— с установочным входом блока двоично-десятичных счетчиков, выход четвертого элемента И—

НЕ соединен непосредственно с управляющим входом блока двоично-десятичных счетчиков и через третий элемент НЕ с установочным входом блока двоичных счетчиков, вычитающий и суммирующий входы которого подключены к выходам соответственно первого и третьего элементов И вЂ” HE.