Способ измерения линейных перемещений и устройство для его осуществления

Иллюстрации

Показать всеРеферат

Изобретение относится к измерительной технике. Цель изобретения - повышение точности за счет уменьшения дрейфа нуля интегратора в условиях времяимпульсной выдачи данных. В ходе измерений на вход интегратора 8 подается нулевое напряжение с шины "0". Уровень смещения нуля запоминается аналоговым запоминающим блоком 16, сигнал с выхода которого через фазоинверсный усилитель 17 подается на вход интегратора 8, предотвращая интегрирование напряжения смещения. Процесс происходит до поступления импульса с задатчика 12 выдачи данных на вход одновибратора, устанавливая на его выходе уровень логической единицы, что обеспечивает повторное интегрирование сигнала с резистивного датчика 1 с учетом дрейфа нуля и определение нового значения, фиксируемого до перемещений счетчиками 13 и 14 в течение работы устройства. 2 с.п.ф-лы, 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (si)s G 01 В 7/04

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) 1563729 (21) 4659245/28 (22) 06,03,89 (46) 15,08.91. Бюл. !4 30 (72) В,Н.Милютин и Б.Л.Николаенко (53) 531.717(088.8) (56) Авторское свидетельство СССР

N 1563729, кл, 6 01 В 7/04, 1988. (54) СПОСОБ ИЗМЕРЕНИЯ ЛИНЕЙНЫХ

ПЕРЕМЕЩЕНИЙ И. УСТРОЙСТВО ДЛЯ ЕГО

ОСУЩЕСТВЛЕНИЯ (57) Изобретение относится к измерительной технике. Цель изобретения — повышение точности за счет уменьшения дрейфа нуля интегратора в условиях времяимпульсной выдачи данных. В ходе измерений на!

Ж 1670365 А2 вход интегратора 8 подается нулевое напряжение с шины "0". Уровень смещения нуля запоминается аналоговым запоминающим блоком 16, сигнал с выхода которого через фазоинверсный усилитель 17 подается на вход интегратора 8, предотвращая интегрирование напряжения смещения. Процесс происходит до поступления импульса с задатчика 12 выдачи данных на вход одновибратора устанавливая на его выходе уровень логической единицы, что обеспечивает повторное интегрирование сигнала с резистивного датчика 1 с учетом дрейфа нуля и определение нового значения, фиксируемого до перемещений счетчиками 13 и 14 в течение работы устройства. 2 с.п.ф-лы. 3 ил.

1670365

Изобретение относится к измерительной технике, может быть использовано в информационно-измерительных системах и я вляется усовершенствованием изобретения по авт.св. N 1563729.

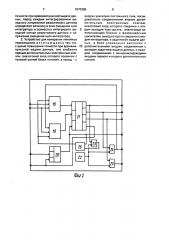

Цель изобретения — повышение точности путем уменьшения дрейфа нуля интегратора в условиях времяимпульсной выдачи данных, На фиг.1 представлена схема устройства, реализующего способ измерения линейных перемещений; на фиг,2 — блок управления, вариант выполнения; на фиг.3 — временные диаграммы работы устройства.

Устройство, реализующее способ, содержит реэистивнй датчик 1, блок 2 питания, шины "0" и "А" которого соединены с неподвижными выводами резистивного датчика 1, четыре электронных ключа 3 — 6, аналоговые входы которых соединены соответственно с подвижным выводом резистивного датчика 1 и шинами "В", "С" и "0" блока 2 питания, последовательно соединенные усилитель 7 постоянного тока, вход которого соединен с выходами электронных ключей 3 — 6, интегратор 8, компаратор 9. второй вход которого соединен с шиной "С" блока 2 питания, и блок 10 управления, первые три выхода которого соединены с синхронизирующими входами соответствующих ключей 3 — 5. Устройство содержит нуль-орган 11, входы которого соединены с выходом интегратора 8 и шиной "0" блока 2 питания, а выход — с вторым входом блока 10 управления, соединенный с его третьим входом эадатчик 12 выдачи данных, первый и второй счетчики 13 и 14, счетные входы которых соединены соответственно с четвертым и пятым выходами блока 10 управления, а обнуляющие входы — с шестым выходом блока 10 управления и последовательно соединенные пятый электронный ключ 15, аналоговый вход которого соединен с вторым входом нуль-органа 11, а синхронизирующий вход — с синхронизирующим входом четвертого электронного ключа 6 и седьмым выходом блока 10 управления, аналогово запоминающий блок 16 и фазоинверсный усилитель 17, выход которого соединен с входом интегратора 8.

Блока 10 управления может быть выполнен в виде первой схемы 3 ИЛИ 18, первые два входа которой представляют собой первый и второй входы блока 10 управления, второй схемы 3 ИЛИ 19, первый вход которой соединен с первым входом схемы 3

ИЛИ 18, одновибратора 20, вход синхронизации которого представляет собой третий вход блока 10 управления. Блок 10 содер5

55 жит регистр 21 сдвига, управляющий, синхронизирующий и установочный входы которого соединены соответственно с выходами первой и второй схем 3 ИЛИ 18 и 19 и одновибратора 20. Первые три выхода представляют собой соответствующие выходы блока

10 управления, а четвертый — седьмой выход и соединен с R-входом одновибратора 20, который может быть выполнен в виде RSтриггера, генератора 22. трех схем 2 И 23—

25, первые входы которых соединены с выходом генератора 22, вторые — с соответствующими выходами регистра 21 сдвига.

Выход второй схемы соединен с вторым входом второй схемы 3 ИЛИ 19 и представляет собой четвертый выход блока 10 управления, а выход третьей схемы представляет собой пятый выход блока 10 управления, Блок 10 управления содержит дополнительного счетчика 26, установочный вход которого соединен с выходом одновибратора

20 и представляет собой шестой выход блока 10 управления, счетный вход — с выходом первой схемы 2 И 23, а выход — с третьими входами схем 3 ИЛИ 18 и 19, напряжения через времязадающую цепочку.

Спосо реализуется следующим образом.

При включении питания на установочный вход одновибратора 20 подается импульс, устанавливающий на выходе одновибратора 20 напряжение логической единицы, поступающей на установочные входы регистра 21 сдвига и счетчика 26, а через выход — на обнуляющие входы счетчиков 13 и 14.

При поступлении логической единицы на установочный вход регистра 21 сдвига на его первом выходе устанавливается логическая единица, а на остальных выходах— логические нули. При поступлении импульсов на обнуляющие входы всех счетчиков 13 и 14 они устанавливаются в состояние, при котором с их выходов снимаются логические нули, Предполагается также, что при включении интегратор 8 устанавливается в нуль, Вследствие наличия на первом выходе регистра 21 логической единицы, которая присутствует также на входе электронного ключа 3, после включения питания напряжение с подвижного вывода резистивного датчика 1 через усилитель 7 поступает на интегратор 8.

Под воздействием напряжения, снимаемого с резистивного датчика 1, интегратор

8 заряжается до напряжения 0, (на фиг.3 показаны два напряжения U> и U2, причем диаграмма для U2»>, показана пунктиром).

В укаэанном состоянии электронные ключи

1670365

4 — 6 и 15 после включения закрыты длч прохождения через них напояжений.

Логическая единица с первого выхода регистра 21 подается также на вход схемы

2 И 23, на другой вход которой подаются импульсы с частотой f от генератора 22.

Пропущенные через схему 2 И 23 импульсы поступают нл счетный вход счетчика 26. Таким обр зсм, с началом интегрирования >iaп ряжения резистивного датчика 1 начинается и одновременный счет кол «ества импульсов, следующих с частотой f на вход счетчика 26. Количество импульсов, на которое рассчитан сче -«ик 26, определяет длительность первого такта интегрирования

После подсчеTà Оitpeäåëeнного количества импульсов нл вь«ходе счет икл 26 поянляегся логическая ед;«ница. >(Qropaот поступать импульсы с частотой f на че нертый выход блока 10 у fpaafte><«f« и далее на счегнь!й вход сче-, «> кл 13.

Ввиду смещения урсь«:, - »ической единицы Г перво; о fir «орой них д регистра 21 клю" 3 v схе>«л 2 И 2 l буду злкрыт>.. дл. (lprf о кденич .: н,»«с:: С м(«м н«3 <11— крь<>«3>«ич t n о «л 1 >«; «и;«-«Tc>I разряд и, <теграТор3 8 от ш. ньi "H . полярнсь»:, о ого проти><;>пс «ожна . змерче;-«о.1у «лпр< ч ению. Рлзр><д интегратора Я длится до по," т у . «л e H u s u e p н о Г с 1 M и у л ь с 3 «л Г I О l t.l с моме>< гл срабатывания l(0Mflaparup3 9.

Cp3á3Tынание ко;.«плрлторл 9 происходит при рлн"tfcTBe н, прчжений поданлемых «Iл комп:paTop от IU!1««t! С !1 or интогpal ора 8, В MQMÃI«T рлгellc l вл >«аг«рч;t,eH: i, ксмплратор 9 н.<рлбатынлет импульс, ко гор< «и пода сч нл cxeму 3 ИГ1И 8 и дэлен Hл упрлнлчюн,и.1 Гкод рсru стра 21.

Е резун Г«аTе пес«уплc «>1В уIlольлR с цеiо и

Г21>i/poHèзируюlNcго сигHB,<3 ???? ?????? t i!1???? 26 ????????????-.?????? ?????????????? ?? ???????? ???? ???????????? ?? ???????????? 21 ???????????????????? l??3 ???? ????> вых(,q. На этом . lQpQ.1 глкт интегрирования зл лнчинаетсч и Од> QBpeMpHHQ >«л «и! «лстГч Tpe1и ч такт ин гегриронания, в проце,се которого через ключ 5 нл нход и>«тегрл«орл 8 по .. уi àeт 1«3«рчжение с вых )дл шины С блокэ у питани>«и ogHQBpeMенно импульсы с ныход:-

ie>«ep3Tnp3 22 «cpaç сxeM;. 2 VI 25 и пч гый выход блока 10 управления !Iocryr«3>QT ila с <етнь!й вход (. «етчикл 1 1 > pf «H -; такт осуU(e(:TBë. eTc.-. при нл,iè÷!I>I лс. ич -.> Qи единицы На входе ключа 5 и входе схем ч 2 И 24.

4()

1Г

r;0

По достижении напряжения равного нулю, срабатывает:чуль-орган 11. при этом импульс нуль-ор аНа 1>1 через блок 10управления и схемы 3 ИЛИ 18 и 19 поступает на управляющий вхо,;, и синхронизирующий вход регистра 2 >. обеспечивая при этом сдвиг логической единицы с третьего на четвеотый выход. С выхода четвертогс регис-ра 21 логическая единица <«оступает на вход

opI:овибратора 20, на выходе которого устаH3Bë> Baåòñÿ нулевой поiåíöèaë, а через седьмой выход блока 10 управления — на входы синхронизации ключей 6 и 15.

Ключ 5 и схел а 2 И 25 в указанный моме:-т времени закрывлютсч для прохсуждени через >I ;х сигналов Тре- ии такт

;1t: «ч рирования при этом заканчивается.

Пр!1 открытых ключах г; 15 на вход интегр;ilopa Ь подается нлпрч.кение с ши> ы "0", на l.ofopoA присутствует ну. евой потенци,.«л, =- выход интегратора 8 через вход и второй выход нуль-ор«лна 11 подключается к входу 3 «алсгового запоминающего блока

16. который фиксирует yposetiB нлг«ряжения

fi3 выходе интегратора.

" учего 1 гого, что на вход интегратора

Ь подаетсч нулено<. лпрчжение с Гви»ы 0", re,:,«выходе интегратора н уклзанном сосг(учнии определяется уровень смещения

Hy»>I. который фиксирует(.ч лналогоным заи(.;и>«лющим блоком «б, С eio выхода На>«р жение cMО це",ич нуля "ере4. 32oI1H Be PcH BtI1 усили1 ель 1 7 oсдаетсч На нх..д интегратора 8, предствращач пр,1 этом и> те«p!.poaàHèå напряжения смещения, каз;«нное состо IH!«e длится. до поступления им««ульсл с выхода задат If<> .3 1 Bt«раЧ<1 ????> >IЫХ (B Клчвв, 3З ЗЛДЛ ЧИК3 МОХСТ .;Гпользонаться BHBL нее устройство;, кстор>»ll! ппступле. нл вход однснибратора 20, у: лнлнлинач на,.го выходе состсчние логич,.Гкой единицы При =-том Обе=ï-;e÷ fнается поь«(>Оное»-«тегрир2нлние î rt«ofo сигнала резистинно>О дл, чика 1 с учетом смеще«н; >«уля интегрл«орл и сг;реде, B,—,ия нового

t л «;,«ич и заф«1кьирова>«>-.сгс: дс перемеш, IIIII с «етчикл>ли 13, 1л и Т.д B iå÷åí«е длительнссти всей (лбсть«ус>ройс-,н :

Применение предгл>лемых сгособл изм«. ре>««1ч линейнь:х перемещен.«й и устройCri= ДЛЯ ЕГ < PeaÃ.!133Ö!fÈ ОбЕСПЕЧИВаЕт ком(«еl .слцию cloiрсшнссти >lзмерений, Обусловленную дреифоM нуля и> Teãðàòîðà.

В результате понышлетсч TQ .HQETb измерения линейных перемещений, Формула изобретения

1, Спссоб измерения линей>«ых перемеще>.IIII по лвт.cB»: ".563729 .= .. л и .. г ощ >1 и с я тем -.lu c целью повышения

1670365 точности при времяимпульсной выдаче данных, перед каждым интегрированием выходного напряжения резистивного датчика определяют величину и знак смещения нуля интегратора и совместно интегрируют выходной сигнал резистивного датчика и напряжение смещения нуля интегратора.

2. Устройство для измерения линейных перемещений, о т л и ч а ю щ е е с я тем. что, с целью повышения точности при времяимпульсной выдаче данных, оно снабжено первым дополнительным электронным ключом, аналоговый вход которого соединен с нулевой шиной блока питания, а выход — с входом усилителя постоянного тока, последовательно соединенными вторым дополнительныM электронным ключом, аналоговый вход которого соединен с вто5 рым выходом йуль-органа, аналоговым запоминающим блоком и фазоинверсным усилителем, выход которого соединен с входом интегратора, и задатчиком выдачи данных, а блок управления выполнен с

10 дополнительными входом, соединенным с выходом задатчика выдачи данных, и выходом, соединенным с синхронизирующими входами первого и второго дополнительных ключей.

1670365

РагЗ

Редактор С. Лисина

Заказ 2736 Тираж 370 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035. Москва, Ж-35, Раушская наб„4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

Ц, Ь

Составитель Ю. Круглов

Техред М,Моргентал Корректор М. Кучерявая