Устройство для спектрального анализа

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и предназначено для спектрального анализа широкополосных детермированных и случайных сигналов. Цель изобретения - повышение точности измерения - достигается введением многовходового сумматора, усилителя-ограничителя, дифференциатора, диода, блокинг-генератора, переключателя, трансформатора напряжений, фильтра нижних частот, квадратурного фазовращателя, блоков запуска и останова, двух блоков аналоговых ключе, триггера и счетчика. Устройство также содержит блок преобразования, включающий в себя квантователи, блок памяти, включающий в себя ячейки, матрицы, коммутатор, генератор импульсов, блок установки шага дискретизации. Каждая из вычислительных ячеек содержит суммирующие усилители, резисторы. Многовходовый сумматор содержит суммирующий усилитель и резисторы. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)5 G 01 R 23/16

ГОСУДАРСТВЕННЫЙ KOMPITET

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ 4

О

О (61) 1083124 (21) 4300764/21 (22) 31.08.87 (46) 15.08.91. Бюл. ¹ 30 (71) Ленинградское высшее инженерное морское училище им. адм.С.О,Макарова (72) Б,Е.Синдаловский, С.С.Березин, В.П,Пиастро и Е.Б,Синдаловская (53) 621.317(088.8) (56) Авторское свидетельство СССР

¹ 1083124, кл. G 01 R 23/16, 1983. (54) УСТРОЙСТВО ДЛЯ СПЕКТРАЛЬНОГО

АНАЛИЗА (57) Изобретение относится к вычислительной технике и предназначено для спектрального анализа широкополосных детерминированных и случайных сигналов.

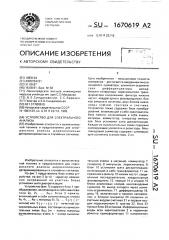

Изобретение относится к вычислительной технике и предназначено для спектрального анализа широкополосных детерминированных и случайных сигналов, На фиг.1 представлена блок-схема устройства; на фиг.2 (а — и) — характер изменения напряжений на участках блока установки шага дискретизации.

Устройство (фиг.1) содержит блок 1 преобразования, включающий в себя квантователи 2о, 21, ..., 2g-I, блок 3 памяти, включающий в себя запоминающие ячейки

4о, 41, ..., 4ы-I, матрицы 51, 52...., 5 y/р (учетное) или 5 (у — 1)/2 (у — нечетное) вычислительных ячеек, состоящих из вычислительных ячеек 6m,I (m — номер матрицы вычислительных ячеек; М вЂ” номер вычисли. Ы „1670619 А2

Цель изобретения — повышениме точности измерения — достигается введением многовходового сумматора. усилителя-ограничителя, дифференциатора, диода, блокинг-генератора, переключателя, трансформатора напряжений, фильтра нижних частот, квадратурного фаэовращателя, блоков запуска и останова, двух блоков аналоговых ключей, триггера и счетчика.

Устройство также содержит блок преобразования, включающий в себя квантователи, блок памяти, включающий в себя ячейки, матрицы, коммутатор, генератор импульсов, блок установки шага дискретизации.

Каждая иэ вычислительных ячеек содержит суммирующие усилители и резисторы, Многовходовый сумматор содержит суммирующий усилитель и резисторы. 2 ил. тельной ячейки в матрице), коммутатор 7, генератор 8 импульсов, переключатель 9, блок 10 установки шага дискретизации, включающий в себя трансформатор 11 напряжения и фильтр 12 низких частот, соединенные последовательно, квадратурный фаэовращатель 13, первый 14 и второй 15 блоки аналоговых ключей, многовходовый сумматор 16, выход которого через усилитель-ограничитель 17, дифференциатор 18, диод 19, включенный в прямом направлении, и блокинг-генератор 20 соединен со счетным входом счетчика 21 и первым входом переключателя 9, триггер 22, блок 23 пуска и блок 24 останова, Информационные входы всех квантователей 2 и первичная обмотка трансформатора 11 напряжения

1670619 соединены с входом устройства. Управляющие входы квантователей 2 соединены с выходами коммутатора 7, а информационные выходы соединены с входами запоминающих ячеек 4. Второй вход переключателя 9 соединен с входом коммутатора 7. Выход фильтра 12 низких частот соединен через квадрэтурный фазовращатель 13 с информационным входом первого блока 14 аналоговых ключей и непосредственно с информационным входом второго блока 15 аналоговых ключей. R- u S-входы триггера 22 соединены соответственно с блоком 23 пуска и блоком 24 останова, э

С1-выход соединен с разрешающими входами счетчика 21, первого 14 и второго 15 блоков аналоговых ключей, Выходы разрядовсчетчика 21 соединены суправляющими входами первого 14 и второго 15 блоков аналоговых ключей.

Каждая вычислительная ячейка восьмивходовая и выполнена в виде двух семивходовых суммирующих усилителей 25 и 26 с резисторами 27 и 28 обратной связи и резисторов, включенных между первым — восьмым входами вычислительной ячейки и неинвертирующими и инвертирующими входами суммирующих усилителей 25 и 26.

Многовходовый сумматор 16 выполнен в виде суммирующего усилителя 29, резистора

30 обратной связи, резисторов 31,32 и т.д., включенных между выходами первого блока

14 аналоговых ключей и инеертирующим входом суммирующего усилителя 29. резисторов 33,34 и т.д., включенных между выходами второго блока 15 аналоговых ключей и неинвертирующим входом суммирующего усилителя 29.

Сигналы, пропорциональные амплитудам ортогональных составляющих комплексного спектра. снимаются с вычиСлитЕльных ячЕЕк 61,0, 61,1, ..., 61,N-1 первой от выхода матрицы 51.

Каждая из первых трех вычислительных ячеек 610, 611, 612 матрицы 51 связана с четырьмя первыми вычислительными ячейками 62,0, 62,1, 62,2. 62,3 второй матрицы 52. а каждая последующая пара вычислительных ячеек 613, 61,4, 61,6 616 матрицы 51 связана со всеми вычислительными ячейками последующей четверки ячеек 62,4, 62,5, 626, 62 7, бг,в, бг,в, 62,10, 62,»; ... матрицы 52, одновременно у остальных матриц вычислительных ячеек каждая k-я вычислительная ячейка предыдущей матрицы в пределах периода повторения связей двух соседних матриц по их высоте соединена с (р2) и вычислительными ячейками последующей матрицы (3

2,3... — номер той иэ рассматриваемых двух матриц, которая ближе к выходу устройства

n = 0,1,2...), причем k-я вычислительная ячейка последней матрицы связана с k и k+ N/2 запоминающими ячейками блока 3 памяти при log2N — нечетном и с Е ц N/4

5 цп запоминающими ячейками блока 3 памяти при log2N — четном, а период повторения связей по высоте матрицы равен 4m (пт— номер вычислительных ячеек).

В основе устройства лежит вычисли10 тельная ячейка, которая выполняет операции вида

А = А1 + А2 ехр (— ) угг ) + Аз ехр (— j ) +

+ A4 exp (— j (p4 )

15 где А1, Аг, Аэ, А4 — комплексные числа, характеризующие сигналы, подводиммые к ячейке;

А — комплексное число, характеризую20 щее результат вычислений;

pz, 1Ъ, р4 углы поворотов Аг, Аэ, А4 соответственно, Семивходовые суммирующие усилители 25 и 26 вычисляют величины вещественной и мнимой частей комплексного числа А.

Истинные знаки весовых коэффициентов учитываются за счет подключения взвешивающих резисторов к инвертирующему или неинвертирующему входам суммирующего усилителя.

Углы фг, фз, р4 поворота векторов Аг, Аэ, А4 связаны с числом дискретных отсчетов исследуемого сигнала соотношением

2 7Г Р= где k1- 0,1„„,N — 1 — число, характеризующее рассматриваемую вершину графа.

Устройство содержит - N вычисли2

40 Ът тельных ячеек, которые обьединены в матриц по N вычислительных ячеек в каждой матрице, если у — четное число, и у — 1

45 2 — — — — N вычислительных ячеек, которые j обьединены в матриц по Ы вычиспи2 тельных ячеек в каждой матрице, если у— нечетное (N — число дискретных отсчетов

50 исследуемого сигнала, N = 2 y), Устройство для спектрального анализа реализует модифицированный алгоритм быстрого преобразования Фурье. В процессе анализа входной сигнал дискретизируется с шагом

Лт=

Т

N где T - период входного сигнала.

1670619

Шаг дискретизации устанавливается автоматически блоком 10 установки шага дискретизации в строгом соответствии с периодом входного сигнала, при этом N paa реализуется соотношение / s r (vent - v ) = U„, Г! d t co s ч Ц,, с05 << 5 и+

Значения cos tj и sin g постоянные на каждом шаге, задаются соответственно с помощью весовых резисторов

33, 34 и 31. 32.

Устройство работает следующим образом.

Аналоговый входной сигнал поступает на информационные входы квантователей 2 блока 1 преобразования и на первичную обмотку трансформатора 11 напряжения.

Фильтр 12 низких частот выделяет первую (либо другую) гармонику входного сигнала.

Синусоидальное напряжение Umsin вт прикладывается к информационному входу второго блока 15 аналоговых ключей и к входу квадратурного фаэовращателя 13, который сдвигает фазу синусоидального напряжения на угол г/2. Напряжение

Umcos и)т прикладывается к информационному входу первого блока 14 аналоговых ключей (фиг.2д).

При измерении ортогональных составляющих комплексного спектра входного сигнала на R-вход триггера 22 от блока 23 пуска поступает отрицательный импульс, переводя триггер 22 в положение "0" (фиr.2а).

С О-выхода триггера 22 к разрешающим входам счетчика 21, первого 14 и второго 15 блоков аналоговых ключей прикладывается положительное "разрешающее" напряжение. Одновременно с выхода разрядов счетчика 21, имеющего N состояний (фиг.26), поступают сигналы на управляющие входы первого 14 и второго 16 блоков аналоговых ключей, в которых в соответствии с таблицей истинности замыкается по одному ключу. Напряжения Umsin в t u Umcos u) t передаются через резисторы на неинвертирующий и инвертирующий входы суммирующего усилителя 29 с заданным коэффициентом передачи (фиг.2в,г).

Напряжение суммирующего усилителя

29 равно Umsin(ш t- gr). При прохождении кривой этого напряжения через ноль с положительной производной усилитель-ограничитель 17 формирует напряжение прямоугольной формы (фиг.2ж). Выходное напряжение усилителя-ограничителя дифференцируется дифференциатором 18 (фиг.2з). Положительный импульс, соответствующий переднему фронту напряжения

55 прямоугольной формы, проходит через диод

19 (фиг.2и) на блокинг-генератор 20. который формирует импульс необходимой амплитуды и длительности (фиг,2к). Импульс поступает через переключатель 9, коммутатор 7 на управляющий вход квантователя, открывая его, и на счетный вход счетчика 21, меняя его состояние. В соответствии с новым состоянием счетчика 21 переключаются ключи в блоках 14 и 15 аналоговых ключей.

На выходе суммирующего усилителя 29 напряжение, изменявшееся по закону

Um sIn (в! — grt ), начинает изменяться по закону Um sin (в! — фг ), Напряжение выхода усилителя-ограничителя 17 резко падает. На выходе дифференциатора 18 возникает отрицательный импульс, который через диод 19 не проходит. Напряжение

Um sin (u) с — !/2 ), возрастая, проходит через ноль с положительной производной.

Усилитель-ограничитель 17 формирует положительный перепад напряжения прямоугольной формы. Процесс работы блока 10 установки шага дискретизации повторяется. На каждом цикле меняется начальная фаза напряжения на выходе суммирующего усилителя 29 (фиг.2е). Величины входного сигнала, выбранные с частотой следования импульсов с блока 10 установки шага дискретизации, последовательно подаются на запоминающие ячейки 4 блока 3 памяти, где они запоминаются на время, необходимое для ввода информации. Выходные напряжения запоминающих ячеек 4 поступают на входы вычислительных ячеек 6 матрицы

5убг (5-> ). г

С помощью семивходовых суммирующих усилителей 25 и 26 и резисторов, входящих в вычислительную ячейку 5, выполняются операции по вычислению напряжений, пропорциональных вещественной и мнимой частям комплексного числа, соответствующего входной величине данной вычислительной ячейки. Напряжения, пропорциональные вещественной и мнимой частям результата вычисления, формируются на первом и втором выходах вычислительной ячейки путем взвешенного суммирования вещественных и мнимых частей входных комплексных чисел. При этом знак весового коэффициента вводится за счет подключения соответствующегосигнала на инвертирующие инеинвертирующие входы усилителя.

Выходные сигналы вычислительных ячеек матрицы 5у/2 (5 Х ) постуг пают на входы вычислительных ячеек матрицы 5у/г — (5 7 ) . где входные

1670619 сигналы разлагаются на ортогональные составляющие, В последующих матрицах вычислительных ячеек операции разложения входных напряжений вычислительными ячейками повторяются.

С выхода вычислительных ячеек первой (от выхода устройства) матрицы 5i снимаются сигналы, пропорциональные амплитудам ортогональных составляющих комплексного спектра.

Работа устройства прекращается, когда положительный импульс с блока 24 останова поступает на S-вход триггера 22, переводя его в положение "1", При настройке и наладке переключатель 9 через второй вход соединяет коммутатор 7 с генератором 8 импульсов.

Формула изобретения

Устройство для спектрального анализа по авт. св. N 11008833112244, о т л и ч а ю щ е е с я тем, что с целью повышения точности измерения, в него дополнительно введены последовательно соединенные многовходовый сумматор, усилитель-ограничитель, дифференциатор, диод, блокинг-генератор и переключатель, последовательно соединенные

5 трансформатор напряжений, фильтр нижних частот и квадратурный фазовращатель, блоки пуска и останова, два блока аналоговых ключей, триггер и счетчик, первый вход которого соединен с выходом триггера и с

10 первыми входами аналоговых ключей, вторые входы которых соединены с выходом счетчика, третьи входы — с выходом и входом квадратурного фазовращателя соответственно, выходы аналоговых ключей подклю15 ченн к входам многовходового сумматора, входы триггера соединены с выходами блока пуска и останова соответственно, второй вход счетчика соединен с первым входом переключателя, второй вход которого сое20 динен с выходом генератора импульсов, выход переключателя — с входом коммутатора, а вход трансформатора напряжений соединен с входом устройства и входом преобразователя.

1670619

1670619 о 1 2 5 g 5 6 7 0

cos 9 ф 1

О а г

oscut

v|t

3

U 6(Фиг. 2

Редактор М. Петрова

Заказ 2749 Тираж 406 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

-1 с д о

incog ь|л(аМ-Ф5 )

S;yut-ã25 ) л(И-УО )

in(cdt. - 80 )

МИ-155 ) Составитель Л. Устинова

Техред М.Моргентал Корректор А. Осауленко