Регенератор двоичных сигналов

Иллюстрации

Показать всеРеферат

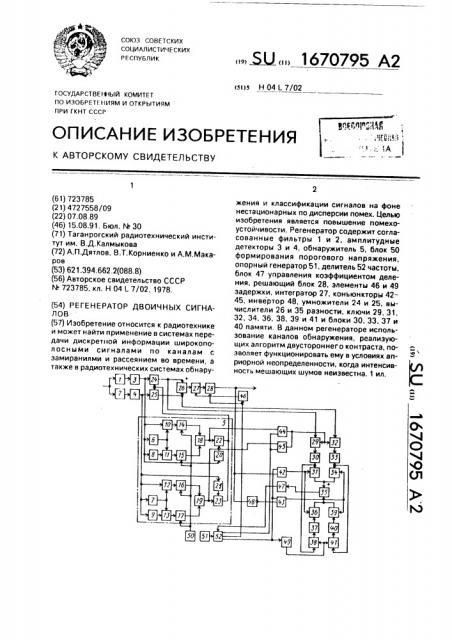

Изобретение относится к радиотехнике и может найти применение в системах передачи дискретной информации широкополосными сигналами по каналам с замираниями и рассеянием во времени, а также в радиотехнических системах обнаружения и классификации сигналов на фоне нестационарных по дисперсии помех. Целью изобретения является повышение помехоустойчивости. Регенератор содержит согласованные фильтры 1 и 2, амплитудные детекторы 3 и 4, обнаружитель 5, блок 50 формирования порогового напряжения, опорный генератор 51, делитель 52 частоты, блок 47 управления коэффициентом деления, решающий блок 28, элементы 46 и 49 задержки, интегратор 27, конъюкторы 42 - 45, инвертор 48, умножители 24 и 25, вычислители 26 и 35 разности, ключи 29, 31, 32, 34, 36, 38, 39 и 41 и блоки 30, 33, 37 и 40 памяти. В данном регенераторе использование каналов обнаружения, реализующих алгоритм двустороннего контраста, позволяет функционировать ему в условиях априорной неопределенности, когда интенсивность мешающих шумов неизвестна. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИ АЛ И СТИЧ Е С К ИХ

РЕСПУБЛИК (! 9) (11) (s()s Н 041 7/02

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТГНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ ф

О

О

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) 723785 (21) 4727558/09 (22) 07.08.89 (46) 15.08.91. Бюл. М 30 (71) Таганрогский радиотехнический институт им. В.Д.Калмыкова (72) А.П.Дятлов, В.Т,Корниенко и А.M,Ìàêaров (53) 621.394,662.2(088.8) (56) Авторское свидетельство СССР () 723785, кл. Н 04 L 7/02, 1978. (54) P Е ГЕН Е PATOP ДВОИЧ Н ЫХ СИГНАЛОВ (57) Изобретение относится к радиотехнике и может найти применение в системах передачи дискретной информации широкополосными сигналами по каналам с замираниями и рассеянием во времени, а также в радиотехнических системах обнаружения и классификации сигналов на фоне нестационарных по дисперсии помех. Целью изобретения является повышение помехоустойчивости, Регенератор содержит согласованные фильтры 1 и 2, амплитудные детекторы 3 и 4, обнаружитель 5, блок 50 формирования порогового напряжения, опорный генератор 51, делитель 52 частоты, блок 47 управления коэффициентом деления, решающий блок 28, элементы 46 и 49 задержки, интегратор 27, коньюнкторы 4245, инвертор 48, умножители 24 и 25, вычислители 26 и 35 разности, ключи 29, 31, Э2, 34, Эб, 38, 39 и 41 и блоки 30, 33. 37 и

40 памяти. В данном регенераторе использование каналов обнаружения, реализующих алгоритм двустороннего контраста, позволяет функционировать ему в условиях априорной неопределенности, когда интенсивность мешающих шумов неизвестна. 1 ил.

1670795

Изобретение относится к радиотехнике и может найти применение в системах передачи дискретной информации широкополосными сигналами по каналам с замираниями и рассеянием во времени, а также в радиотехнических системах обнаружения и классификации сигналов на фоне нестационарных по дисперсии помех.

Целью изобретения является повышение помехоустойчивости, На чертеже приведена структурно-электрическая схема предлагаемого регенератора.

Регенератор содержит согласованные фильтры 1 и 2, амплитудные детекторы 3 и

4, обнаружитель 5, содержащий первый 6, второй 7, третий 8 и четвертый 9 блоки задержки, первый 10, второй 11, третий 12 и четвертый 13 делители напряжения, первый

14, второй 15, третий 16 и четвертый 17 пороговые блоки, первый 18 и второй 19 решающие блоки, первый 20 и второй 21 блоки оценки амплитуды и первый 22 и второй 23 ключи, а также умножители 24 и 25, вычислитель 26 разности, интегратор 27, решающий блок 28, первый ключ 29, первый блок 30 памяти, второй 31 и третий 32 ключи, второй блок 33 памяти, четвертый ключ

34, дополнительный вычислитель 35 разности, пятый ключ 36, третий блок 37 памяти, шестой 38 и седьмой 39 ключи, четвертый блок 40 памяти, восьмой ключ 41, первый 42, второй 43, третий 44 и четвертый 45 коньюнкторы, первый элемент 46 задержки, блок

47 управления коэффициентом деления, инвертор 48, второй элемент 49 задержки, блок 50 формирования порогового напряжения, опорный генератор 51 и делитель 52 частоты.

Регенератор работает следующим образом, На вход подается сигнал, принимаемый на фоне аддитивного шума неизвестной мощности и неравномерным энергетическим спектром, причем каждая посылка передается широкополосным сигналом S1(t) или Sz(t). Передаваемые сигналы ортогональны. Проходя согласованные фильтры 1 и 2, сигнал сжимается во времени и происходит разделение лучей.

Введем следующие обозначения;

Vg1(К) — напряжение на выходе g-ro (g =

=1, 2) амплитудного детектора (3, 4) в 1-ом элементе временной дискретизации на ком такте; = 1, 1о, где Lo — количество элементов временной дискретизации на к-ом такте; VQI(K) — сигнальное напряжение на выходе первого элемента yG задержки

„,,(К) =-®

Vgi (к) () (к1

Vgi (K) 20

g = 1,2 (1).

Решение о наличии сигнала в g-ом канале (g = 1, 2) обнаружения выносится решающим блоком 18 или 19 при одновременном превышении обеими функциями контраста (1) заданного порогового уровня Z<, однозначно определяемого вероятностью ложной тревоги, вырабатываемого блоком 50 формирования порогового напряжения и подаваемого на другие входы пороговых блоков 14 и 15 обнаружителя 5, В те моменты времени, когда принимается решение о наличии (гипотеза Н1) и отсутствии (гипотеза Mo) сигнала (луча) в соответствии с решающим правилом (Щ1 (K) Zo) П (Щ2 (К) > Zo) Н1 (77g11 (К) ) Zo) и (7912 (K) < Q)g H (2) (9911 (K) 0) и (gglp (K) Zo) на выходах решающих блоков 18 и 19 появ45 ляется единичный или нулевой потенциал. который подается соответственно на первые входы третьего 44 и четвертого 45 коньюнкторов. При этом в момент принятия решения о наличии сигнала открывается первый ключ 22 и с выхода блока 20 оценки амплитуды сигнал подается на вторые входы умножителей 24 и 25. Если сигнал в некоторый момент времени не обнаруживается, то оценка амплитуды равна нулю.

В результате перемножения огибающей процесса на оценку амплитуды сильные лучи усиливаются больше (подчеркиваются), а слабые — меньше (подавляются). После перемножения на оценку амплитуды сигналы вычитаются и на выходе вычислителя 26 в g-ом канале в (-ом элементе времени дискретизации на к-ом такте;

Н i (К) — опорное напряжение на выходе второго элемента 49 задержки в g-ом канале

a l-ом элементе временной дискретизации на к-ом такте, С выходом амплитудных детекторов 3, 4 сигналы подаются на первый вход первого делителя 10 напряжения непосредственно, 10 а на второй вход — через первый блок 6 задержки, на входы второго делителя 11 напряжения через первый 6 и третий 8 блоки задержки и непосредственно на вход блока

20 оценки амплитуды в обнаружителе 5, Таким образом на выходах делителей 10 и 11 напряжения формируются функции контраста

1670795 разности получается биполярный видеосигнал. Мощности обнаруженных лучей суммируются в интеграторе 27. Наличие умножителей 24 и 25, а также обнаружителя

5, реализующего алгоритм двустороннего контраста, позволяет отделить сигналы лучей от тех временных интервалов, где присутствует только шум, обнаруживать сигналы при априоринеизвестной интенсивности шума, а также осуществить весовое суммирование обнаруженных лучей.

Решение о значении дискретного информационного параметра Ч(т) = +1 принимается в решающем блоке 28 путем опроса один раз за такт состояния интегратора 27, Если в момент опроса напряжение на выходе интегратора 27 положительно, то принимается решение о том, что передан символ

"1" при отрицательном выходном напряжении интегратора 27 принимается решение в пользу символа "0" (этому соответствует нулевой потенциал на выходе решающего блока 28). Моменты регистрации символов (моменты опроса) определяются импульсами, следующими с периодом

Т и поступающими на второй вход решающего блока 28 с первого импульсного выхода делителя 52 частоты, Эти же импульсы через первый элемент 63 задержки поступают на второй вход интегратора 27 для его обнуления. Вероятность ошибочной регистрации символов минимальна, если в интервал интегрирования попадают сигналы лучей одной полярности, относящиеся к одному переданному символу. Это возможно, когда импульсы, управляющие работой решающего блока 28 и обнуляющие интегратор 27, располагаются между последним лучом предыдущей посылки и первым лучом последующей посылки. При этом предполагается, что интервал рассеяния сигнала во времени Тр меньше тактового интервала Т на некоторую защитную величину, При появлении на объединенных выходах третьего 44 и четвертого 45 конъюнкторов импульса обнаружения и отсутствии запрещающего (нулевого) потенциала на вторых входах третьего 44 и четвертого 45 конъюнкторов, замыкаются ключи 29 и 32. а амплитуды процессов, действующих в эти моменты времени на выходах умножителей 24 и 25, запоминаются в первом 30 и втором 33 блоках памяти. Один раз за такт на втором импульсном выходе делителя 52 частоты появляется синхроимпульс, который, пройдя второй элемент 49 задержки, замыкает ключи 38 и 41. В эти моменты времени информация с выхода первого 30 и третьего 33 блоков памяти

55 туды входного сигнала в 1-ом элементе временной дискретизации на к-ом такте, а в блоках 37 и 40 памяти на к-ом такте хранятся

Ф величины А (К-1) Ч (К-1). Следовательно, в момент времени т1(К), когда на втором импульсном выходе делителя 52 частоты появпереписывается соответственно в третий 37 и четвертый 40 блоки памяти. Таким образом в моменты появления синхроимпульсов на выходах блоков 30 и 33 присутствуют на5 пряжения, имевшие место в момент последнего обнаружения луча на текущем к-ом такте, а на выходах блоков 37 и 40 присутствуют напряжения, имевшие место в момент последнего обнаружения луча на предыду10 щем (к — 1)-ом такте. В качестве блоков памяти могут быть использованы, например. конденсаторы в цепи с малой постоянной времени заряда (меньшей, чем длительность элемента временной дискретизации)

15 и большой по сравнению с тактом постоянной времени разряда.

Опрос состояния интегратора 27 в решающем блоке 28 и обнуление интегратора

27 происходит раньше на величину d>, чем

20 на втором импульсном выходе делителя 52 частоты появляется очередной синхроимпульс, временное положение которого и определяет текущую оценку ri(K) задержки первого луча (К вЂ” номер такта). Таким образом к моменту появления синхроимпульса решение о значении информационного дискретного параметра V(t) уже принято и на выходе решающего блока 28 к моменту rt(K)

3р устанавливается единичный или нулевой потенциал.

Единичный потенциал на выходе решающего блока 28 открывает первый конъюнктор 42, запирая через инвертор 48 второй коньюнктор. Нулевой потенциал на выходе решающего блока 28, наоборот. запирает первый конъюнктор 42 и открывает второй коньюнктор 43, Таким образом синхронизирующий импульс, поступающий в момент

40 времени г (К) на первые входы конъюнкторов 42 и 43, появляется в зависимости от потенциала на выходе решающего блока

28 либо на управляющих входах ключей 31 и 36, либо на управляющих входах ключей

45 34 и 39. В результате на входы дополнительного вычислителя 35 разности поступают либо напряжения с входов первого

30 и третьего 37 блоков памяти, либо напряжения с выходов второго 33 и четвертого 40 блоков памяти, Таким образом в блоках 30 и 33 памяти на текущем к-ом такте запоминаются величины A((К) Vgl(K), где А (К) — оценка ампли1670795 ляется синхроимпульс. замыкающий одну иэ пар ключей 31 и 36 или 34 и 39, на выходе дополнительного вычислителя 35 разности образуется сигнал коррекции

ЛЧ(К) =- А (К) Vgl (К) — А (К-1) х х Vgl (К - 1). (3)

При формировании сигнала коррекции и перезаписи информации из первого 30 и второго 33 блоков памяти соответственно в третий 37 и четвертый 40 блоки памяти импульсы обнаружения запрещаются с помощью коньюнкторов 44 и 45 импульсами запрета, за счет чего состояние первого 30 и второго 33 блоков памяти остается неизменным, В момент времени (r>(K) — у1) производится опрос интегратора 27 с последующим

его обнулением. В результате опроса в решающем блоке 28 принимается решение в пользу символа "1". В результате;-.ого решения в момент времени т1(К) на входы дополнительного вычислителя 35 разности поступают сигналы с выходов первого 30 и третьего 37 блоков памяти. При этом на выходе дополнительного вычислителя 35 разности формируется отрицательный сигнал коррекции.

ЛЧ(К) =- Al* (К) Vgl(К) — Al* (К-1) х

x Vgl (K - 1). (4) так как в интервале (KTo, (К+ 1)Tp) на выходе первого амплитудного детектора 3 действует только шум и в первый блок 30 памяти в моменты обнаружения записываются значения шумовой реализации, а в интер; вале ((К - 1)Т, КТ0) на выходе первого амплитудного детектора 3 действует смесь сигналов с шумом и в третий блок 37 памяти в момент Т> (К - 1) переписывается случайная величина, которая определяется суммарным напряжением шума и сигнала третьего луча.

В момент времени (ri (К+ 1) - д1) принимается решение в пользу символа (-1), на выходе решающего блока 28 устанавливается нулевой потенциал, под действием которого в момент т1(К + 1) на выходы дополнительного вычислителя 35 разности поступают сигналы с выходов второго 33 и четвертого 40 блоков памяти. При этом также формируется отрицательный сигнал коррекции

A V (К + 1) = Al (К + 1) Vgl (К+ 1)— — Al (К) Vgl (К ), (5) 5

m 1(Л V (К)) = О.

Очевидно, что в этом случае принимаемый сигнал не несет в себе синхронизирующей информации. Таким образом знак сигнала коррекции меняется при переходе через ti(K). Описанная процедура формирования Л V(K) рассматривается для случая, когда 11 (К) > г (К). При r> (K)< т1 (К) процедура формирования аналогична, при этом Л V(K) > О. Дисперсия ошибки оценки т1(К) при фиксированном отношении сигнал/шум определяется коэффициентом усиления блока 47 управления коэффициентом деления. Из двух членов, стоящих в правой части выражения (3), при правильном обнаружении луча и раэнополярных соседних посылках один член с точностью до оценки амплитуды представляет собой огибающую шума, а другой — огибающую смеси сигнала и шума, так что в регенераторе сигнал коррекции определяется амплитудой сигнала.

Использование каналов обнаружения, реализующих алгоритм двустороннего контраста, позволяет регенератору функционировать в условиях априорной неопределенности, когда интенсивность мешающих шумов неизвестна.

Таким образом при приеме сигналов на фоне аддитивных шумов меняющейся интенсивности никакой подстройки порога под фактические значение уровня шумов не требуется и обеспечивается высокая устойчивость к изменению формы спектра мешающих шумов.

Формула изобретения

1. Регенератор двоичных сигналов по автсв. М723785, от л и ч а ю щи йс ятем, что, с целью повышения помехоустойчивости при воздействии аддитивных шумов меняющейся интенсивности, введены блок формирования порогового напряжения и четвертый коньюнктор, первый и второй входы и выход которого соединены соответПод действием сигнала коррекции оценка t> (К) уменьшается, стремясь к ti(K), так как задержка синхроимпульсов уменьшается, стремясь к задержке первого луча.

При следовании подряд нескольких посылок одного знака в идеальной ситуации пои отсутствии шумов и замираний Л V (К) = О, так как сигналы на двух соседних посылках одинаковы. В реальной же ситуации при следовании подряд нескольких посылок одного знака математическое ожидание сигнала коррекции равно нулю, т.е.

1670795

Составитель О. Андрушко

Редактор Ю. Середа Техред М.Моргентал Корректор В. Гирняк

Заказ 2757 Тираж 375 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", r. Ужгород. ул. Гагарина, 101 ственно с третьими выходами обнаружителя и делителя частоты и выходом третьего

Ko Hb lo HK To pa, а выход блока формирования порогового напряжения подключен кдополнительному входу обнаружителя.

2. Регенератор по п.1, о т л и ч а ю щ и йс я тем, что обнаружитель выполнен в виде первого и второго блоков оценки амплитуды, первого и второго блоков задержки, последовательно соединенных первого делителя напряжения, первого порогового блока, первого решающего блока и первого ключа, последовательно соединенных третьего блока задержки, второго делителя напряжения и второго порогового блока, последовательно соединенных, третьего делителя напряжения, третьего порогового блока, второго решающего блока и второго ключа и последовательно Соединенных четвертого блока задержки, четвертого делителя напряжения и четвертого порогового блока, причем первый вход первого делителя напряжения соединен с входами первого блока оценки амплитуды, третьего блока держки и первого блока задержки, выход которого подключен к вторым входам первого и второго делителей напряжения, первый вход третьего делителя напряжения

5 соединен с входами второго блока оценки амплитуды, четвертого блока задержки и второго блока задержки, выход которого подключен к вторым входам третьего и четвертого делителей напряжения, вторые вхо10 ды всех пороговых блоков объединены, выходы второго и четвертого пороговых блоков подключены к вторым входам соответственно первого и второго решающих блоков, выходы первого и второго блоков оценки

15 амплитуды подключены к вторым входам соответственно первого и второго ключей, выходы которых являются первым выходом обнаружителя, вторым и третьим выходами и первым и вторым входами которого явля20 ются соответственно выходы первого и второго решающих блоков и входы первого и второго блоков задержки, а второй вход первого порогового блока является дополнительным входом обнаружителя.