Демодулятор сигналов с фазоразностной модуляцией

Иллюстрации

Показать всеРеферат

Изобретение относится к радиосвязи и может найти применение в системах передачи дискретной информации в каналах связи с нестабильной частотой несущего колебания. Целью изобретения является повышение помехоустойчивости. Демодулятор содержит линию 1 задержки, умножители 2, 4, 8, 10, 15 и 17, фазовращатель 3, интеграторы 5 и 6, блоки 7, 11, 12, 13 и 14 задержки, сумматоры 9 и 16 и блок 18 принятия решения. В данном демодуляторе за счет использования дополнительных квадратурных значений первых разностей фаз, содержащих информацию о неопределенном фазовом набеге, частично компенсируется незнание частоты сигнала. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)5 Н 04 L 27/22

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4728725/09 (22) 07,08.89 (46) 15.08,91. Бюл, М 30 (72) Н.М.Сидоров (53) 621,394.62(088 8) (56) Окунев Ю.Б. Теория фазораэностной модуляции. М.: Связь. 1979, с. 140, (54) ДЕМОДУЛЯТОР СИГНАЛОВ С ФАЗОРАЗНОСТНОЙ МОДУЛЯЦИЕЙ (57) Изобретение относится к радиосвязи и может найти применение в системах передачи дискретной информации в каналах свя,,5U„„1670799 А1 эи с нестабильной частотой несущего колебания. Целью изобретения является повышение помехоустойчивости. Демодулятор содержит линию 1 задержки, умножители 2, 4, 8, 10, 15 и 17, фазовращатель 3, интеграторы 5 и 6, блоки 7, 11, 12, 13 и 14 задержки, сумматоры 9 и 16 и блок 18 принятия решения. В данном демодуляторе эа счет использования дополнительных квадратурных значений первых разностей фаз, содержащих информацию о неопределенном фазовом набеге, частично компенсируется незнание частоты сигнала. 2 ил. 0

О

1О

1670799

Изобретение относится к радиосвязи и может найти применение в системах передачи дискретной информации в канапах связи с нестабильной частотой несущего колебания.

Целью изобретения является повышение помехоустойчивости.

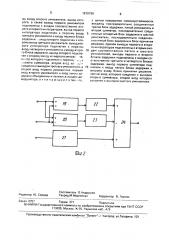

На фиг,1 приведена структурно-электрическая схема демодулятора; на фиг,2— структурно-электрическая схема блока принятия решения.

Демодулятор содержит линию 1 задержки, первый умножитель 2, фаэовращатель

3, второй умножитель 4, первый 5 и второй

6 интеграторы, первый блок 7 задержки, третий умножитель 8, первый сумматор 9, четвертый умножитель 10, второй 11, третий

12, четвертый 13 и пятый 14 блоки задержки, пятый умножитель 15, второй сумматор 16, шестой умножитель 17 и блок 18 принятия решения, который содержит первый 19 и второй 20 сумматоры, умножитель 21, первый 22 и второй 23 выпрямители и сумматор

24.

Демодулятор работает следующим образом, В блоке 18 принятия решения определяется знак суммы трех величин: удвоенного значения с выхода первого сумматора 9 плюс абсолютное значение от суммы двух выходов: выхода второго сумматора 9 и выхода пятого блока 14 задержки и минус абсолютное значение от разности этих двух выходов.

Входной сигнал подается на автокорреляторы, которые формиру от квадратурные значения первой разности фаз. Формирователь квадратурных значений первой разности фаз состоит иэ линии 1 задержки на длительность посылки, фаэовращателя 3. умножителей 2, 4 и интеграторов 5, 6, на выходе которых вычисляются проекции входного сигнала x(t) на координатные функции x(t - Т) и х (t - T), где х (t - Т) — и реобраэованный по Гильберту сигнал x(t - Т), формируемый фазовращателем 3, Напряжения на выходах автокорреляторов (выходы интеграторов 5 и 6) пропорциональны квадратурным значениям разности фаэ между соседними посылками

Xn - Е COS («М+ APn), Yn = Е sin ( — значение несущей частоты;

Т вЂ” длительность посылки;

Apn — разность фаэ между и-й и (и - 1)-й посылками;

Š— енергия сигнала, приходящаяся на бит передаваемой информации.

R блоках 8, 9, 10 по X Y и задержанным в блоках 7 и 11 задержки значениям

Хп-1 = Е COS («4+ APn — 1):

5 Уп-1 = Е sin (

l1= Xn Xn-1+ Yn Yn-1= Е COSA Pn г инвариантный к частоте несущего колебания, Сущность изобретения заключается в обработке варианта большей длительности, чем передаваемый вариант сигнала.

В демодуляторе обрабатывается сигнал длительностью в четыре посылки.

Для этого при принятии решения о переданной второй разнос ги фаэ используются дополнительные квадратурные значения первой разности фаз

Хп-2 = Е COS («> Т + A p n — 2 ), Уп.2 = Е Sin (Ж Т + Apn — 2), 25 которые формируются в блоках 12 и 13 задержки и содержат информацию о неопределенном параметре со Т, Это позволяет повысить помехоустойчивость приема, Добавленный блок 18 принятия решения анализирует, кроме l1, еще два сигнала

l2=Е созЛ p — 1 и

13 = Е cos (Apn Apn — 2), 35 при этом 11 подается с первого сумматора 9, 12 — с блока 14 задержки, а !з формируется в элементах 12, 13, 15, 16 и 17 и подается с второго сумматора 16.

40 Блок принятия решения построен по алгоритму з 9п (i) = з 9п (2 1+ 1 2+ 31 2 з!)

Положительное значение выходной величины I соответствует A2 pn = О, а отрица45 2

ТЕЛЬНОŠ— Л pn = 2Г.

Повышение помехоустойчивости в демодуляторе достигается за счет использования дополнительных квадратурных значений первых разностей фаэ, содержит информацию о неопределенном фазовом набеге, что позволяет частично компенсировать незнание частоты сигнала.

Формула изобретения

Демодулятор сигналов с фазоразностной модуляцией, содержащий линию задержки, выход которой подключен к первому входу первого умножителя и входу фазовращателя, выход которого подключен к перво1670799

Составитель Q.Àíäðóøêî

Техред М,Моргентал Корректор В. Гирняк

Редактор Ю. Середа

Заказ 2757 Тираж 371 Подписное

8НИИПИ Государственного комитета пс изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб„4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101 му входу второго умножителя. выход которого, а также выход первого умножителя подключены к входам соответственно второго и первого интеграторов, выход первого интегратора подключен к первому входу 5 третьего умножителя и входу первого блока задержки, ыход которого подключен к второму входу третьего умнажителя, выход второго интегратора подключен к первому входу четвертого умножителя и входу второ- 10 го блока задержки, выход которого подключен к второму входу че вертого умнож я, въ од которого подключен к первому ..", v, ервого сумматора, второй вхсд ко соединен с выходом третьего умножителя, а 15 второй вход первого умножителя, первый вход второго умножителя и вход линии задержки объединены и являются входом демодулятора, отличающийся тем, чго, с целью повышения помехоустойчивости, введены последовательно соединенные третий блок задержки, пятый умножитель и второй сумматор, последовательно соединенные четвертый блок задержки и шестой умножитель, последовательно соединенные пятый блок задержки и блок принятия решения, причем выходы первого и второго интеграторов подключены к вторым входам соответственно пятого и шестого умножителей, выходы первого и второго блоков задержки подключены к входам соответственно третьего и четвертого блоков задержки, выход первого сумматора подключен к входу пятого блока задержки и второму входу блока принятия решения, третий вход которого соединен с выходом второ о сумматора, второй вход которого соединен с выходом шестого умножителя.