Устройство для деления

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может найти применение в арифметических устройствах для реализации множительно-делительных операций универсальных и специализированных вычислителях. Цель изобретения - расширение функциональных возможностей за счет выполнения операции умножения. Устройство содержит регистр первого операнда 1, регистр второго операнда 2, регистр результата 3, сумматор по модулю два 4, блок памяти 5, сумматор 6, блок выбора операции 7, генератор тактовых импульсов 8, коммутатор 9. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (s»s G 06 F 7/52

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ;

ЖЗЯДЯ

4„ 1; а

1 1 1 1 1

Ci С2 Сэ С4 Cï

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4668252/24 (22) 13.01.89 (46) 23.08.91. Бюл, ¹ 31 (71) Ташкентский политехнический институт имени А.P.Áèðóíè (72) А,Л.Кушнаренко, С.В.Дегтярев и

Б.Н.Бекмухамедов (53) 681.325(088.8) (56) Авторское свидетельство СССР

¹ 987621, кл. G 06 F 7/52, 1981.

Авторское свидетельство СССР

¹ 1290303, кл, G 06 F 7/52, 1985. (54) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ

Устройство относится к вычислительной технике и может быть использовано в арифметических устройствах, для реализации множительно-делительных операций, универсальных и специализированных вычислителях, обрабатывающих двоичную информацию.

Цель изобретения — расширение функциональных воэможностей за счет выполнения операции умножения.

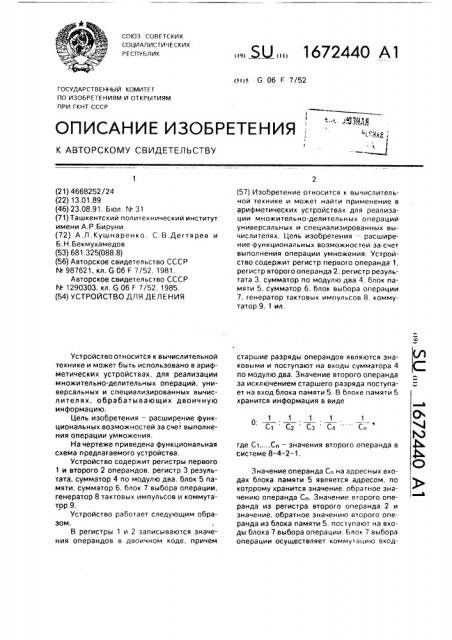

На чертеже приведена функциональная схема предлагаемого устройства.

Устройство содержит регистры первого

1 и второго 2 операндов, регистр 3 результата, сумматор 4 по модулю два, блок 5 памяти, сумматор 6, блок 7 выбора операции, генератор 8 тактовых импульсов и коммутатор 9.

Устройство работает следующим образом.

В регистры 1 и 2 записываются значения операндов в двоичном коде, причем.. Й2 1672440 А1 (57) Изобретение относится к вычислительной технике и может найти применение в арифметических устройствах для реализации множительно-делительных операций универсальных и специализированных вычислителях. Цель изобретения — расширение функциональных возможностей за счет выполнения операции умножения. Устройство содержит регистр первого операнда 1, регистр второго операнда 2, регистр результата 3, сумматор по модулю два 4, блок памяти 5, сумматор 6, блок выбора операции

7, генератор тактовых импульсов 8, коммутатор 9, 1 ил. старшие разряды операндов являются знаковыми и поступают на входы сумматора 4 по модулю два. Значение второго операнда эа исключением старшего разряда поступает на вход блока памяти 5. В блоке памяти 5 хранится информация в виде где С1,...,Cп — значения второго операнда в системе 8-4-2-1.

Значение операнда Сп на адресных входах блока памяти 5 является адресом, по которому хранится значение. обратное значению операнда Сп. Значение второго операнда из регистра второго операнда 2 и значение, обратное значению второго операнда из блока памяти 5. поступают на входы блока 7 выбора операции. Блок 7 выбора операции осуществляет коммутацию вход1672440 ных значений в зависимости от кода операции (умножения или деления). Если на выходе блока 7 выбора операции устанавливается значение второго операйда, то результат. получаемый на выходе устройства, является произведением первого и второго операнда. Если же на выходе блока выбора операции 7 устанавливается значение, обратное значению второго операнда, то результат, получаемый на выходе устройства, является частным от деления первого операнда на второй. Операция умножения значения первого операнда на значение, установленное на выходе блока 7 выбора операции, осуществляется следующим образом.

Формула изобретения

Составитель Е.Мурзина

Техред M,Ìoðãåíòàë Корректор А.Осауленко

Редактор Т.Шагова

Заказ 2840 Тираж 374 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101 а

Одновременно с установлением коммутируемого значения на выходе блока 7 выбора операции в блоке формируется сигнал управления. разрешающий работу генератора тактовых импульсов 8, который осущствляет по каждомду такту сдвиг регистра первого операнда 1, который выполняет фукнцию последовательного вывода разрядов первого операнда 1. Коммутатор 9 опрашивает выход блока выбора операции 7: за один такт — один разряд. При наличии "логической единицы" в разряде производится запись в регистр 3 результата информации с двоичного сумматора 6. После завершения опроса всех разрядов вычисление автоматически завершается. Результат находится в регистре 3 результата. Знаковый разряд результата формируется на выходе сумматора 4 по модулю два, Устройство для деления, содержащее регистры первого и второго операндов, сум5 матор, регистр результата. генератор тактовых импульсов, блок памяти и коммутатор, причем выход сумматора соединен ". инфор, мационным входом регистра результата, выход которого соединен с выходом реэуль10 тата устройства и входом первого слагаемого сумматора, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных воэможностЕй эа счет выполнения операции умножения, в него введены блок выбора

15 операции и сумматор по модулю два, выход которого соединен с выходом знака результата устройства, а первый и второй входы— соответственно с выходами знаковых разрядов регистров первого и второго операн2р дов, вход второго слагаемого сумматора соединен с разрядными выходами регистра первого операнда, вход сдвига которого соединен с управляющим входом коммутатора и выходом генератора тактовых

25 импульсов, вход которого соединен с первым выходом блока выбора операции, первый информационный вход которого соединен с разрядными выходами регистра второго операнда и входом блока памяти, выход которого соединен с вторым информационным входом блока выбора операции, управляющий вход которого соединен с входом кода операции устройства, а второй выход — с информационным входом коммутатора, выход которого соединен с входом записи регистоа результата.