Узел контроля вычислительной системы

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для встроенного контроля асинхронных цифровых вычислительных систем, а также в аппаратуре автоматизированного контроля цифровых блоков. Цель изобретения - расширение области применения за счет увеличения класса обнаруживаемых неисправностей при контроле последовательностных и асинхронных цифровых блоков. С этой целью в узел контроля, содержащий два триггера и два элемента И, введены третий и четвертый элементы И и три элемента ИЛИ. 1 табл., 7 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (S1)S С 06 Е 11/-"6

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

Н А BTOPCHOMY СВИДЕТЕЛЬСТВУ (21 ) 4675650/24 . (22) 11. 04. 89 (46) 2.3. 08. 91. Бюл. И- 31 (71) Ленинградский электротехн гческий институт им. В.И.Ульянова (Ленина) (72) A. С. Календарев, Н.Д.Лгггтецкая, И. В, Матвеев и Д. В. Пуз анков (53? «81. 32 (088. 8) (56) Патент США ¹ 3976864, кл. 235-153, опублик. 1976, Авторское свидетельство СССР

Р 1149265, кл. С 06 Г 11/26, 1985.

Изобретение относится к вычислительной технике и может быть использовано для встроенного контроля асинхронных цифровых вычислительных систем, а также в аппаратуре антоматизггрованггого контроля цифровых блоков, Цель изобретения — расширение области применения за счет увеличения класса обнаруживаемых н исправностей (возникающих в синхронных и асинхронных вычислительньгх сис гемах) при к<>нтролс последовательноетных и а с и ихро н ных цифр о вых бло ко в .

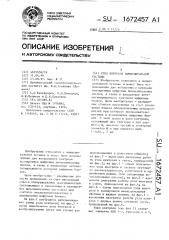

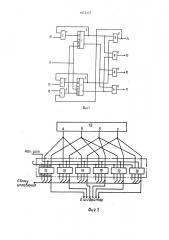

На фиг.1 изображена функциональная схема узла контроля, на фиг.2 схема подключения узла контроля к контролируемому блоку для случая его (1672457 А1

2 (54) УЗЕЛ КОНТРОЛЯ ВЬИИСЛИТЕЛЬПОИ

СИСТЕМЫ (57) Изобретение относится к вычислительной технике и может быть использовано для встроеHHOI о контроля асинхронных цифровых вычислительных систем, а также в аппаратуре автоматизированного контроля цифровых блоков. Цель изобретения — распгирение области применения за счет увеличения класса обнаруживаемых неисправностей при контроле последовательностных и асинхронных цифровых блоков„ С этой целью в узел контроля, содержащгм два триггера и два элемента И, введены третий и четвертый элементы И и три элемента II1IH, 1 табл,, 7 ил, использования в известном объекте, на фиг.3 — временная диаграмма рабой ты узла контроля в схеме, приведеннои на фиг.2; на фиг.4 — схема подключе- О н1гя узла контроля в системе тестового диагностироваг.ия, работающей в од- Я нотактном режиме (для синхронных вы- ф3 числительных систем); на фиг.5 — вре- (Л менная диаграмма работы узла контроля в с еме, приведенной на фиг ° 4; на фиг.б — схема подключения узла контроля к асинхроннои вычислительной системе в ждущем режиме, на фиг.7 временная диаграмма работы узла контроля в ждущем режиме со гласно схеме р приведенной на фиг.б.

Узел контроля (см. фиг.,1) содержит элементы ИЛИ 3, триггеры 4 и 5, 1672457 п/п jВых, 15 Вых. 16 Вых. 11

1

0

1

0

1

0

0

0

0

=х,g х

, = Х, 3 Х, =x,3,xÄ ъ =х йх

45 элементы И 6-9 и имеет первый информационный вход 10, вход 11 синхронизации, второй информационный вход

12, вход 1 3 начальной установки, выходы 14-17 результата.

Кроме того, на фиг.2 дополнительно показаны объект 18 контроля и узел

19 контроля. На фиг.4, кроме объекта

18 контроля и узла 19 контроля, изображены блок 20 памяти тестов, 20 мно гоканальный сигнатурный анализатор 21 и блок 22 индикации. На фиг.6, кроме узла 19 контроля и блока 22 индикации, дополнительно изображены ведущий блок 23 (активное вычислительное устройство), ведомый блок

24 (пассивное вычислительное устройстВо), блок 25 регистровой памяти, блок 26 обработки измерительной информации и элемент ИЛИ 27.

Узел работает следующим образом.

Узел может работать в однотактном и ждущем режиме.

В однотактном режиме на соответствующе выходах 14-17 узла формируют(:ÿ сигналы Y) q Yg p Y gq Y4 при возник — 35 новении всех возможных комбинаций входных сигналов Х и Х, поступающих соответственно на входы 10 и 12 в соответствии с уравнением (1)

В каждом такте на одном из выходов узла формируется единичный сигнал, индициирующий появление определенной комбинации входных сигналов. Установка триггеров 4 и 5 осуществляется по сигналу синхронизации С, поступающему на вход,, узла. Начальная установка триггеров 4и 5 вновь. осуществляется перед подачей каждого синхроимпульса

55 путем подачи сигнала К начальной установки на вход 13 узла. При этом сигнал, соответствующий "логической единице", с выхода элемента ИЛИ 3

Элементы И 6-9 обеспечивают формирование сигналов на выходах 14-17 в соответствии с таблицей. поступает на входы начальной установки триггеров 4 и 5. Этот режим работы может быть использован при работе узла в качестве схемы сравнения в составе внешних средств тестового диагностирования (при необходймости сравнения в каждом такте контролируемого и эталонного сигналов), В ждущем режиме работы узла контролируется появление определенной комбинации сигналов Х и Х на входах 10 и 12 на заданный промежуток времени. Подобные ситуации возникают при организации асинхронной связи между вычислительными устройствами по принципу "управляющий — управляемый" ("активный пассивный"). .Таким образом при работе в ждущем режиме узел предназначен для использования в составе встроенных средств контроля вычислительных систем с асинхронным принципом связи между вычислительными устройствами.

Пример. Пусть активным уров= нем управляющего (Х,) и ответного (Х ) сигналов будет являться единич2 ный уровень. Приход активного управляющего сигнала Х на вход 10 узла формирует на выходе первого элемента

ИЛИ 1 сигнал "логической единицы", который при поступлении на информационный вход первого триггера 4 ус" танавливает триггер в единичное состояние при приходе на вход С единичного синхроимпульса с входа 11 узла.

Сигнал, соответствующий логической единице, с прямого выхода первого триггера 4 поступает на первый вход первого элемента ИЛИ 1. Первый триггер 4 блокируется в единичном состоянии. Приход за определенный промежуток времени t ответного сигнала

Х на вход 13 узла формирует на вы2. ходе второго элемента ИЛИ 2 сигнал логической единицы, который при

1672457 поступлении на информационный вход второго триггера 5 устанавливает триггер в единичное состояние. Сигнал, соответствующий "логической единице, с прямого выхода второго триггера 5 поступает на первый вход второго элемента ИЛИ 2. Второй триггер 5 блокируется в единичном состоянии. В известном устройстве в тест включены лишь пары наборов X = О, Х =1 иХ =1.Х =О. Такимобра2 < 2 зом не проверяются ситуации Х, = 1, Х = 1 (разрешение обмена) и X = О

2 1

Х = О (пауза).

В данном узле наблюдаеа ся два варианта начальной установки.

Сигнал R начальной установки подается с входа 13 узла на первый вход третьего элемента ИЛИ 3, на выходе которого формируется сигнал, соответствующий логической единице", поступающий на входы К начальной .установки обоих триггеров 4 и 5. При этом сигнал начальной установки по входу 13 подается с периодом, равным по истечении которого производится анализ подаваемых на входы 10 и 12 сигналов Х и Х . Кроме того, оба триггера 4 и 5 бнуляются путем подачи на входы R начальной установки триггеров 4 и 5 сигнала, соответствующего логической единице, с выхода третьего элемента ИЛИ 3, на второй вход которого с выхода первого элемента И 6 поступает сигнал У1 = 1.

Это позволяет подготовить узел контроля к приему новой информации за меньший промежуток времени.

Формула изобретения

Узел контроля вычислительной системы, содержащий два триггера и два

40 элемента И, причем прямой выход первого триггера соединен с первыми входами первог< и второго элементов И, прямой выход в то ро го три гге ра подключен к второму входу первого элемента

И, а.выходы первого и второro эле— ментов И являются соответственно первым и вторым выходами результата узла,от ли чающий сятем, что, с целью расширения области применения за счет увеличения класса обнаруживаемых неисправностей при контроле последовательностных и асинхронных цифровых блоков, он содержит третий и четвертый элементы И и три элемента ИЛИ, при этом прямые выходы первого и второго триггеров соединены с первыми входами соответственно первого и второго элементов

ИЛИ, вторые входы которых являются соответственно первым и вторым информационными входами узла, выходы первого и второго элементов ИЛИ подключены к информационным входам соответственно первого и второго триггеров, первый и второй входы и выход третьего элемента ИШ1 соединены соответственно с входом начальной установки узла, выходом первого элемента И и входами сбро са первого и в то ро го триггеров, второй вход второго элемента И подключен к инверсному выходу второго триггера, первые входы третьего и четвертого элементов И соединены с инверсным выходом первого триггера, вторые входы третьего и ч твертого элементов И подключены соответственно к прямому и инверсному выходам второго триггера, а выходы третьего и четвертого элементов И являются соответственно третьим и четвертым выходами результата узла, 1672457

Нач

Клоку управе шоФрааар

Юиа Г

1612451

1672451

8х. 11

BX. 13

Bl . 1О

ЮХ 72 йи 19

Вых 15 йа. 16

Вьх. 77

1672457

Вх. О

Вх. 12

Редактор Т.Шагова

Заказ 2841 Тираж 391 Подписное

ВНИИЛИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101

Вх. 13

8х, 70 дых. 79

Вык 75 дых. 16 дух. 77

Piuреш.

Заиосц о память

Ъ

Составитет6 Г.Виталиев

Техред Л.Сердюкова Корректор М.Демчик