Формирователь сигналов с амплитудной и угловой модуляцией

Иллюстрации

Показать всеРеферат

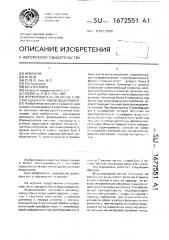

Изобретение относится к радиотехнике и может использоваться в системах передачи сигналов с амплитудной и угловой модуляцией. Цель изобретения - расширение диапазона частот формируемого с сигнала. Формирователь сигналов с амплитудной и угловой модуляцией содержит генератор 1 тактовых импульсов, двоичный сумматор 2, первый регистр 3 памяти, первый блок 4 постоянной памяти, цифроаналоговый преобразователь 5, второй регистр 9 памяти. Цель достигается введением перемножающего цифроаналогового преобразователи 6, фильтра 7 нижних частот, второго блока 8 постоянной памяти. Сумматор 2 и регистр 3 образуют накопительный сумматор, который используется в качестве делителя частоты с дробно-переменным коэффициентом деления. На выходе блока 8 появляется код амплитуды синусоидального колебания, соответствующий текущей фазе формируемого сигнала. Преобразователь 5 преобразует его в напряжение, которое поступает на преобразователь 6, на цифровой вход которого с второго выхода блока 4 поступает код текущего значения амплитуды формируемого сигнала. Фильтр 7 нижних частот очищает спектр формируемого сигнала от помех квантования с частотой, равной частоте следования импульсов с выхода генератора 1. 1 ил.

союз совгтских

СОЦИАПИСГИЧГСКИХ

РЕСПУБЛИК (5Н5 Н 03 С 5/00

ГОСУДАРСТВЕННЫЙ КОМИН-Т

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4689234/09 (22) 05.05.89 (46) 23.08.91, Бюл, ¹ 31 (72) Я,О.Аввакумов (5З) 621.376.6 (088.8) (56) Авторское свидетельство С Г Р

¹1262688,,кл. Н 03 С 5/00, 1985. (54) ФОРМИРОВАТЕЛЬ СИГНАЛОВ С АМПЛИТУДНОЙ И УГЛОВОЙ МОДУЛЯЦИЕЙ (57) Изобретение относится к радиотехнике и может использоваться в системах передачи сигналов с амплитудной и угловой модуляцией. Цель изобретения — расщирение диапазона частот формируемого сигнала, Формирователь сигч лов с амплитуд;ой и угловой модуляцией содержит генера1ор тактовых импульсов, двоичный сумматор 2, первый регистр 3 памя и, первый блок 4 постояннои памяти, цифроаналоговый преобразователь 5, второй регистр 9 памяти.

Изобретение относится к радиотехнике и может использоваться -:, сис. емах передачи сигналов с лмплитуднои и угловой модуляцией.

Цель изобретения — расширение диапазона ча";or формируем ; о сигнала, На чертеже представлена электрическая схема предложенного формирователя, Формирователь сигналов с амплитудной и угловой модул цией содержит i онерагор 1 TBKToohlx импульсов,, воичный сук матор ?, первый регистр памяти. первый блок 4 посточнной памяти, цифроаналоговый преобразо атель 5, пеоемножающий цифроаналоговый преобразователь 6, 50, 1672551 А1

Цель достигается введением перемножающе"о цифроаналогового преобразователя 6, фильтра 7 нижних частот, второго блока 8 постоянной памяти. Сумматор 2 и регистр

3 образуют накопительный сумматор, который используется в качестве делителя частоты с дробно-переменным коэффициентом деления. На выходе блока 8 появгяется код амплитуды синусоидального колебания, соответствующий текущей фазе формируемого сигнала. Преобразователь 5 преобразует его в напряжение, которое пост пает на пресбразоватень 6 на цифрово . вход кот .1роrо с второ; о вы ода блока 4 поступает код тек,щего: Гачения амглитудь, формируемого сигнала. Фильтр 7 нижних частот очищает спектр формируемого сигнглг от помех кг чтования с частотой, равчой частоте следования импульсов с выхода reriepa ор ; 1.

1 ил.

ciил„гр 7 нижних частот, второй блок 8 постоян чои памяти и второй регис р 9 гав.яти.

Формирователь работает следующим образом.

Мод,лирующий сигнал поступает на сигнальчый вход второго регистра 9 памяти и запи" веется в него по приходу на его вход синхронизации импульса с выхода генер=..тооа 1 тактовых имоульсоч. Это обеспечигает синхронизацчю модулирующего сивина з импульсами o ..ыхода генератора 1 тактовых импульсов, чем ус- ранчется возможHocTb сбоев в работе формирователя сигналов с амплитудной и угловои модуляцией из-за изменения модулирующего сигнала на интервале времени между

1 ! и

1 а ) ! (у

jQI !

1672551

15 приходом соседних импульсов с выхода генератора 1 тактовых импупьсое.

С выхода второго регистра 9 памяти модулирующий сигнал поступает на адресный вход первого бпока 4 постоянной памяти, в котором в двоичном коде хранятся численные значения приращения фазы формируемого сигнала за период частоты следования импульсов с выхода генератора 1 тактовых импульсов и численные значения текущей амплитуды формируемого сигнала на интервале между приходом соседних импульсов с выхода генератора 1 тактовых импульсов. Законы изменения численных значений приращения фазы и текущей амплитуды формируемого сигнала в соответствии с модулирующим сигналом выбирают, исходя из требований получения минимального уровня внеполосового излучения, С первого выхода первого блока 4 код приращения фазы поступает на первый вход двоичного сумматора 2. Выход двоич, ного сумматора 2 соединен с сигнальным входом первого регистра 3 памяти, в котором хранится код текущего значения фазы формируемого сигнала, Сигналы с выходов всех разрядов первого регистра 3 памяти поступают на второй вход двоичного сумматора 2, Таким образом, на выходе двоичного сумматора 2 присутствует код вновь вычисленного значения фазы формируемого сигнала, равный сумме кода текущего значения фазы формируемого сигнала с выхода первого регистра 3 памяти и кода приращения фазы формируемого сигнала с первого вы хода первого блока 4. По приходу каждого импульса с выхода генератора 1 тактовых импульсов на вход синхронизации первого регистра 3 памяти в него записывается вновь вычисленное значение кода фазы формируемого сигнала, которое после этого становится текущим значением кода фазы формируемого сигнала, Таким образом, двоичный сумматор 2 и первый регистр 3 памяти образует так называемый накопительный сумматор, который в данном случае используется в качестве делителя частоты с дробно-переменным коэффициентом деления. Частота F формируемого сигнала, получаемого с помощью этого делителя, определяется по формуле

F =F0 (1)

2М где F - частота формируемого сигнала;

FO — частота следования импульсов с выхода генератора 1 тактовых импульсов;

— код приращения фазы формируемого сигнала;

0F — число двоичных разрядов двоичного сумматора 2 и первого регистра 3 памяти.

Минимально возможное изменение частоты формируемого сигнала (шаг сетки частот AF) получается при изменении кода

В приращения фазы на единицу младшего разряда и определяет я по формуле ог (2)

FO

При необходимости s течение одного периода частоты следования импульсов с выхода генератора 2 тактовых импульсов изменить фазу формируемого сигнала на величину Arp производят изменение кода приращения фазы формируемого сигнала на величину Л В, определяемую по формуле

ЛВ =- 2, (3)

Сигналы с выходов N старших разрядов первого регистра 3 памяти поступают на адресный вход второго блока 8 постоянной памяти, в котором хранятся численные значения выборов одного периода синусоидального колебания. При поступлении на адресный вход второго блока 8 постоянней памяти текущего значения кода фазы формируемого сигнала с выходов N старших разрядов первого регистра 3 памяти на выходе второго блока 8 постоянной паМяти появляется код ампли гуды синусоидального колебания, соответствующий текущей фазе формируемого сигнала, Этст код поступает на цифровой вход цифроаналогового преобразователя 5, с помощью которого он преобразуется в аналоговое напряжение.

С выхода цифроаналогового преобразователя 5 аналоговый синусоидапьньй сигнал с постоянной амплитудой поступает на вход опорного напряжения перемножающего цифроаналогового преобразователя 6, на цифровой вход которого с второго выхода первого блока 4 постоянной памяти поступает код AT текущего значения амплитуды формируемого сигнала. Амплитуда А сигнала на выходе перемножающего цифроаналогового преобразователя 6 определяется по формуле

A=AO "„„, (4)

2 " где Л вЂ” амплитуда формируемого сигна»а на выходе перемножающего цифроаналогового преобразователя 6;

АΠ— амплитуда сигнала на выходе цифроаналогового преобразователя 5;

AT — код текущего значения амплитуды формируемого сигнала, 1672551

DA — число двоичных разрядов цифоового входа перемножэющего цифроаналогового преобразователя 6.

Аналоговый сигнал с выхода перемножающего цифроаналогового преобраэова- 5 теля 6 поступает на фильтр 7 нижних частот, который служит для очищения спектра фоомируемого сигнала от помех квантования с частотой, равной частоте следования импульсов с выхода генератора 1 тактовых им- 10 пульсов.

Таким образом, на выходе фильтра 7 нижних частот присутствует аналоговый синусоидальный сигнал с амплитудой, определяемой по формуле (4), и частотой, 15 определяемой по формуле (1). Причем шаг

A F сетки частот формируемого сигнала на выходе предложенного формирователя сигналов с амплитудной и угловой модуляциями значительно меньше, чем в известном фор- 20 мирователе сигналов с амплитудной и угловой модуляциями при одинаковом объеме первого блока 4 постоянной памяти. Это объясняется тем, что для формирования сигнала с постоянными амплитудой, часто- 25 той и фазой, т.е. элементарного сигнала, иэ набора которых можно сформировать требуемый закон изменения амплитуды, частоты или фазы, в предложенном формироВоТ-ëå с1ггналсв с амплиудной и уговой, д модуляциями требуется хранение в первом блоке 4 пос янн;>й памяти только о>..ного многораэряд ого .-. ова, состоя <е о из кода

Б приращения фаза и из кода AT текущей амплитуды формируемо о сигнала. При 35 этом число 0Р ячеек памяти в первом блоке

4 постоянной памяти, требуемых для хранения информации о сигнале с постоянными амплитудой, частотой и фазой определяе ся по формуле

ОР = DF+ DA. (5)

Формула изобретения

Формирователь сиг алов с амплитудной и угловой модуляцией, содержащий цифроаналоговый преобразователь и генератор тактовых импульсов, выход которого подключен к синхронизационным входам первого регистра памяти, выходы разрядов которого соединены с первым входом двоичного сумматора, и второго регистра памяти, выход которого подключен к адресному входу первого блока постоянной памяти, при этом сигнальный вход второго регистра памяти является модулирующим входом формирователя, отличающийся тем, что, с целью расширения диапазона частот формируемого сигнала, в него введены второй блок постоянной памяти и последовательно соединенные перемножающий цифроаналоговый преобразователь и фильтр нижних частот, выход которого является выходом формирователя, причем первый и второй выходы первого блока постоянной памяти подключены соответственно к второму входу двоичного сумматора, выход которого соединен с сиrHàëьным входо; ° первого регистра памяти, и к цифрое у входу перемножвющегс ц :Фроан ..логового г;реобрэзоввтеля, опорный вход которого соединен с выходом цифроаналогоап.о преобразователя, к входу которого подключен выход второго блока постоянной гамят, адресный вход которого .:оединен с выходами тарших разрядов пере го ое истра памяти.

1672551

Составитель В, Чибисов

Редактор Т. Иванова Техред М.Моргентал Корректор М, Кучерявая

Заказ 2845 Тираж 424 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул.Гагарина, 101