Цифровой фильтр

Иллюстрации

Показать всеРеферат

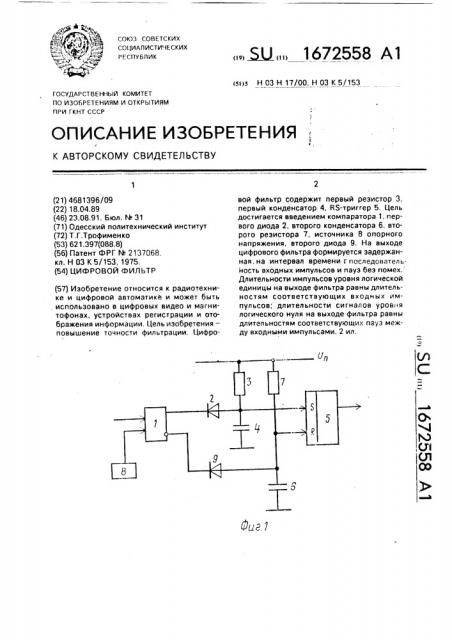

Изобретение относится к радиотехнике и цифровой автоматике и может быть использовано в цифровых видео-магнитофонах, устройствах регистрации и отображения информации. Цель изобретения - повышение точности фильтрации. Цифровой фильтр содержит первый резистор 3, первый конденсатор 4, RS - триггер 5. Цель достигается введением компаратора 1, первого диода 2, второго конденсатора 6, второго резистора 7, источника 8 опорного напряжения, второго диода 9. На выходе цифрового фильтра формируется задержанная на интервал времени &Tgr; последовательность входных импульсов и пауз без помех. Длительности импульсов уровня логической единицы на выходе фильтра равны длительностям соответствующих входных импульсов длительности сигналов уровня логического нуля на выходе фильтра равны длительностям соответствующих пауз между входными импульсами. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК вЂ” ф ф

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

4 с.) ,(Jl

jQl

ОО

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4681396/09 (22) 18.04.89 (46) 23.08.91. Бюл. N 31 (71) Одесский политехнический институт (72) Т, Г.Трофименко (53) 621.397(088,8) (56) Патент ФРГ М 2137068, кл. Н 03 К 5/153, 1975, (54) ЦИФРОВОЙ ФИЛЬТР (57) Изобретение относится к радиотехнике и цифровой автоматике и может быть использовано в цифровых видео и магнитофонах, устройствах регистрации и отображения информации. Цель изобретения— повышение точности фильтрации, Цифро Ж 1672558 А1

rsi)s Н 03 Н 17/00, Н 03 К 5/153 вой фильтр содержит первый резистор 3, первый конденсатор 4, RS-триггер 5. Цель достигается введением компаратора 1, первого диода 2, второго конденсатора 6, второго резистора 7, источника 8 опорного напряжения, второго диода 9. На выходе цифрового фильтра формируется задержанная, на интервал времени Г последователь ность входных импульсов и пауз без помех.

Длительности импульсов уровня логической, единицы на выходе фильтра равны длительностям соответствующих входных импульсов, длительности сигналов уров tA логического нуля на выходе фильтра равны длительностям соответствующих пауз между входными импульсами. 2 ил, 1672558 формула изобретения

Таким образом, на выходе цифрового фильтра формируется задержанная на интервал времени т последовательность входных импульсов и пауз без помех. Причем длительности импульсов уровня логической единицы на выходе фильтра равны длительностям соответствующих входных импульсов, длительности сигналов уровня логического нуля на выходе фильтра равны длительностям соответствующих пауз между входными импульсами. ю-а arPcr

fð яной

Аио коюца6 Р

КонйнCaioP 7

Кснденспто б

Быка

Р июьтЬв

Составитель С,Муэычук

Техред M,Ìîðãåíòàë Корректор T.Малец

Редактор А,Козориз

Заказ 2846 Тираж 433 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва. Ж-35, Раушская наб„4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул,Гагарина, 101

Таким образом, R- и на $-входах триггера 5 в течение (t> + t) имеют место сигналы уровня логического нуля, что не меняет состояния RS-триггера (фиг. 2ж) (он остается в нулевом состоянии). В момент, когда уровень сигнала на входе фильтра снова снизится ниже опорного (фиг. 2а), т.е. исчезнет импульс помехи, на инверсном выходе компаратора 1 сформируется сигнал уровня логической единицы, который через время задержки поступит на R-вход триггера 5 (фиг. 2е), но это не изменит состояния триггера 5, он останется в нулевом состоянии (фиг, 2ж), Цифровой фильтр, содержащий RSтриггер, первый резистор и первый конден5 сатор, первая обкладка которого соединена с первым выводом первого резистора, о тл и ч а ю шийся тем, что, с целью повышения точности фильтрации, введены компаратор, первый вход которого является

10 входом цифрового фильтра, два диода, вторые резистор и конденсатор и источник опорного напряжения, выход которого соединен с вторым входом компаратора, прямой и инверсный выходы которого под15 ключены к катодам первого и второго диодов соответственно, анод первого диода соединен с первой обкладкой первого конденсатора и входом установки RS-триггера, вход сброса которого соединен с анодом

20 второго диода, первой обкладкой второго конденсатора и первым выводом второго резистора. причем вторые выводы первого и второго резисторов соединены с шиной питания, а вторые обкладки первого и вто25 рого конденсаторов соединены с общей шиной.