Устройство для приема информации

Иллюстрации

Показать всеРеферат

Изобретение относится к электросвязи, вычислительной технике и может быть использовано в устройствах последовательной передачи информации. Цель изобретения - повышение помехоустойчивости устройства при наличии флуктуационных помех во входном сигнале и расширение его функциональных возможностей путем обеспечения приема биполярных двухфазных кодов без нулевого уровня между битами. Устройство содержит информационные входы 1, линейный блок 2, элементы И-НЕ 3, 4, 7, 8, триггеры 5, 6, 10, 15, 28, элементы ИЛИ 9, 14, элемент И 29, элементы НЕ 19, 20, 30, блоки 16, 24, 35 задержки, резисторы 17, 21, 25, 31, 32, конденсаторы 18, 22, 26, оптроны 33, 34 и шину 23 единичного потенциала. 3 ил.

б

C (.Í:>3 СОВГ ГСКИХ сО!1иАлис ги ГР ских

Pf- СПУ6ЛИК (я)5 Н 03 М 5/18

f ОСУДАРСТВЕННЫИ КОМИТГТ

ПО ИЗО6РЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

Г

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Ы (у 4 (21) 4499687/24 (22) 28.10.88 (46) 23.08.91. Бюл. ¹ 31 (72) В.Е.Амбарцумов. А,Ю.Болдырев и А.А.Борисенко (53) 621.374(088.8) (56) Авторское свидетельство СССР

¹ 1051708, кл. Н 03 К 13/24, 1982.

Авторское свидетельство СССР

¹ 1444955, кл. Н 03 М 5/18, 1987. (54) УСТРОЙСТВО ДЛЯ ПРИЕМА ИНФОРМАЦИИ (57) Изобретение относится к электросвязи, вычислительной технике и может быть использовано е устройствах последовательИзобретение относится к электросвязи и вычислительной технике и может быть использовано в устройствах последовательной передачи информации.

Цель изобретения повышение помехоустойчивости устройства при наличии флуктуационных помех во входном сигнале и расширение его функциональных возможностей путем обеспечения приема биполярных двухфазных кодов без нулевого уровня между битами.

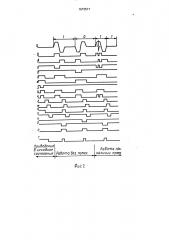

На фиг, 1 представлена принципиальная функциональная схема устройства; на фиг. 2, 3 — временные диаграммы, поясняющие работу устройства.

Устройство для приема информации содержит (см. фиг. 1) информационные входы

1, линейный блок 2, первый, второй элементы И вЂ” НЕ 3, 4, первый. второй RS-триггеры 5, 6, третий, четвертый элементы И-НЕ 7, 8, первый элемент ИЛИ 9, третий D-триггер 10, SLY„„1672571 А1 ной передачи информации. Цель изобретения — повышение помехоустойчивости устройства при наличии флуктуационных помех во входном сигнале и расширение его функциональных воэможностей путем обеспечения приема биполярных двухфазных кодов без нулевого уровня между битами.

Устройство содержит информационные входы 1, линейный блок 2, элементы И вЂ” НЕ 3, 4, 7, 8, триггеры 5, 6, 10, 15, 28, элементы ИЛИ

9, 14, элемент И 29, элементы НЕ 19, 20, 30, блоки 16, 24, 35 задержки, резисторы 17, 21, 25, 31, 32, конденсаторы 18, 22, 26, оптроны

33, 34 и шину 23 единичного потенциала.

3 ил. информационный и тактовый выходы 11 и 12 устройства, вход 13 "Сброс" устройства, второй элемент ИЛИ 14, четвертый О-триггер 15, первый блок 16 задержки, выполненный на резисторе 17, конденсаторе 18, элементах НЕ 19, 20, второи блок 35 задержки, выполненный на резисторе 21, конденсаторе 22, шину 23 единичного потенциала, третий блок 24 задержки, выполненный на резисторе 25, конденсаторе 26 и элементе

ИЛИ 27, пятый О-триггер 28, элемент И 29, элемент НЕ 30. Линейный блок 2 выполнен на резисторах 31, 32 и оптронах 33, 34.

Устройство работает следующим образом, Импульс сброса при включении питания поступает на вход 13 "Сброс" устройства и через элемент ИЛИ 9 и блок 24 задержки по фронту устанавливает триггер 15 в единичное состояние. Через время, формируемое блоком 35 задержки, с выхода элемента НЕ

1672571

30 на вход триггера 10 пос1упает сигнал, устанавливающий его в исходное нулевое состояние, а через время, формируемое блоком 16 задержки, триггеры 5, 6, 15, 28 также устанавливаются в исходное нулевое состояние. На выходах 11, 12 устройства устанавливается логический нуль. В случае поступления на вход 1 устройства положи1ельной полуволны единичной посылки сигнала, содержащего нулевые уровни между битами (см. фиг. 2а), на первом выходе блока

2 формируется импульс (см. фиг. 2б), который через элемент И-НЕ 3 (см. фиг. 2г) устанавливает тритгер 5 в единичное состояние (см. фиг. 2е), Этот же импульс через элемент

ИЛИ 9 поступает на третий блок 24 задержки (см. фиг, 2к), с выхода которого задержанный импульс (см. фи . 2и) поступает на триггеры 15 и 28, срабатывающие по заднему франту импульса (cM, фиг. 2л, н). Триггер

28 дает разрешение на элемент И 29 для ттрохаждения тактового импульса, сформированного а|рицательной полуволнай единичной т1ас!лпки, который формируется на втором выходе блока 2 (см, фиг. 2в). При совпадении сигналов на входах элемента

И вЂ” НЕ 8 отрицательный импульс(см. фиг, 2р) с его выхода поступает через элемент ИЛИ

14 в виде положительного импульса (cM. фиг. 2с) на вход элемента И 29 и информационный вход триггера 28, Триггер 28 сраба1ывлет пп заднему фронту импульса (см. фиг. 2и) при появлении на информационном входе rpvrrepa 28 положительного импульса, сформированного ат отрицательной попувалны биимпульснай посылки (см. фиг. 2с).

Затем триггер 28 открывает элемент И 29 и триггер 10 срабатывает по переднему фронту импульса с выхода элемента ИЛИ 14 (см, фиг. 2с). С триггера 10 передний фронт тактового импульса поступает на выход 12 устраиства (см, фиг, 2у). Положительный перепад с триггера 15, задержанный в блоке

35 задержки (см. фиг. 2м), через элементы

НЕ 30 выдается для формирования заднего фронта тактового импульса на выходе 12 устройства (см, фиг. 2у). Величина задержки в блоке 35 задержки выбирается из расчета

T Т вЂ” — < Г-,д <

2 где т;,1л — время задержки;

Т вЂ” длитепт.ность импульса положительной или а1рица ельнай полуволны биимпупьснато си нала.

Г1а импульсу сброса (см. фиг. 2м), сформированному блоком 16 задержки, триггеры 5, 6, 28, 15 устанапт1иваются в исходное состояние и н:3 выходе 11 устанавливается логичт-ской ну t,. Г!ри этом отрицательный перепад на выходе триггера 15 поступает через блок 35 задержки, элемент НЕ 30 и блок 16 задержки на сбросовые входы триггеров 5, 6, 10, 15, 28, устанавливая их в рабочее состояние и разрешая прохождение следующих посылок с информационных входов устройства. Величина задержки блока 16 задержки выбирается из расчета, что время задержки iaaa должно перекрывать окончание второй полуволны биимпульсной посылки. Аналогично работает устройство при вступлении на вход биимпульсного сигнала, соответствующего нулевой посылке на входе 1, В этом случае переключается триггер 6. На выходе I! отсутствует импульс (см. фиг. 2а, в, е), При поступлении на вход

1 флуктуационной помехи, наложенной на полуволну биимпульсной посылки (см, фиг.

2а), на выходах блока 2 формируются дополнительные короткие импульсы, но они не вызывают срабатывания триггеров 15 и 10, так как блокируются блоком 24 задержки.

Нормальная работа устройства обеспечивается лишь тогда, когда за положительной полуволной обязательно следует отрицательная полуволна, и наоборот. Исходя иэ этого, величина задержки в блоке 24 задержки должна быть такова, чтобы одна полуволна давала "разрешение" на прохождение другой полуволны. Кроме того, величина задержки выбирается, исходя из ожидаемой длительности полуволны флуктуационной помехи т„

Т т-.„„< т.„д <—

8 где балх — длительность фпуктуационной помехи; т„д — величина задержки блока 24 задержки;

Т вЂ” длительность импульса полуволны биимпульсного сигнала.

Таким образом отрицательная и положительная полуволны флуктуационной помехи блокируются блоком 24 задержки, не проходят на триггеры 15 и 28 и не нарушают работу устройства. В случае, когда на вход устройства подается биполярный двухфазный код без нулевого уровня между битами (см, фиг, За) декодирование первой положительной и первой отрицательной полуволн биимпульсной посылки происходит аналогично описанному выше, причем начало формирования импульса сброса происходит по заднему фронту первой полуволны первой биимпульсной посылки, а действие импульса сброса происходи1 во воемя действия второй полувалны первой биимпульсной посылки и заканчивается в начале первой полуволны последующей (второй) 1672571 биимпульсной посылки. По окончании импульса сброса происходит снятие запрета с элемента И-НЕ, э действующая в это время первая полуволна второй биимпульсной посылки проходит через элемент И-НЕ 3 (см. 5 фиг. 1 — 3) взводит триггер 5. Таким образом происходит дальнейшая обработка последующих посылок.

Формула изобретения 10

Устройство для приема информации, содержащее элемент НЕ, линейный блок. входы которого являются информационными входами устройства, первый и второй выходы линейного блока соединены соот- 15 ветственно с первыми входами первого, второго, третьего и четвертого элементов

И-НЕ, выходы первого и третьего элементов И-НЕ соединены соответственно с входом установки в "1" первого триггера, 20 первым инверсным входом первого элемента ИЛИ и входом установки в "1" второго триггера, вторым инверсным входом первого элемента ИЛИ, прямой выход первого триггера соединен с вторым входом четвер- 25 того элемента И вЂ” НЕ и является информационным выходом устройства, инверсный выход первого триггера соединен с вторым входом третьего элемента И--НЕ прямой выход второго григгера соединен с вторым 30 входом второго элемен1" И вЂ” НЕ, инверсный выход второ о триггера соединен с вторым входом первого элемента И вЂ” НЕ, выходы второго и четвертого элементов И-НЕ соединены с инверсными входами второго эле- 35 мента ИЛИ, третий инверсный вход первого элемента ИЛИ является входом "Сброс" устройства, вход первого блока задержки соединен с входом установки в "0" третьего триггера, информационный вход которого подключен к шине единичного потенциала, прямой выход третьего триггера является тактовым выходом устройства, выход первого блока задержки соединен с установочными входами в "0" первого. второго и четвертого триггеров, информационный вход четвертого триггера подключен к шине единичного потенциала, прямой выход соединен с входом второго блока задержки, о т л и ч а ю щ е е с я тем, что, с целью повышения помехоустойчивости устройства при наличии флуктуационных помех во входном сигнале и расширения его функциональных возможностей путем обеспечения приема биполярных двухфазных кодов без нулевого уровня между битами, в него введены третий блок задержки, пятый триггер и элемент И, первый вход которого объединен с информационным входом пятого триггера и подключен к выходу второго элемента ИЛИ, вход установки в "0" пятого триггера объединен с третьими входами первого, третьего элементов И-НЕ и подключен к выходу первого блока задержки, вход третьего блока задержки соединен с выходом первого элемента ИЛИ, выход подключен к тактовым входам пятого и четвертого триггеров, прямой выход пятого . риггера соединен с вторым входом элемента И, выход которого подключен к тактовому входу третьего триггера, вход и выход элемента НЕ подключены соответственно к выходу второго блока задержки и входу первого блока задержки.

1672571

К

Л

М

П

P иг2

1672571

Работа без помех Рабогпа при на очии nones

Составитель С.Левичев

Техред М,Моргентал Корректор Т.Малец

Редактор Т.Шагова

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина. 101

Заказ 2846 Тираж 435 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5