Й счетчик в коде грея

Иллюстрации

Показать всеРеферат

167365

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистицеских

Республик

Зависимое от авт. свидетельства №

Заявлено 02.11.1963 (№ 817375/26-24) с присоединением заявки №

Приоритет

Опубликовано 04.1.!965. Бюллетень ¹ 1

Дата опубликования описания 29.1.1965

Кл. 42m, 14оа

Государственный комитет по делам изобретений и открытий СССР

МПК G 06(j

УДК 681, 142(088.8) Авторы изобретсния

Ю. С. Манукян, М. В. Чхеидзе, В. Г. Христесашвили и Г. А. Мачавариани

3 а явитель

РЕВЕРСИВНЫЙ СЧЕТЧИК В КОДЕ ГРЕЯ

Подписная группа JH 145

Известны реверсивные счетчики в коде

Грея, содержащие регистр из триггеров со счетным входом, триггер четности и упра вляюшие схемы совпадения, которые включаются либо параллельным, либо последовательным способом.

Предложенный счетчик отличается от известных тем, что счетный вход каждого триггера регистра соединен с выходом схемы совпадения предыдущего разряда. Один вход схемы совпадения подключен к единичному выходу триггера одноименного разряда; второй— к отводу от выхода предыдущей секции линии сквозного переноса, состоящей из последовательно соединенных и параллельно управляемых от одноименных триггеров регистра вентилей; а третий — к выходу схемы совпадения для четных входных импульсов, соединенной с единичным выходом триггера четности.

Счетный вход триггера первого разряда соединен с выходом схемы совпадения для нечетных входных импульсов, один вход которой подключен к нулевому выходу триггера четности, счетный вход которого соединен через линию задержки и схему «ИЛИ» со входом счетчика и входом реверса. Это позволяет уменьшить ошибку при считывании информации в процессе счета, стабилизировать нагрузку для источника входных импульсов и упростить схему при большом числе разрядов.

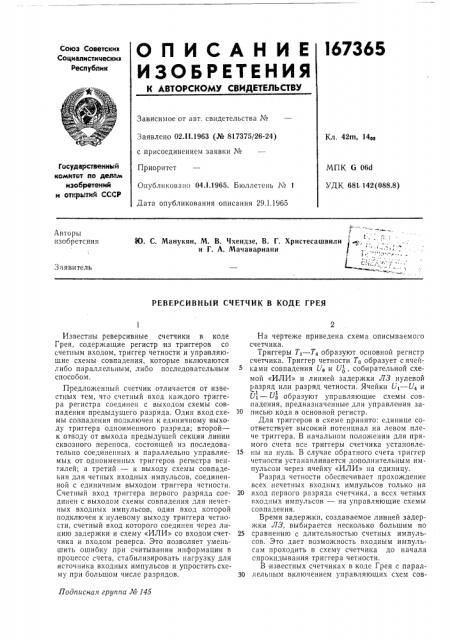

На чертеже приведена схема описываемого счетчика.

Триггеры T> — Т4 образуют основной регистр счетчика. Триггер четности Т<> образует с ячейками совпадения Uo u U, собирательной схемой «ИЛИ» и линией задержки ЛЗ нулевой разряд или разряд четности. Ячейки U> — U4 и

-1 1

U> — Ua образуют управляющие схемы совпадения, предназначенные для управления за10 писью кода в основной регистр.

Для триггеров в схеме принято: единице соответствует высокий потенциал на левом плече триггера. В начальном положении для прямого счета все триггеры счетчика установле15 ны на нуль. В случае обратного счета триггер четности устанавливается дополнительным импульсом через ячейку «ИЛИ» па единицу.

Разряд четности обеспечивает прохождение всех нечетных входных импульсов только на

20 вход первого разряда счетчика, а всех четных входных импульсов — на управляющие схемы совпадения.

Время задержки, создаваемое линией задержки ЛЗ, выбирается несколько большим по

25 сравнению с длительностью счетных импульсов. Это дает возможность входным импульсам проходить в схему счетчика до начала спрокидывания триггера четности.

В известных счетчиках в коде Грея с парал30 лельным включением управляющих схем сов167365

Предмет изобретения

Составитель Т. Бакина

Редактор П. Шлаин

Техред Ю. В. Баранов Корректор Ю. М. Федулова

Заказ 3741/15 Тираж 825 Формат бум. 60 X 901/8 Объем 0,16 изд. л. Цена 5 коп.

ЦНИИПИ Государственного комитета по делам изобретений и открытий СССР

Москва, Центр, пр. Серова, д. 4

Типография, пр. Сапунова, 2 падения, сложность системы зависит от разрядности счетчика.

В счетчиках же с последовательным вклю° чением - схем совпадения интервал времени между моментом прихода счетного импульса и моментом соответствующего переключения в счетчике непостоянен даже для периодических импульсных последовательностей на входе, что значительно увеличивает вероятность ошибки при съеме показаний в процессе счета.

В описываемом счетчике структура включения управляющих схем совпадения последовательно-параллельная.

1 1

Ячейки U> — U а составляют линию сквозного переноса, непосредственно же функции управления выполняют ячейки Ут — U4, к которым одновременно подводятся четные входные сигналы.

Такая структура обеспечивает изменение записи в счетчике от каждого счетного импульса сразу же после его поступления на счетчик, в результате чего уменьшается вероятность ошибки при снятии показаний в процессе счета и стабилизируется нагрузка для источника входных импульсов, что снижает требования к формированию на входе счетчика.

Рассмотренный счетчик обладает идентичной структурой во всех разрядах и отличается большой простотой; наличие же цепи сквозного переноса обеспечивает высокое быстродействие.

Приведенные отличия делают полезным применение описанного счетчика в цифровых системах автоматического регулирования и управления и в частности в многоканальных аналогоцифровых преобразователях с разверткой каналов по напряжению.

Рвверсивный счетчик в коде Грея, содержащий регистр из триггеров со счетным входом, триггер четности и управляющие схемы совпадения, отличающийся тем, что с целью уменьшения ошибок при считывании информации в процессе счета, стабилизации цагрузки для источника входных импульсовн и упрощения

15 схемы при оольшом числе разрядов, счетный вход каждого триггера регистра соединен с выходом схемы совпадения предыдущего разряда, один вход которой подключен к единичному выходу триггера одноименного разряда, 20 второй — к отводу от выхода предыдущей секции линии сквозного переноса, состоящей из последовательно соединенных и параллельно управляемых от одноименных триггеров регистра вентилей, а третий — к выходу схемы сов25 падения для четных входных импульсов, соединенной с единичным выходом триггера четности; счетный вход триггера первого разряда соединен с выходом схемы совпадения для нечетных входных импульсов, один вход кото30 рой подключен к нулевому выходу триггера четносги, счетный вход которого соединен через линию задержки и схему «ИЛИ» со входом счетчика и входом реверса,