Вычислительное устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для деления чисел, представленных в формате с фиксированной запятой. Цель изобретения - расширение функциональных возможностей за счет реализации операции деления чисел. Новым в устройстве, содержащем дешифратор 1 старшей единицы кода делителя, первый 2 и второй 4 блоки сдвига, блок 5 формирования базисной функции, является введение умножителя 7, что позволило в устройстве выполнять не только операцию вычисления обратной величины, но и операцию деления чисел. 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)5 G 06 F 7/52

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ1

К ABTOPCKGMY СВИДЕТЕЛЬСТВУ

В (21) 4440876/24 (22) 14.04.88 (46) 30.08,91. Бюл, N 32 (72) А.С.Просочкин, С.Ф,Свиньин и Е,С.Тулуза ков (53) 681,325 (088.8) (56) Авторское свидетельство СССР

М 1262480, кл, 6 06 F 7/52, 1985.

Авторское свидетельство СССР

М 676986, кл, 6 06 F 7/38, 1978. (54) ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО (57) Изобретение относится к вычислительной технике и может быть использовано для

Изобретение относится к вычислительной технике и может быть использовано для деления чисел, представленных в формате с фиксированной запятой.

Цель изобретения — расширение функциональных возможностей за счет реализации операции деления чисел.

Вычисление отношения у/х основано на кусочной аппроксимации функции 1/х, причем длина участков аппроксимации пропорциональна целочисленным степеням двойки, Для вычисления функции Z = у/х на

1-м участке аппроксимации (! = О, 1...„п — 1; и — число разрядов делителя) используется соотношение

Z= — =" p{z), xE(x>, х + Лх ), (1) х х где х — значение аргумента х, соответствующее началу 1-го участка аппроксимации;

Ьх — длина i-ro участка аппроксимации; р {z} =- 1/{т+ 1) — базисная функция.

Если x E (0; 2" — 1), то в формуле (1) х = 2", i = 0,1,...,п-1;

Ьxi = xi-1 — х = xi, .. Ж 1674109 А1 деления чисел, представленных в формате с фиксированной запятой. Цель изобретения —;асширение функциональных возможностей за счет реализации операции деления чисел. Новым в устройстве, содержащем дешифратор 1 старшей единицы кода делителя, первый 2 и второй 4 блоки сдвига, блок 5 формирования базисной функции, является введение умножителя

7, что позволило в устройстве выполнять не только операцию вычисления обратной величины, но и операцию деления чисел.

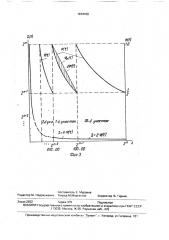

3 ил. следовательно, нулевому участку аппроксимации (i = О) соответствует код хо = 100...00, первому участку -х1 = 010...00 и т.д. Таким образом, деление у/х сводится к соответствующему сдвигу делимого у.

Величина z характеризует изменение . кода делителя внутри участка аппроксимации х-xj х-xi

hxi xi

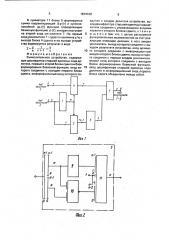

x E (х;:; 2xi), z E (О; 1), На фиг. 1 приведена функциональная схема устройства; на фиг. 2 — пример реализации блока формирования базисной функции; на фиг. 3 — графики функций p{z}, Z = 2" /х, поясняющие работу устройства.

Вычислительное устройство (фиг. 1) содержит дешифратор 1 старшей единицы кода делителя, первый блок 2 сдвига, вход 3 делителя устройства, второй блок 4 сдвига, блок 5 формирования базисной функции, вход 6 делимого устройства, умножитель 7, выход результата 8 устройства.

1674109

Блок 5 формирования базисной функции (фиг. 2) содержит блок 9 памяти, блок 10 инверторов, сумматор 11.

Код номера участка формируется дешифратором старшей единицы кода делителя и определяет величину сдвига делимого, необходимую для получения отношения у/хь а также величину сдвига делителя х, требуемую для получения нормированного значения т; Блок формирования базисной функции вычисляет значение функции p(t), единичной для всех участков аппроксимации, которое умножается затем на величину.

Устройства работает следующим образом, Код делителя посгупает с входа 3 на вход дешифратара i, который определяет положение крайней левай единицы кода.

Если обозначить МΠ— pecmичный эквивалент выходного кода дешифратара 1, то

Мп-п — 1 — К где k = 0,1...,п-1 — номер первого слева разряда кода делителя, содержащего единицу.

При этом нулевому коду (МО = О) на выходе дешифратора соответствуеr кулеВОЙ участок аппрОксимации с начальным значением делителя х<; -- 100„.„00 (см, фиг. 3), коду Мо = 1 — первый участок с x = 01О,...,ОО и т.д. Код с выхода дешифратора 1 поступает на управляющие Входы боков 2, 4 Сдвига.

Блок 4 сдвига формирует величину у/х ny" тем соответствующего сдвига вправо када делимого у.

Блок 2 сдвига r,раизводит левый сдвиг кода делителя, необходимый для получения нормированной величины t Е iG; Ц. Например, если Мп = О, то в бг оке 2 сдвига осуществляется нулевой сдвиг кода, при Мп = 1 код делителя сдвигается влево иа один разряд и т.д. (n — 1)-разрядный код, определяющий нормированную величину t; поступает на вход блока 5 формирования базисной функции.

Блок 5 формирования базисной функции (см. фиг. 2) вычисляет ее значение в виде суммы кусочно-линейной рл (т) и корректию щ е й, ф () ф у и к ц и

V(<) =V (<)+ @(

Где фд (r) = 1 — Г/2;

Ьр(т)=1/(r+ i)-, + /2, Кусочно-линейная функция р (г) формируется в виде дополнительного кода величины т/2. Кодтинвертируется В блоке 10 ииверторов и поступает со сдвигом в один разряд(деление нэ дВэ) нэ ВтОрОй ВХОД сумматора 11. При этом старший разряд второго входа сумматора 11 подключен к шине логической единицы устройства. Логиче40

n — 1, при нечетном;

N— — 1, при четном и

M =-и — N, Очевидно, что при увеличении i > N максимальная величина модуля первой производной функции h.Ъ(т) растет пропорционально целочисленным степеням двойки и достигает наибольшего значения при i и — 1, Следовательно, на всех участках

i > N шаг изменения аргумента корректирующей функции должен быть минимальным и равным единице младшего разряда. При уменьшении i < N максимальная величина модуля первой производной уменьшается

От учэсткэ к участку В двэ раза, чта приводит к возможности соответствующего увеличения шага изменения аргумента корректирующей функции. Таким образом, на всех участках i < N для полного определения корректирующей функции AZt(z) достаточно иметь 2 значений функции p (z). ская единица, которую следует прибавить к обратному коду величины r/2 для получения ее дополнительного кода, подается на нулевой разряд первого входа сумматора 11. На

5 Все остальные разряды первого входа сумматора 11 поступает код корректирующей функции Лр (т) с выхода блока 9 памяти.

Можно показать, что для вычисления функции Z = у/х с точностью представления

1G аргументов достаточно определить корректирующую функцию Ap(t) лишь в 2 точках, где М = (и + 1)/2 при и — нечетном и

М = и/2 + 1 при п-четном, С учетом (2) формула (1) преобразуется

15. к виду

Zi (r) =- Y (p, (т) + Л p (r)j, При у = y e c = 2" общая величина корректирующей поправки функции Z апреде20 ляется выражением

Л2 (i) — „Лр(г) .

Найдем N-й участок аппроксимации, на котором максимальная величина модуля первой производной функции А3 (т) равна единице, т.е. шаг изменения функции (шаг ее дискретизации) равен шагу изменения аргумента t. Ha каждом участке аппроксимации максимальное значение модуля первой производной функции ЛЯ (т) соответствует величине r = О и с учетом х = 2 равчО д .(0g 2-и+2! + 1, Из соотношения l(AZtq(0)fl 1 находим

1674109

/od дрюиппгп

В сумматоре 11 блока 5 формиРуется сумма корректирующей Лр(г} и кусочнолинейной rp (т) функций, определяющих базисную функцию p (t), которая поступает на второй вход умножителя 7. На первый вход умножителя 7 подается величина у/xi с выхода блока 4 сдвига и на выходе устройства формируется результат в виде у

xi г+1 х

Формула изобретения

Вычислительное устройство, содержащее дешифратор старшей единицы кода делителя, первый и второй блоки сдвига и блок формирования базисной функции, вход которого соединен с выходом первого блока сдвига, информационный вход которого соединен с входом делителя устройства, выход дешифратора старшей единицы кода делителя соединен с управляющими входами первого и второго блоков сдвига, о т л и ч а5 ю щ е е с я тем, что, с целью расширения функциональных возможностей за счет реализации операции деления, в него введен умножитель, выход которого соединен с выходом результата устройства, вход делимо10 го которого соединен с информационным входом второго блока сдвига, выход которого соединен с первым входом умножителя, второй вход которого соединен с выходом блока формирования базисной функции, 15 вход дешифратора старшей единицы кода делителя и информационный вход первого блока сдвига объединены между собой.

1674109

Составитель Е. Мурзина

Редактор M. Недолуженко Текред М.Моргентал Корректор В, Гирняк

Заказ 2922 Тираж 375 Подписное

ВНИИПИ Го

ИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5 роизводственно-издательский комбинат "Патент", r, Ужгород, ул,Гагарина. 101