Устройство для имитации неисправностей

Иллюстрации

Показать всеРеферат

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при формировании тестов для контроля вычислительных средств. Цель изобретения - расширение перечня имитируемых дефектов. В устройство введены второй дешифратор, второй и третий элементы ИЛИ, блок искажения сигнала, две группы элементов И, третий элемент И. Устройство обеспечивает возможность имитации коротких замыканий между двумя какими-либо шинами вычислительной системы. 1 з.п. ф-лы, 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я 5 6 06 F 11/26

ГОСУДЛР СТ ВЕ ННЬ| И КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21} 4615201/24 (22) 05,12.88 (46) 30,08.91. Бюл, М 32 (72) К.В.Семин, ЮЛ,Спирин и И.Л.Ямутов (53) 681.3 (088.8) (56) Авторское свидетельство СССР

ЬВ 1183972, кл. G Об F 11/26, 1984.

Авторское свидетельство СССР

М 860076, кл, G 06 F 11/26, 1979. (54) УСТРОЙСТВО ДЛЯ ИМИТАЦИИ НЕИС-

ПРАВНОСТЕЙ

Изобретение относится к автоматике и вычислительной технике и может быть использовано при формировании тестов для контроля вычислительных средств.

Цель изобретения — расширение перечня имитируемых неисправностей.

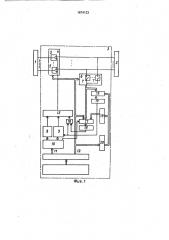

На фиг.1 приведена функциональная схема устройства; на фиг.2 — функциональная схема блока искажения сигналов.

Устройство (фиг,1) содержит вычислительную схему 1, контролируемый узел 2, шифратор 3, коммутатор 4, управляемые каналы 5 коммутатора 4, коммутатор 6, управляемые каналы 7 коммутатора 6, блок задания дефектор 8., блок искажения сигнала 9, дешифратор 10, вход 11 вида дефекта, вход 12 позиционного кода дефекта, элементы ИЛИ 13, 14, 15, две группы элементов

И 16, :.7, элемент И 18 группу элементов НЕ

19„дешифратор 20 выделения крайней единицы.

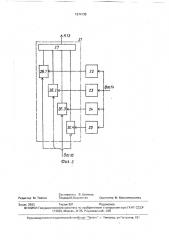

Блок искажения сигналов 9 (фиг.2) содержит мультиплексор 21 и группу узлов искажения, состоящую из: инвертора 22,,, SU,, 1674133 А1 (57 Изобретение относится к области автоматики и зычислительной техники и может быть использовано при формировании тестов для контроля вычислительных средств.

Цель изобретения — расширение перечня имитируемых дефектов, В устройство введены второй дешифратор, второй и третий элементы ИЛИ, блок искажения сигнала, две группы элементов И, третий элемент И. Ус- тройство обеспечивает возможность имитации коротких замыканий между двумя какими-либо шинами вычислительной системыы. 1 з, и. ф-лы, 2 ил. 3 элема |та задержки 23, мультивибратора 24, делителя 25, элемента И 26.1-26.4, элемента ИЛИ 27.

Устройство работает следующим обраЪ.Г

В штатный разъем вычислительной системы 1 включается устройство для имитации неисправностей, к входным контактам кото- О рого подключается контролируемый узел 2.

С входа 11 подается код, задающий вид де- Д фекта, одновременно с этим с входа 12 на коммутаторы 4 и 6 подается код, определяющий позиционный номер канала, в котором имитируется заданный вид дефекта.

При нулевых значениях всех разрядов позиционного кода на входе 12 сигналы с выхода контролируемого узла 2, минуя устройство, а поступают на вход вычислительной системы

1. Если в каком-либо разряде позиционного кода на входе 12 появляется единица, то коммутаторы 4 и 6 переходят- в состояние, когда сигналы соответствующего канала с выхода узла 2 поступают на вход коммутатора 6, а вместо него на выходе коммутатора

1674133

4 на этом же канале имитируется дефект или искажение сигнала.

Для этого код cвхо:,да 11 поступает на дешифратор 10, который определяет вид дефекта или искажения сигнала с помошью 5

Выходного сигнала дешифратора 10 на выходах блоков 8 или 9 формируется определенный сигнал, который через элемент ИЛИ

13 и соответствующий канал 5 коммутатора

4 поступает на вход Вычислительной систе- 10

Mbl 1, В случае имитации короткого замыкания между какими-либо каналами В соответствующих ДВух разрядах позициОннОГО кода на входе 12 должны присутствовать 15 единицы. Чогда на Выходы коммутатора 6 поступают сиГналы сос1тветству161цих двух каналов, а два соответствующих канала 5 коммутатора 4 перекл1очаются с этих шин на выход элемента ИЛИ 13. 20

Имитация короткого замыкания между двумя шинами производится следующим образом.

Позиционный код, сформированный на 25 входе 12, поступает на коммутаторы 4, 6 и в шифратор 3.

На выходе шифратора 3 формируется код с единицей в самом старшем разряде, которая определяет одну из двух замыкае- 30 мых шин. Э го приводит к подаче на первый

Вход элемента И 18 логической величины.

Номер другой шины выделяется группой элементов И 17 и элементом ИЛИ 15. Группа элементов Yi 17 стробирется сигналом с 35 выхода дешифратора 10, Формула изобретения

1, Устройство для имитации неисправностей, содержащее дешифратор, блок задания дефектов и первый коммугатор, 40 причем группа адресных Входов первого коммутатора является входом задания номера канала устройства, группа выходов первого коммутатора являе.-ся группой выходов устройства, группа информационных 45

ВхОдОВ дешифратора является Входом Вида дефекта устройства, первая группа выходов дешифратора соединена с группой Входов блока задания дефектов, о т л и ч в ю щ е ес я тем, что, с целью расш :1рения перечня 50 имитируемых неисправностей, в него введены дешифратор выделения крайней единицы, три элемента ИЛИ, две группы элементов И, элемент И, группа элементов

НЕ, блок искажения сигнала, второй коммутатор, причем вторая группа выходов дешифратора соединена с группой входов блока искажения сигнала, выходы блока задания дефекта и блка искажения сигнала соединены соответственно с первым и вторым входами первого элемента ИЛИ, Выход которого соединен с информационным входом коммутатора, группа входов задания номера канала устройства соединена с группой адресных входов Второго коммутатора, с первыми входами элементов И первой группы и с группой информационных входов дешифратора Выделения крайней единицы, группа выходов которого соединена с

Входами элементов НЕ группы и с первыми входами элементов И второй группы, выходы которых соединены с группой входов второго элемента ИЛИ, выход которого соединен с входом блока искажения сигналов и с первым входом элемента И, выход которого соединен с третьим входом первого элемента ИЛИ, группа выходов второго коммутатора соединена с вторыми входами элементов И первой и В орой групп, третьи входы элементов И первой группы соединены с выходами элементов НЕ группы, выходы элементов И первой группы соединены с группой Входов третьего элемента ИЛИ, выход которого соединен с вторым входом элемента И, Входы стробирования элементов И первой группы соединены с выходом дешифратора, группа информацирнных sxoдов устройства соединена с группами информационных входов первого и второго . коммутаторов.

2. Устройство по п.1, о тл и ч а ю ще ес я тем, что блок искажения сигнала содержит мультиплексор и группу узлов искажения, группа входов блока соединена с управляю цими входами мультиплексора, информационные входы которых соединены с выходами узлов искажения, входы пуска которых соединены с входом блока, Выход мультиплексора соединен с выходом блока.

1674133

1674133

Ж1Составитель H. Шиянов

Редактор М. Товтин Техред M,Ìopãeíòàë Корректор M. Максимиыинец

Заказ 2923 Тираж 391 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб„4/5

Производственно-издательский комбинат Патент", г, Ужгород, ул.Гагарина, jQ",