Устройство для ввода информации

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при создании систем сбора и обработки информации и вычислительных комплексов. Цель изобретения - повышение быстродействия. Поставленная цель достигается тем, что устройство для ввода информации содержит первую группу передатчиков 6, дешифратор 7, блок 8 управления, вторую группу передатчиков 9, приемники 10, буферный регистр 11 и блок 12 памяти . 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (s>)s G 06 F 13/14

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

s i. с °

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4622469/24 (22) 20.12,88 (46) 30.08.91, Бюл. М 32 (72) Г.В. Кухарь, В.И. Потапенко, Е.Б. Паламарчук, В.А. Алеев и Н.Н. Блистанов (53) 681.325(088,8) (56) Авторское свидетельство СССР

hL 1003063, кл. G 06 F 13/14, 1981.

Авторское свидетельство СССР

М 1005019, кл. G 06 F 13/14, 1981. (54) УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ

„„Я2„„ 1674142 А1 (57) Изобретение относится к вычислительной технике и может быть использовано при создании систем сбора и обработки информации и вычислительных комплексов. Цель изобретения — повышение быстродействия. Поставленная цель достигается тем, что устройство для ввода информации содержит первую группу передатчиков 6, дешифратор 7, блок 8 управления, вторую группу пеоедатчиков

9, приемники 10, буферный регистр 11 и блок 12 памяти. 2 ил.

1674142

Изобретение относится к вычислительной технике и может быть использовано при создании систем сбора и обработки информации и вычислительных комплексов.

Цель изобретения — повышение быстродействия.

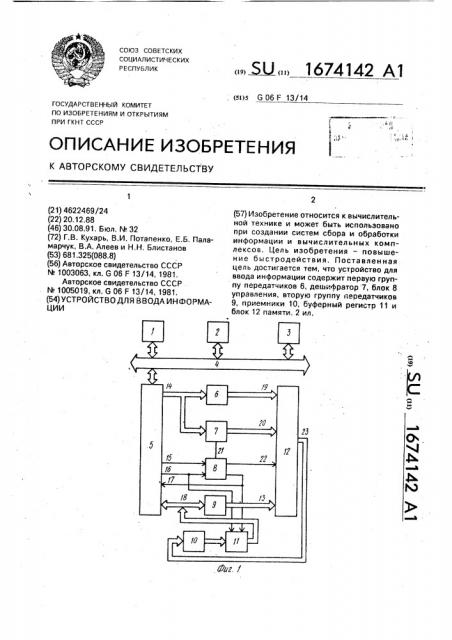

На фиг. 1 показана схема устройства для ввода информации в системе обработки данных; на фиг. 2 — схема устройства сопряжения, Система обработки данных содержит, процессор 1, оперативное запоминающее устройство 2 (ОЗУ), внешнее запоминающее устройство 3 (ВЗУ), канал 4 типа "Общая шина", устройство 5 сопряжения, первую группу передатчиков 6, дешифратор

7, блок 8 управления, вторую группу передатчиков 9, приемники 10, буферный регистр 11, блок 12 памяти, информационные входы 13 блока памяти, адресные входы 14 первой и второй групп устройства для ввода информации, входы 15 запуска, 16 режима, выход 17 признака ответа устройства для ввода информации, информационные входы-выходы 18 устройства для ввода информации, адресные входы 19, вход20 . записи/считывания блока памяти, вход 21 синхронизации дешифратора, вход 22 синхронизации и выходы 23 блока памяти. Устройство сопряжения содержит приемники 24, первый селектор 25 адреса, элемент НЕ 26, первый элемент И 27, второй селектор 28 адреса, первый и второй регистры 29 и 30, регистр 31 адреса, первый, второй и третий триггеры 32 — 34, регистр 35 данных, дешифратор 36, первый — третий элементы И вЂ” НЕ. 37-39, блок 40 постоянной памяти, второй элемент И 41. элемент 42 задержки, первую группу передатчиков 43, четвертый элемент И вЂ” НЕ 44, мультиплексор

45, пятый элемент И вЂ” Н Е 46, третий элемент

И 47, передатчик 48, шестой и седьмой элементы И вЂ” НЕ 49 и 50, вторую группу передатчиков 51, линию 52 сигнала ОТВ, линию

53 сигнала А1, лини1о 54 сигнала А2, линию

55 сигнала ОБМ, линию 56 сигнала BY, линии 57 и 58 адреса, линию 59 сигнала ДЗП, линию 60 сигнала ДЧТ, линию 61 сигнала

УСТ, линии 62 адреса, линию 63 сигнала

ВЫВ, 2, линию 64 сигнала ВЫВ.О, линию 65 сигнала ВЫВ.4, линию 66 сигнала ВВ.О, линию 67 сигнала BB.4, линию 68 сигнала

В В.4.

Устройство имеет основной и вспомогательный режимы работы, Основной режим при включении питания обеспечивает автоматический запуск и выполнение рабочей программы пользователя, хранящейся в блоке 12, Вспомогательный режим обеспечивает загрузку рабочей программы пользователя с соответствующего носителя информации (перфоленты, гибкого магнитного диска и

5 др.) в блок 12, Этот режим используется только при замене и корректировке рабочей программы пользователя. Запуск программы начальной загрузки производится оператором. Операция загрузки происходит

10 под управлением процессора 1 по программе начальной загрузки информации.

Программа начальной загрузки информации находится в блоке 40 постоянной памяти устройства сопряжения 5 и занимает в

15 адресном пространстве некоторую область.

B основном режиме при включении устройства источник питания формирует вторичные питающие напряжения и блокирует работу системы сигналами АИП и АСП.

20 При установке рабочих уровней вторичных напряжений сигналы АИПН, АСПН снимаются с канала 4, По снятии сигнала АСП процессор 1 переходит на выполнение микропрограммы, 25 которая загружает в счетчик команд стартовый адрес и, если в канале 4 не вырабатывается сигнал ОСТ, начинает выполнение программы перезаписи информации. Программа перезаписи информации занимает

30 некоторую область адресов блока 40 постоянной памяти устройства 5 сопряжения, При выполнении программа обеспечивает перезапись массива информации из блока

12 в ОЗУ 2; По окончании перезаписи ин35 формации программа передает управление на старторый адрес рабочей программы пользователя.

Выполнение основного и вспомогательного режима работы происходит под управ40 лением процессора 1. При этом процессор обращается к устройствам, подключенным к каналу 4 с помощью стандартных канальных циклов "Ввод" и "Вывод".

Процедура ."Ввод". При выполнении

45 данной процедуры процессор 1 устанавливает в канале 4 адрес, сигнал BY — признак обращения к области адресов (100000—

177776) и сигнал 06М, сопровождающий адрес.

50 В устройство 5 сопряжения адрес, сигнал BY и сигнал сопровождения поступают через приемники 24. Сигнал BY и разряды, например (9-12) адреса, поступают в селектор 28, Селектор адреса 28 вырабатывает

55 активный высокий уровень сигнала ПЗУ

ВЫБРАНО, Сигнал ПЗУ ВЫБРАНО совместно с разрядами, например 1 — 8 адреса, определяющими конкретную ячейку блока 40, поступают в регистр 30 и запоминаются в нем по переднему фронту сигнала ОБМ, 1674142

С выходов регистра 30 сигнал ПЗУ В bl- адреса вырабатывает активный уровень сигБРАНО и информация об адресе выбранной нала УС.ВЫБРАНО (высокий уровень), Сигячейки поступают соответственно на вход нал УС ВЫБРАНО совместно с разрядами элемента И вЂ” НЕ 39 и на адресные входы А1, А2 адреса поступают на входы регистра блока40. Наэтомадресный циклпроцедуры 5 29 и запоминаются в нем по переднему

"Ввод" заканчивается. Процессор1снимает фронту сигнала ОБМ. На этом адресный с канала 4 адрес и устанавливает сигнал цикл процедур "Ввод", "Вывод" эаканчиДЧТ, вается. Процессор 1 снимает с канала 4

Сигнал ДЧТ через один из приемников адрес и устанавливает в случае процедуры

24 поступает на вход элемента И вЂ” НЕ 39. В 10 "Ввод" сигнал ДЧТ, а в случае процедуры результате на выходе элемента И вЂ” НЕ 39 "Вывод" — данные, подлежащие записи в вырабатывается сигнал низкого уровня, ко- выбранный регистр, и сигнал сопровождеторый поступает на управляющий вход бло- ния ДЗП. ка 40, Информация о содержимом выбранной Сигнал ДЧТ или ДЗП совместно с разячейки блока 40 поступает на первую группу 15 рядами А1, А2 адреса и сигналом УС ВЫинформационных входов мультиплексора 45 БРАНО поступают на дешифратор 36, В и через элемент задержки 42 — на входы результате дешифратор вырабатывает акэлемента И вЂ” НЕ 50 и элемента И вЂ” НЕ 49. flo тинный уровень сигнала, непосредственно данному сигналу элементы И-НЕ 50 и 49 на осуществляющего операцию "Чтение" или выходахформируютсигналывысокогоуров- 20 "Запись" над выбранным регистром, а ня, которые поступают на адресные входы именно:сигнал ВЫВ,Оосуществляетзапись мультиплексора 45 и разрешают прохожде- нового содержимого в РГ.С, сигнал ВЫВ.2— ние информации о содержании выбранной запись нового содержимого в Рг.А, сигнал ячейки блока 40 на входы передатчиков 51. ВЫВ.4 — запись нового содержимого в реЭлементИ-НЕ46формируетнавыходесиг- 25 гистр Рг,Д, сигнал ВВ.Π— чтение содержинал высокого уровня, который поступает на мого регистра Pr.Ñ, сигнал ВВ2 — чтение управляющей входы передатчиков 51 и раз- содержимого регистра РгА, сигнал ВВ.4— решаетпрохождениеинформациис выхода чтение содержимого регистра Рг.Д., где мультиплексора45вканал4.ЭлементИ-НЕ Pr.À, Рг.Д и Рг.С вЂ” регистры, соответствен44 формирует на выходе сигнал высокого 30 но, адреса, данных и состояния. уровня, который через передатчик 48 посту- .. Кроме того, в устройстве 5 сопряжения пает в канал 4 (на линию ОТВ). Сигнал на вырабатывается сигнал ОТВ, который инлинии ОТВ сопровождает информацию о со- формирует процессор о завершении операдержимом выбранной ячейки блока 40 к ции "Чтение" или "Запись" над выбранным процессору 1. 35 регистром.

Процессор, получив сигнал ОТВ, прини- При выполнении процедуры "Ввод" сигмает информацию о содержимом выбран- нал 0ТВ формируется следующим образом. ной ячейки и заканчивает процедуру ВВОД, На один вход элемента И вЂ” НЕ 38 постуснимая с канала 4 сигналы ДЧТ и ОБМ, пает сигнал ДЧТ, на другом входе этого элеОперация "Чтение содержимого ячейки 40 мента И вЂ” НЕ к этому времени установлен

ЗУ пользователя" выполняется процессо- сигнал УС ВЫБРАНО, в результате на выхором при перезаписи информации из ячеек де элемента И вЂ” НЕ 38 формируется сигнал блока 12 в ячейки ОЗУ 2, низкого уровня, который через элементы И

Устройство 5 сопряжения имеет три про- 41 и И вЂ” НЕ 44 поступает на вход передатчика граммно-адресуемые регистра: регистрсосто- 45 48. С выхода передатчика 48 сигнал OTB яния РГС(группа триггеров 32, 33, 34), регистр поступает в канал 4, адреса (Рг.А) — буферный регистр 31, доступ- Аналогично формируется сигнал ОТВ ный процессору по чтению и записи, ре- при выполнении процедуры ВЫВОД. гистр 35 данных (Рг.Д) — буферный регистр, Для чтения содержимого одной ячейки доступный процессору по чтению и записи. 50 ЗУ пользователя процессор выполняет слеПри выполнении стандартных процедур дующие стандартные процедуры по отно"Ввод", "Вывод" по отношению к програм- шению к регистрам устройства сопряжения. мно-адресуемым регистрам устройства 5 Процедура "Вывод" записывает в Pr.À сопряжения процессор 1 устанавливает (31) адрес выбранной ячейки ЗУ. Процедура в канале 4 адрес выбранного регистра, сиг- 55 "Вывод" в Рг.С устанавливает разряд "Пуск" нал BY и сигнал сопровождения (ОБМ), В (триггер 32) в состояние "1", а разряд "Реустройство 5 сопряжения данные сигналы жим" (триггер 33) — в состояние "0". Процепоступают через приемники 24. дура "Ввод" "читает" Рг.С усгройства 5

Сигнал BY и разряды адреса 62 посту- сопряжения и анализирует его разряд "Го- пают на селектор 25 адреса. Селектор 25 товность" (триггер 34). Процедура "Ввод"

1674142

"читает" содержимое регистра данных Рг,Д (35) устройства 5 сопряжения, При выполнении первой процедуры дешифратор 36 формирует сигнал ВЫВ.2, Сигнал ВЫВ.2 низким уровнем поступает на стробирующий вход регистра 31 и по переднему фронту записывает в регистр адрес, поступающий на входы регистра адреса

31 через приемники 24 с канала 4.

С выходов регистра 31 адрес выбранной ячейки через входы 14 поступает на передатчики 6 (например, разряды

А1...А12) и дешифратор 7 (например, разря ды А13...A15), С вь ходов передатчиков 6 адрес поступает в блок 12. При выполнении второй процедуры (" Вывод" ) дешифратор 36 формируе сигнал В Ы В,О. Данный сигнал низким уровнем поступает на входы С триггеров 32, 33 и по переднему фронтуустанавливает их в состояние, определяемое информацией, поступающей на входы Dтриггеров 32 и 33 через приемники 24 с линии (например, АДО и АДЗ) канала 4;соответственно. Триггер 32 устанавливается в состояние "1", а триггер 33 — в состояние

"0". Сигнал, низкого уровня с инверсного выхода триггера 32 и сигнал высокого уровня с инверсного выхода триггера 33, соответственно, поступают на входы блока 8 управления.

Кроме того, сигнал высокого урвня с инверсного выхода триггера 33 (разряд "Режим") поступает на управляющие входы передатчиков 43 и регистра 11. Передатчики

43 переводятся в состояние высокого импеданса, а иэ регистра 11 производится считывание.

Сигнал с третьего выхода блока 8 управления поступает на дешифратор 7 и разрешает дешифрацию кода, установленного на его информационных входах (например, разряды А1З...А15). Сигнал с первого выхода блока 8 управления поступает в блок 12, в результате чего происходит операция

"Чтение" ячейки блока 1 . памяти. С выходов блока 12 содержимое выбранной ячейки через приемники 10 поступает на регистр 11.

При этом, так как на входе 16 установлен сигнал низкого уровня, то информация из регистра 11 проходит на вход-выход 18, Передача информации сопровождается сигналом, формируемым блоком 8 управления на втором выходе. Информация и сигнал сопровождения поступают на устройство сопряжения 5 по следующим цепям; информация о содержимом выбранной ячейки поступает на третью группу информационных входов мультиплексора 45„и сигнал сопровождения (078) на вход S триггера 34, уста- навливая разряд "Готовность" Рг.С и через

50 элемент И 27 — на вход R триггера 32, сбрасывая разряд "Пуск" Рг, С, Информация о состоянии разрядов Рг.С поступает на информационные входы мультиплексора 45, Мультиплексор 45 пропускает данную информацию на входы передатчиков 51.

Процедура "Ввод" вь полняется процессором 1 по отношени.о к Pr.Ñ. При этом процессор анализирует состояние разряда

Pr,Ñ "Готовность" (триггер 34). При выполнении процедуры "Ввод" на выходе дешифратора 36 формируется сигнал ВВ,О, который поступает затем на первый вход элемента И вЂ” НЕ 46.

Элемент И вЂ” Н Е 46 формирует сигнал высокого уровня, который поступает на управляющие входы передатчиков 51 и разрешает передачу в канал 4 информации о содержимом регистра состояний (Рг.C).

Процедура "Ввод" позволяет процессору 1 считать содержимое выбранной ячейки.

Данная процедура выполняется только при условии установки разряда Рг,С "Готовность" в состояние, соответствующее "1".

При выполнении процедуры дешифратор 36 формирует сигнал ВВ.4. Сигнал ВВ,4 низким уровнем поступает на третий вход элемента И-НЕ 46, на второй вход элемента

И вЂ” НЕ 49 и на второй вход элемента И 47.

Элемент И вЂ” НЕ 49 формирует сигнал высокого уровня, который поступает на первый адресный вход мультиплексора

45, В результате мультиплексор 45 пропускает информацию о содержимом выбранной ячейки на передатчики 51, Элемент

И-НЕ 46 формирует сигнал высокого уровня, который поступает на управляющие входы передатчиков 51 и разрешает прохождение информации о содержимом выбранной ячейки в канал 4, Элемент И 47 формирует сигнал низкого уровня, который поступает на вход С триггера 34 и по заднему фронту устанавливает данный триггер в состояние "0", Операция "Запись нового содержимого" в ячейки ЗУ пользователя выполняется процессором 1 при начальной загрузке пользователя. При этом для записи нового содержимого в одну из ячеек ЗУ процессор

1 выполняет следующие стандартные процедуры по отношению к программно-адресуемым регистрам устройства 5 сопряжения.

Процедура "Вывод" устанавливает в

Рг.А (31) ацрес выбранной ячейки ЗУ, Процедура "Вывод" устанавливает в Pr.Ä (35) данные, подлежащие записи в выбранную ячейку ЗУ. Процедура "Вывод" устанавливает в Рг.С разряды "Режим" (триггер ЗЗ) и

1674142

5

40

"Пуск" (триггер 32). Процедура "Ввод" анализирует состояние разряда "Готовность" (триггер 34) Рг.С, При выполнении первой процедуры дешифратор 36 устройства 5 сопряжения формирует сигнал ВЫВ.2, Сигнал ВЫ В.2 низким уровнем поступает на стробирующий вход регистра 31 и по переднему фронту записывает в регистр адрес выбранной ячейки, поступающий на входы регистра 31 адреса через приемники

24 с канала 4.

С выходов регистра 31 адреса адрес выбранной ячейки через входы 14 поступает на группу передатчиков 6 (например, разряды А1...А12) и дешифратор 7 (например, разряды А13...A15). С выходов передатчиков адрес поступает в блок 12.

При выполнении второй процедуры (" Вывод" ) дешифратор 36 устройства 5 сопряжения формирует сигнал ВЫВ.4. Данный сигнал низким уровнем поступает на стробирующий вход С регистра 35 данных и по переднему фронту записывает данные, поступающие на входы регистра через приемники 24 с канала 4. При выполнении третьей процедуры (" Вывод" ) дешифратор

36 устройства 5 сопряжения формирует сигнал ВЫВ,О. Данный сигнал низким уровнем поступает на стробирующие входы регистра состояния, Сигнал ВЫВ,О поступает на входы С триггеров 32, 33 и по переднему фронту записывает в них информацию, поступающую на их входы Д через приемники 24 с лийий АД (О) и АД (3) канала 4, соответственно.

При выполнении операции "Запись" ноаого содержимого в ячейку ЗУ разряды регистра состояния "Режим" триггер (33) и

"Пуск" (триггер 32) устанавливаются в состояние "1". Сигналы низкого уровня с инверсных выходов триггеров 32, 33, соответственно; поступают на входы устройства 8 управления, Кроме того, сигнал с инверсного выхода триггера 33 (разряд "Режим" ) поступает на управляющие входы передатчиков 43 и регистра 11. Данный сигнал разрешает прохождение информации с выходов передатчиков 43 на вход-выход 18, а выходы регистра 11 переводит в состояние высокого импеданса. Информация с выходов передатчиков 43 поступает на передатчики 9.

Сигнал с третьего выхода блока управления, поступая на вход V дешифратора 7, разрешает дешифрацию кода адреса (например, разряды А13 — А15), Сигнал с первого выхода блока 8 формируется позже, чем сигнал на третьем выходе, и поступает на блок 12. В результате происходит запись нового содержимого в ячейку, определяемую кодом адреса, установленного на входах А. По окончании процесса записи блока

8 управления на втором выходе формирует сигнал "ОТВ.ЗУ", который поступает на устройство 5 сопряжения, В устройство сопряжения сигнал ОТВ ЗУ поступает на вход S триггера 34 и через элемент И 27 — на вход К триггера 32, Происходит сброс разряда

"Пуск" и установка разряда "Готовность", При выполнении четвертой процедуры (" Ввод" ) дешифратор 36 формирует сигнал

ВВ.О, который поступает на первый вход элемента И вЂ” НЕ 46 и далее с выхода его сигналом высокого уровня на управляющие входы передатчиков . 51, разрешая прохождение информации о содержимом Рг.С в канал 4, Информация о содержимом Pr.Ñ (триггеры 32 — 34) поступает на входы передатчиков 51 через мультиплексор 45.

Формула изобретения

УстрОйствО Для Ввода информации, содержащее дешифратор, буферный регистр, блок управления и блок памяти, причем выход дешифратора подключен к входу записи-считывания блока памяти, первый и второй выходы блока управления подключены соответственно к входам синхронизации блока памяти и буферного регистра, о т л и ч а ю щ е е с я тем, что, с целью увеличения быстродействия, устройство содержит приемники, первую и вторую группу передатчиков, причем адресные входы первой и второй групп устройства подключены соответственно к информационным входам передатчиков первой группы и дешифратора, выходы передатчиков первой группы подключены к адресным входам блока памяти, выходы которого подключены соответственно к информационным входам приемников, выходы которых подключенысоответственно к информационным входам буферного регистра, выходы которого подключены соответственно к информационным входам-выходам устройства и соответственно к информационным входам передатчиков второй группы, выходы которых подключены соответственно к информационным входам блока памяти, второй выход блока управления подключен к выходу признака ответа устройства, вход запуска которого подключен к входу запуска блока управления, третий выход которого подключен к входу синхронизации дешифратора, вход режима устройства подключен к входу режима блока управления и к входу записисчитывания буферного регистра, 1674142

Составитель В. Смирнов

Техред M.Mîðãåíòàë Корректор Э, Лончакова

Редактор О, Спесивых

Производственно-издательский комбинат "Патент", г, Ужгород, ул.Гагарина, 101

Заказ 2924 Тираж 383 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, )К-35, Раушская наб., 4/5