Аналоговое вычислительное устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах. Целью изобретения является расширение функциональных возможностей за счет реализации операции суммирования и повышение точности. Аналоговое вычислительное устройство содержит с первого по N-ый перемножающие блоки 1.1, ... 1.N, первый источник 2 опорного напряжения, сумматор 3, второй источник 4 опорного напряжения, выход 5, входы 6.1 - 6.N с первого по N-й сигналов-сомножителей. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)5 G 06 G 7/12

ГОСУДАРСТВЕ! 1НЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И OTKF- ЫТИЯМ

ПРИ ГКНТ СССР

rю у

E ° / (ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4636459/24 (22) 12,01.89 (46) 30,08.91. Бюл. ¹ 32 (72) А.А.Киселев и В.М.Назаренко (53) 681.335(088.8) (56) Авторское свидетельство СССР

¹ 1146688, кл, G 06 G 7/16, 1985.

Авторское свидетельство СССР

N 1497625, кл. G 06 G 7/16, 1987. (54) АНАЛОГОВОЕ ВЫЧИСЛИТЕЛЬНОЕ

УСТРОЙСТВО (57) Изобретение относится к электрическим вычислительным устройствам и может

Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах.

Цель изобретения — оасширение функциональных возможностей за счет реализации операции суммирования и повышение точности.

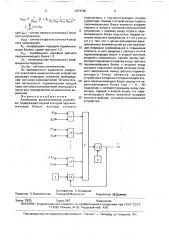

На чертеже изображена структурная схема аналогового вычислительного устройства, Устройство содержит с первого по N-й перемножающие блоки 1.1 — 1,N, первый источник 2 опорного напряжения, сумматор 3, второй источник 4 опорного напряжения, выход 5, входы с первого по N-й сигналовсомножителей 6.1-6.N.

Аналоговое вычислительное устройство работает следующим образом.

Все перемножающие блоки, кроме третьего 1.3, имеют одинаковое схемное решение. Третий перемножающий блок 1.3. Ы 1674162 А1 быть использовано в аналоговых вычислительных машинах. Целью изобретения является расширение функциональных возможностей за счет реализации операции суммирования и повышение точности. Аналоговое вычислительное устройство содержит с первого по N-й перемножающие блоки

1.1.„1.N, первый источник 2 опорного напряжения, сумматор 3, второй источник 4 опорного напряжения, выход 5, входы 6.1—

6.N с первого по N-й сигналов-сомножителей. 1 ил. должен быть прямого действия. Сигналы-сомножители с входов 6,1 — 6,N поступают на соответствующие входы перемножающих блоков 1.1 — 1.N. Выходные сигналы перемножающих блоков поступают на входы сумматора 3: Кроме того, на соответствующий вход сумматора 3 с выхода второго перемножающего блока 1.2 поступает сигнал, равный произведению сигнала с выхода 5 и сигнала первого источника 2 опорного напряжения. Этот сигнал поступает на вход сумматора 3 с отрицательным знаком. Выходной сигнал сумматора 3 с помощью третьего перемножающего блока 1.3 перемножается с сигналом второго источника 4 спорного напряжения.

При выполнении условия идентичности параметров перемножающих блоков, кроме третьего перемножающего блока 1.3, величина результирующего сигнала на выходе 5 описывается выражением

1674162

Составитель G.Отраднов

Редактор Л,Веселовская Техред М.Моргентал Корректор M.Äåì÷èê

Заказ 2925 Тираж 367 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, )К-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

1 1

0вых = — 1 + о х

Омк1 1 Ко Омк1 Кпз Омк21 х 01j 02), j =1 где 0«1 — сигнал первого источника 2 опорного напряжения;

Омк2 — сигнал второго источника 4 опорного напряжения;

Ко — коэффициент передачи перемножающих блоков, кроме третьего 1.3;

Кп — коэффициент передачи третьего перемножающего блока l,3; до — относительная погрешность коэффициента передачи;

0 1j, U2j — сигналы-сом ножител и, Из приведенного выражения следует, что аналоговое вычислительное устройство реализует операцию сложения произведений сигналов-сомножителей. Относительная погрешность перемножения каждой пары сигналов-сомножителей уменьшена в число раз, определяемое знаменателем выражения, Формула изобретения

Аналоговое вычислительное устройство, содержащее первый и второй перемножающие блоки, выходы которых подключены к соответствующим входам сумматора, первый и второй входы первого перемножающего блока являются входами первого и второго сигналов-сомножителей

5 устройства, к первому входу второго перемножающего блока подключен первый источник опорного напряжения, о т л и ч а ю ще е с я тем, что, с целью расширения функциональных возможностей за счет реализа10 ции операции суммирования и повышения точности, в него введены с третьего по N-й перемножающие блоки и второй источник опорного напряжения, причем выход сумматора подключен к первому входу третьего

15 перемножающего блока, к второму входу которого подключен второй источник опорного напряжения, выход третьего перемножающего блока является выходом устройства и соединен с вторым входом вто20 рого перемножающего блока, выход i-ro перемножающего блока (где i = 4,...,N) подключен к соответствующему входу сумматора, первый и второй входы i-ro перемножающего блока являются входами

25 соответствующих сигналов-сомножителей устройства.