Нелинейный преобразователь

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано для линеаризации характеристик датчиков и выполнения различных математических операций. Цель изобретения - повышение точности при вычислении полиномиальных зависимостей. Получение полиномиальных зависимостей осуществляется на основе циклического повторения процесса двухтактного интегрирования, при этом число циклов определяется степенью полинома. В первом такте первого цикла интегрируют входной сигнал в течение периода помехи, во втором такте всех циклов интегрируют образцовый сигнал до момента равенства нулю текущей суммы интегралов первого и второго тактов данного цикла. Длительность второго такта первого цикла кодируют и преобразуют в аналоговую величину, которую далее интегрируют в первом такте всех последующих циклов вместо входного сигнала, причем длительность первого такта последующего цикла равна длительности второго такта предыдущего цикла. Нелинейный преобразователь содержит компаратор 2 знака, ключи 3, 11, 16, интегратор 4, нуль - орган 5, блок 6 управления, реверсивный счетчик 8, генератор 9 тактовых импульсов, элемент И 10, цифроаналоговые преобразователи 13 и 18, источник 14 опорного напряжения, регистр 17 памяти. 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4622107/24 (22) 19.12.88 (46) 30.08.91, Бюл, hh 32 (72) А.Б.Андреев, Вик,А.Баранов, Вл.А.Баранов и Н.А.Ермолаев (53) 681.3(088.8) (56) Авторское свидетельство СССР

М 1012279, кл. 6 06 G 7/26, 1981.

Шляндин В,M. Цифровые измерительные устройства. M. Высшая школа, 1981, . c,202-203. (54) НЕЛИНЕЙНЫЙ ПРЕОБРАЗОВАТЕЛЬ (57) Изобретение относится к автоматике и вычислительной технике и может быть использовано для линеарилизации характеристик датчиков и выполнения различных математических операций. Цель изобретения — повышение точности при вычислении полиномиальных зависимостей, Получение полиномиальных зависимостей осуществляется на основе циклического повторения процесса двухтактного интегрирования, Изобретение относится к автоматике и вычислительной технике и может быть использовано для линеаризации характеристик датчиков и выполнения различных математических операций.

Цель изобретения — повышение точности при вычислении полиноминальных зависимостей.

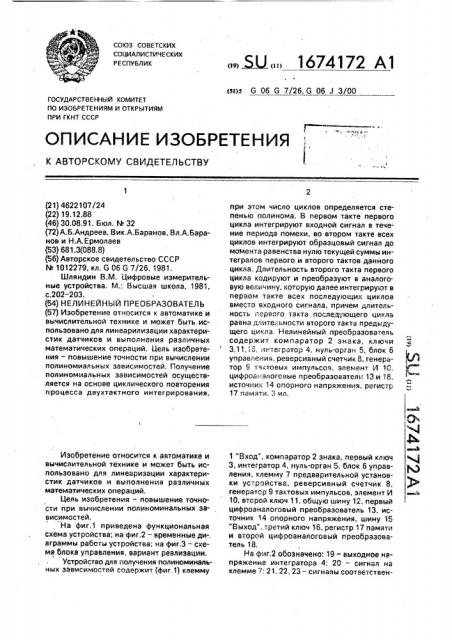

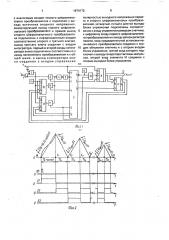

На фиг.1 приведена функциональная схема устройства; на фиг,2 — временные ди-, аграммы работы устройства; на фиг.3 — схема блока управления, вариант реализации.

Устройство для получения полиноминальных зависимостей содержит (фиг.1) клемму, Ы„„1674172 А1 (я)5 G 06 6 7/26, G 06 J 3/00 при этом число циклов определяется степенью полинома. В первом такте первого цикла интегрируют входной сигнал в течеwe периода помехи, во втором такте всех циклов интегрируют образцовый сигнал до момента равенства нулю текущей суммы интегралов первого и второго тактов данного цикла, Длительность второго такта первого цикла кодируют и преобразуют в аналоговую величину, которую далее интегрируют в первом такте всех последующих циклов вместо входного сигнала, причем длительность первого такта последующего цикла равна длительности второго такта предыдущего цикла, Нелинейный преобразователь содержит компаратор 2 знака, ключи

3,11,16, интегратор 4, нуль-орган 5, блок 6 управления, реверсивный счетчик 8, генератор 9 тактовых импульсов, элемент И 10. цифроаналоговые преобразователи 13 и 18, источник 14 опорного напряжения, регистр

17 памяти. 3 ил, 1 "Вход", компаратор 2 знака, первый ключ

3, интегратор 4. нуль-орган 5, блок 6 управления, клемму 7 предварительной установки устройства, реверсивный счетчик 8, генератор 9 тактовых импульсов, элемент И

10, второй ключ 11, общую шину 12, первый цифроаналоговый преобразователь 13, источник 14 опорного напряжения, шину 15

"Выход", третий ключ 16, регистр 17 памяти и второй цифроаналоговый преобразователь 18.

На фиг,2 обозначено; 19 — выходное напряжение интегратора 4; 20 — сигнал на клемме 7; 21, 22, 23 — сигналы соответствен1674172 но на первом, втором и третьем выходах блока 6 управления, Блок 6 управления (фиг,3) может быть выполнен на основе первого, второго и третьего D-триггеров 24-26, RS-триггера 27, счетчика 28, реверсивного счетчика 29 тактов, счетчика 30 циклов, блока 31 памяти, первого и второго элементов ИЛИ 32 и 33, первого — четвертого элементов И 34 — 37.

Устройство работает следующим образом.

Предварительна в блок 31 памяти записываются nm-разрядньо: слов,, где n — степень полинома, fn — разрядность выходного

4(ода. ЕМКОСТЬ Ко СЧЕТЧИКа 28 ВЫбИраЕТСЯ

4 о таКОй, ЧтабЫ ОТ4-4ОЦ4Е44ИЕ. "Го= — (4о — ЧаСтОо та импульсов с генератора 9 импульсов) было бы кратно г4ериоду помехи на входе устройства. Емкость и реверсивного счетчика 29 тактов выбирается равной максимальному значению выходного кода первого цикла. Емкость йя счетчика 30 циклов выбирается равной степени полинома

A.

В исходном состОянии (фиг,1 и 2) ключи

3, 11 и 16 разомкнуты, выходное напряжение интегратора 4 равно нулю, прохождение счетных импульсов на реверсивный счетчик 8 запрещено сигналом с второго выхода блока 6 управления. Компаратор 2 знака управляе4 знаком вь4ходного на и рЯжения первого 1 3 и втОрого 1 8 цифроаналоговых преобразователей. Для определенности примем, что интегратор 4 является неинвэртирующим, следовательно, э49пО1з = — sign О 4э == — signU>x„ где О4з и О1в — выходные напряжения первого 13 и второго 18 ц44фроаналоговь4х преобразователей.

Пусть в момент времени 1о (фиг,2) подается импульс на клемму 7, по которому устанавливаются в ноль все счетчики 8, 28, 29 и

30, RS-триггер 27 и второй 4..-триггер 25, а первый и третий 4..4-триггеры 24 и 26 — в единицу. Вследствие зт зго замыкается первый ключ 3 и нс4чи44с4етсй заполнение счет" чика 28 импульсами с выхода генератора 9 импульсов. В результате интегратор 4 интегрирует входной сигнал Ux с налаженной на него помехой U!sin и t, В момент времени t> счетчик 28 пег4еполняется и сигналОМ:" ереполнения устанавливает первый D-триггер 24 в ноль, а второй D-триггер 25 в единицу. Вследствие этого первый ключ 3 размыкается, а второй ключ 11 замыкается, Одновремен44о разрешается прохо>кде44ие импульсов на реверсивный 4 четчик 8 и 4е4 4ррсивный 4qeqpq4444 29

О1э(4) = О, а, U«

Оо1

5

30 тактов. Направление счета импульсов реверсивного счетчика 8 зависит от записанной в блоке 31 памяти информации для первого цикла, которая считывается по адресу, определяемому состоянием счетчика

30 циклов, Первый счетный импульс в последний поступил в момент времени tt, Во втором такте первого цикла оевеосивный счетчик. 29 тактов работает на сложение, что определяется единицей на выходе третьего О-триггера 26. В результате интегратор 4 интегрирует выходное напряжение первого цифроаналогового преобразователя 13, величина которого зависит от записанной в блоке 31 памяти информации для первого цикла, В момент времени tz (фиг.2) выходное напряжение интегратора 4 достигает нуля, что вызывает срабатывание нуль-Органа 5, Сигналом последнего RS-триггер 27 устанавливается в единицу, фиксируя содержимое реверсивного счетчика 8 в регистре 17 памяти, а третий D-триггер 26 устанавливается в ноль, Сигналом последнеего запрещается счет импульсов реверсивным счетчиком 8, реверсивный счетчик 29 тактов включается на вычитание, второй ключ 11 размыкается, а третий ключ 16 замыкается.

На этом в момент времени tz заканчивается первый цикл работы устройства.

В результате перечисленных поцессов в реверсивном счетчике 8 и регистре 17 памяти будет зафиксирован код

Uxt Uxt «= . о 4о =а1 ..— °

ОО4 Uo> где U« — среднее значение входного сигнала на интервале Т„;

Оо4 — выходной сигнал цифроаналогового преобразователя 13 в первом цикле;

Э1= то1 =COnSt — ПОСтОЯННЫй КОЗффИЦИент первого цикла, С момента времени tz (фиг,2) идет первый такт второго цикла преобразования, в течение которого интегратор через замкнутый третий ключ 16 интегрирует выходное напряжение второго цифроаналогового преобразователя 18, которое будет равно где Оо — выходной сигнал источника 14 опорного нат4ряжения, В момент времени тэ (фиг.2) работающий на вычитание реверсивный счетчик 29 тактов обнуляется и импульсом переноса переключает третий D-триггер 26 в единицу, 1674172 в(Й то Гхг =то

Их1 О г

U01 U02 001 Тх1—

„г

t.) = аг

Uox

k=1

Где Тх1 и Тхг — Длительность втоРого такта соответственно первого и второго цикла; а2= (Tofî) ПОСТОЯННЫЙ КозффИЦИUo 2

001 ент второго цикла, 40

ТогДа сУммаРный коД Nx2 в РевеРсивном счетчике 8 за два цикла

Nx2=a;

Далее повторяются изложенные выше процессы за второй цикл (интервал времени 50

t4 — t2) для третьего и последующих циклов с учетом того, что длительность первого такта каждого последующего цикла берется равной длительности второго такта предыдущего цикла. Это обеспечивается попе- 55 ременной работой на сложсние-вычитание реверсивного счетчика 29 тактов.

По Окончании всех и циклов (момент времени 12П, фиг.2) на выходе переноса счетчика 30 циклов возникает импульс, который

Вследствие этого реверсивный счетчик 29 тактов переключается на сложение, начиная отсчет второго такта второго цикла, третий ключ 16 размыкается, а второй ключ 11 замыкается, Одновременно счетчик 30 цик- 5 лов сосчитывает второй импульс, вследствие чего на блок 31 памяти поступает код адреса второго цикла для направления счета. импульсов реверсивного счетчика 8 и определения кодового слова первого 10 преобразователя 13 для задания размера образцового напряжения Um во втором такте второго цикла. В результате интегратор 4 интегрирует напряжение Um, поступающее 15 на его вход через второй замкнутый ключ 11 с выхода первого преобразователя 13, В момент времени t4 (фиг,2) выходное напряжение интегратора 4 становится равным нулю, что приводит к срабатыванию 20 нуль-органа 5 и повторению описанных выше процессов для момента времени t2, На этом заканчивается второй цикл работ устройства, В результате перечисленных процессов 25 в реверсивный счетчик 8 поступает число импульсов, равное устанавливает второй D-триггер 25 в ноль. запрещая тем самым прохождение счетных импульсов в реверсивный счетчик 29 тактов и замыкание ключей 11 и 16, В результате в реверсивном счетчике 8 будет зафиксирован код

Ux1

Nx = ! =1 оак

k =1

Код в реверсивном счетчике 8 по окончании и циклов пропорционален значению полинома и-й степени от среднего значения

141 входного сигнала эа фиксированный интервал времени То, т,е. в данном случае отсутствует методическая погрешность получения полиномиальной зависимости, поскольку во всех тактах первого цикла в качестве входного сигнала фиксируется одна и та же величина Ux1 независимо от текущего изменения входного сигнала в течение п циклов преобразования.

Кроме того, поскольку начиная со второго цикла в качестве входной величины используется 01в(1), которая очищена от влияния аддитивной периодической помехи в первом цикле, то результат преобразования (1) также не будет зависеть от действия этой помехи.

Формула изобретения

Нелинейный преобразователь, содержащий источник опорного напряжения, первый. второй и третий ключи, причем информационный вход первого ключа соединен с входом нелинейного преобразователи, а выход первого ключа через последовательно соединенные интегратор и нуль-орган подключен к первому входу блока управления, первый, второй и третий выходы которого соединены с управляющими входами соответственно первого, второго и третьего ключей, выход генератора тактовых импульсов подключен к первому входу элемента И, выход которого соединен со счетным входом счетчика, выход которого является выходом нелинейного преобразователя, выходы первого и второго ключей обьед нены, О т л и ч а Ю щ и Й с я тем, что, с целью повышения точности при вычислении полинал.лальных зависимостей, в него введены кОмпаратор знака, первый и второй цифроаналоговые преобразователи и регистр памяти, а счетчик выполнен реверсивным, причем во ход счетчика подключен к инфор;Оц.1онному входу регистра памяти, выход котОрога соединен с цифровым входом ьтсрог0 цнфрсаналогового преобразователя, знл Ого=-ый вход которогО соединен

167 И72

Зхо

gxod

19

2 о -CeirS с аналоговым входом первого цифроаналогового преобразователя и подключен к выходу источника опорного напряжения, инвертирующий выход первого цифроаналогового преобразователя и прямой выход второго цифроаналогового г|реобразователя подключены к информационным входам соответственно второго и третьего ключей, выход третьего ключа соединен с входом интегратора, первый и второй входы компаратора знака подключены соответственно к входу нелинейного преобразователя и к общей шине, а выход компаратора знака соединен с входом управления

7 полярностью выходного напряжения первого и второго цифроаналоговых преобразователей, четвертый, пятый и шестой выходы блока управления подключены соответст5 венно к входу управления реверсом счетчика, к цифровому входу первого цифроаналогового преобразователя и к входу записи регистра памяти, вход предварительной установки нелинейного преобразователя соединен с вхо1О дом обнуления счетчика и с вторым входом блока управления, третий вход которого подключен к выходу генератора тактовых импульсов, второй вход элемента И соединен с вторым выходом блока управления.

1Г

1574172 1 3

Составитель В.Алекперов

Редактор Л.Веселовская Техред M.Ìîðråíòàë Корректор М;Демчик

Заказ 2925 Тираж 371 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101