Устройство для распознавания сигналов объектов

Иллюстрации

Показать всеРеферат

Изобретение относится к области автоматики, в частности к устройствам для распознавания сигналов объектов, и может быть использовано при построении распознающих автоматов. Цель изобретения состоит в повышении надежности распознавания составных фазоманипулированных сигналов. Поставленная цель достигается путем введения второго квадратора, фильтра нижних частот, делителя напряжения, ключа, второго интегратора, второго элемента задержки, четвертого компаратора, группы делителей напряжения, второго инвертора, пятого компаратора, второго элемента И, регистра сдвига, элемента ИЛИ, третьего инвертора, третьего элемента И, одновибратора, четвертого инвертора и второго формирователя планирующих импульсов. 1 ил.

союз советских

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

<я)з G 06 К 9/О

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

1

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4659565/24 (22) 06.03.89 (46) 30.08,91. Бюл. М 32 (71) Таганрогский радиотехнический институт им. В.Д.Калмыкова (72) А.П.Дятлов, А.В.Троц, Е.И.Коваленко и

А.М.Макаров (53) 681.327.12 (088.8) (56) Авторское свидетельство СССР

1Ф 481054, кл. G 06 К 9/00, 1975.

Авторское свидетельство СССР

М 1113760, кл, G 01 S 7/36. 1984. (54) УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ

СИГНАЛОВ ОБЬЕКТОВ (57) Изобретение относится к автоматике, в частности к устройствам для распознавания

Изобретение относится к автоматике, в частности к устройству для распознавания сигналов объектов, и может быть использовано при построении распознающих автоматов.

Цель изобретения — повышение надежности распознавания составных фазоманипулированных сигналов.

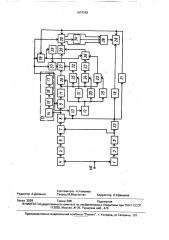

На чертеже представлена блок-схема устройства.

Устройство включает первый 1 и второй

2 квадраторы, первый 3 и второй 4 узкополосные фильтры, амплитудный детектор 5, фильтр 6 нижних частот, делитель 7 напряжения, ключ 8, первый 9 и второй 10 интеграторы, первый 11 и второй 12 элементы задержки, первый формирователь 13 тактирующих импульсов, включающий блок 14 формирования положительных импульсов, дифференцирующий блок 15, блок 16 определения модуля и одновибратор 17, одно„„5U „„1674183 А1 сигналов объектов, и может быть использовано при построении распознающих автоматов. Цель изобретения — повышение надежности распознавания составных фазоманипулированных сигналов. Поставленная цель достигается путем введения второго квадраторэ, фильтра нижних частот, делителя напряжения, ключа, второго интегратора, второго элемента задержки, четвертого компаратора, группы делителей напряжения, второго инвертора, пятого компэрэтора, второго элемента И, регистра сдвига, элемента ИЛИ, третьего инвертора, третьего элемента И, одновибратора, четвертого инверторэ и второго формирователя планирующих импульсов. 1 ил. вибратор 18, счетчик 19, регистр 20 сдвига, второй формирователь 21 тактирующих импульсов, выполненный в виде времязадающего блока, первый22, второй 23, третий 24, четвертый 25 и пятый 26 компараторы, первый 27 и второй 28 триггеры, группу делителей 29 — 31 напряжения, первый 32, второй

33, третий 34 и четвертый 35 инверторы, первый 36, второй 37 и третий 38 элементы

И, элемент 39 ИЛИ, На чертеже показан также вход 40 устройства.

Устройство работает следующим образом.

Входной сигнал с входа 40 поступает на входы фильтра 4 и квадратора 1.

С выхода фильтра 4 сигнал через квадратор 2 и фильтр 6 нижних частот поступает на один вход делителя 7, на другой вход которого поступает сигнал с выхода амплитудного детектора 5. С выхода делителя 7 выходное напряжение через ключ 8 посту1674183

20

50 пает как на вход интегратора 9, так и на вход блока 14.

В исходном состоянии (при отсутствии сигнала на входе устройства) напряжение на выходе компаратора 22 соответствует лог. "О", ключ 8 разомкнут, напряжения на первом входе и выходе интегратора 9 равны нулю, Напряжение на первом входе интегратора 10 больше нуля.

В момент поступления сигнала на вход устройства срабатывает компаратор 22 (пороговое напряжение компаратора определяется заданной вероятностью его ложных срабатываний), при этом на первый вход интегратора 10 и второй вход ключа 8 подается напряжение лог, "1". Ключ 8 замыкается и подключает выход делителя 7 к первому входу интегратора 9, а также к входу формирователя 13, состоящего из блока 14 формирования положительных импульсов, дифференцирующего блока 15, блока 16 определения модуля и одновибратора 17 и формирующего тактовые импульсы в моменты начала и окончания каждой компоненты входного сигнала.

Тактовые импульсы используются для сброса первого 9 и второго 10 интеграторов, а также управляют работой первого триггера 27 и регистра 20 сдвига. Длительность тактовых импульсов равна времени задержки первого 11 и второго 12 элементов задержки и много меньше минимально возможной длительности гармонической или манипулированной по фазе меандром компоненты.

Напряжение с выхода интегратора 9 через элемент 11 задержки подается на первый вход компаратора 26, а также на первые входы компараторов 23 — 25, Напряжение с выхода интегратора 10 через элементы 12 задержки подается на второй вход компаратора 26, а также на входыд, елителей 21 — 31 напряжения.

Комп араторы 23 — 25 срабаты вают (формируют на выходе уровень лог. "1") только в том случае, когда напряжение на их первых входах превышает напряжение на вторых входах, Компаратор 26 формирует на выходе уровень лог. "1" при приближенном равенстве (например, с погрешностью 10%) напряжений на первом и втором входах, В момент прихода первого тактового импульса напряжение на выходе элемента

11 задержки равно нулю, напряжение на выходе элемента 12 задержки равно соответствующей величине. При этом напряжения на выходах в горого, третьего, четвертого компараторов 23, 24 и 25 и на выходе компаратора 16 соответствует лог, "0". Выход компаратора 15 соединен с вторым входом триггера 27 через последовательно включенный первый инвертор 32, на первом входе первого триггера 27 имеется лог. "О", на втором входе этого же триггера — лог. "1". По окончании первого тактового импульса на выходе первого триггера 27 устанавливается лог, "О".

Таким образом, в моментприхода второготактового импульса напряжение на выходах второго — четвертого компараторов 23 — 26 соответствует лог. "1", на первом входе триггера 27 — лог. "1", на.втором — лог. "0".

На выходе триггера 27 устанавливается лог.

"1", которая переписывается в регистр 20 сдвига.

По окончании компоненты, манипулированной по фазе меандром, напряжение на первых входах второго, третьего, четвертого и пятого компараторов 23, 24, 25 и 26 близко к нулю, на их выходах имеется лог

"О", В момент прихода третьего тактового импульса напряжение nor. "0" переписывается на выход триггера 27 и Заносится в регистр 20 сдвига.

Счетчик 19 импульсов по переднему фронту четвертого тактового импульса формирует сигнал лог. "1", который поступает на третий вход элемента И 36, Одновременно с выхода инвертора 35 на второй вход элемента И 37 подается сигнал лог. "0", так что четвертый тактовый импульс не поступает на тактовый вход триггера 27, В момент прихода четвертого тактового импульса напряжение лог, "1" с выхода элемента И 36 записывается в третью ячейку регистра 20 сдвига. Появление на выходах регистра 20 сдвига логической комбинации

101 приводит к появлению лог. "1" на выходе элемента И 38. В момент окончания сигнала одновибратор 18 по отрицательному перепаду напряжения на выходе компаратора 22 формирует тактовый импульс, при поступлении которого на третий вход триггера 28 информация с первого входа триггера 28 переписывается на его выход.

Решение о наличии сложного составного сигнала принимается только в том случае, когда компоненты сигнала поступают на вход устройства в последовательности: гармоническая, манипулированная по фазе меандром, информационная, что обеспечивается счетчиком 19 импульсов, инвертором 35, элементами И 36 и 37. Счетчик 19 импульсов формирует напряжение лог. "1" по переднему фронту четвертого импульса, поступившего Hà его вход

Таким образом, считывание информации о состоянии компараторов 23 и 24 осуществляется только в момент прихода последнего (четвертого) тактового импуль1674183 са. Считывание информации о состоянии компараторов 25 и 2б осуществляется в моменты прихода первых трех тактовых импульсов.

Формирователь 21 тактовых импульсов ограничивает время анализа входного процесса после срабатывания компаратора 22 максимально возможной длительностью входного сигнала. Этот блок в течение заданного времени с момента срабатывания компаратора 22 выдает сигнал лог. "1". flo истечении этого времени триггер 28, регистр 20 сдвига и счетчик импульсов устанавливаются в нулевое состояние подачей на их обнуляющие входы сигнала лог. "0" с выхода формирователя 21.

Таким образом, предлагаемое устройство позволяет осуществлять надежное распознавание сложных составных фазоманипулированных сигналов.

Формула изобретения

Устройство для распознавания сигналов объектов, содержащее первый узкополосный фильтр, вход которого соединен с выходом первого квадратора, а выход подключен к входу амплитудного детектора, первый компаратор, вход которого соединен с выходом амплитудного детектора, второй компаратор, выход которого подключен к одному входу первого элемента И, третий компаратор, второй элемент И, первый интегратор, первый формирователь тактирующих импульсов, первый элемент задержки, первый и второй триггеры, второй узкополосный фильтр и первый инвертор, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности распознавания со-. ставных фазоманипулированных сигналов, оно содержит второй квадратор, информационный вход которого соединен с выходом второго узкополосного фильтра, фильтр нижних частот, информационный вход которого подключен к выходу второго квадратора, делитель напряжения, информационные входы которого соединены с выходами амплитудного детектора и фильтра нижних частот, ключ, входы которого подключены к выходам первого компаратора и делителя напряжения, а выход соединен с входом первого формирователя тактирующих импульсов и с информационным входом первого интегратора, синхронизирующий вход которого подключен к выходу первого формирователя тактирующих импульсов, а выход соединен с входом первого элемента задержки, второй интегратор, информационный вход которого подключен к выходу

20

25 мирователя тактирующих импульсов, а вы30

55 первого компаратора, синхронизирующий вход соединен с выходом первого формирователя тактирующих импульсов, второй элемент задержки, вход которого подключен к выходу второго интегратора, четвертый компаратор, выход которого соединен с входом первого инвертора, выход которого подключен к инверсному входу первого триггера, группа делителей напряжения, входы которых соединены с выходом второго элемента задержки, а выходы подключены к соответствующим информационным входам второго, третьего и четвертого компараторов, другие информационныевходы которых соединены с выходом первого элемента задержки, второй инвертор, вход которого подключен к выходу третьего компаратора, а выход соединен с вторым входом первого элемента И, пятый компаратор, информационные входы которого подключены к выходам первого и второго элементов задержки, а выход соединен с прямым входом первого триггера, второй элемент И, один вход которого подключен к выходу первого форход соединен с тактовым входом первого триггера, счетчик, счетный вход которого, подключен к выходу первого формирователя тактирующих импульсов, а выход соединен с третьим входом первого элемента И, регистр сдвига, тактирующий вход которого подключен к выходу первого формирователя тактирующих импульсов, элемент ИЛИ, входы которого соединены с выходами первого триггера и первого элемента И, а выход подключен к информационному входу регистра сдвига, третий инвертор, вход которого соединен с соответствующим выходом регистра сдвига, третий элемент И, входы которого подключены к выходам регистра сдвига и третьего инвертора, а выход соединен с одним входом второго триггера, одновибратор, вход которого подключен к выходу первого компаратора, а выход соединен с другим входом второго триггера, четвертый инвертор, вход которого подключен к выходу счетчика, а выход соединен с другим входом второго элемента И, и второй формирователь тактирующих импульсов, вход которого подключен к выходу первого компаратора, а выход соединен с установочными входами счетчика, регистра сдвига и второго триггера, при этом входы первого квадратора и второго узкополосного фильтра являются информационным входом устройства.

1674183

Составитель A.Ðoìàíîâ

Техред M.Mopãåíòàë Корректор О.Кравцова

Редактор А.Долинич

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 1р1

Заказ 2926 Тираж 368 Подписное

8НИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035. Москва, Ж-35, Раушская наб„4/5