Последовательный регистр сдвига

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике. Цель изобретения состоит в уменьшении статического потребления энергии. Регистр состоит из ячеек памяти (разрядов), входного и выходного преобразователей. Для корректной работы необходимо, чтобы все переходные процессы в элементах регистра завершались в течение одного такта синхронизации, а входные сигналы должны изменяться в первом такте работы регистра, когда входной преобразователь отсечен от входов. 3 ил.

союз советских

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)5 6 11 С 19/00

ГОСУДАРСТВEHHblй КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К AQTOPCKOMY СВИДЕТЕЛЬСТВУ (21) 4492143/24 (22) 10.10.88 (46) 30.08.91. Бюл. ¹ 32 (71) Ленинградский электротехнический институт им.В.И.Ульянова (Ленина) (72) В.И.Варшавский, М.А.Кишиневский, Н.M.Êðàâ÷åíêî, В.Б.Мараховский и А.P.Tàóáèí (53) 681.327.66(088.8) (56) Букреев И.Н. и др. Микропроцессорные схемы цифровых устройств. — M.: Сов. радио, 1975, с.223 — 227.

Авторское свидетельство СССР № 734809, кл. G11 С 19/00,,1980.

Изобретение относится к автоматике и вычислительной технике.

Цель изобретения — уменьшение статического потребления энергии.

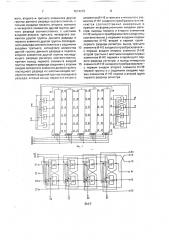

На фиг. 1 приведена схема четырехтактного последовательного регистра сдвига; на фиг. 2 — схема одного разряда регистра (ячейки памяти); на фиг. 3 — временная диаграмма работы регистра.

Регистр состоит из ячеек памяти (разрядов) 1, входного 2 и выходного 3 преобразователей.

Входной 2 и выходной 3 преобразователи содержат элементы И-НЕ 4 — 7 и 8 — 11 соответственно, причем выходы 12-15 последней ячейки 1 соединены соответственно с входами элементов 9 и 11, 8 и 11, 9 и 10 и 8 и 10 преобразователя 3, выходы элементов 8 и 9 являются соответственно прямым 16 и инверсным 17 выходами регистра и соединены с входами элементов 9 и

8 соответственно, выходы элементов 10 и 11

„„5О „., 1674263 А1 (54) П 0 С Л Е Д 0 В А Т Е Л b H Ы Й P Е Г И С T Р

СДВИГА (57) Изобретение относится к автоматике и вычислительной технике, Цель изобретения состоит в уменьшении статического потребления энергии. Регистр состоит из ячеек памяти (разрядов), входного и выходного преобразователей. Для корректной работы необходимо, чтобы все переходные процессы в элементах регистра завершались в течение одного такта синхронизации. а входные сигналы должны изменяться в первом такте работы регистра, когда входной преобразователь отсечен от входов. 3 ил. преобразователя 3 соединены соответственно с входами элементов 5, 7 и 4, 6 преобразователя 2, прямой l8 и инверсный 19 входы регистра соединены соответственно с входами элементов 6, 7 и 4, 5 преобразователя 2, выходы элементов 4-7 преобразователя 2 соединены с соответствующими входами 20 — 23 первой ячейки регистра 1.

Каждая из ячеек памяти регистра имеет входы 20 — 23 и 24, 25 и выxîäû 12 — 15, 26, 27.

Входы 20 — 23 каждой из ячеек регистра, кроме первой, соединены с выходами 12-15 предшествующей ячейки, входы 24 и 25 каждой из ячеек регистров соединены с выходами 26, 27 последующей ячейки, причем входы 24, 25 последней ячейки регистра соединены с выходами 26, 27 первой ячейки.

Каждая из ячеек регистра имеет также входы 28-31, соединенные с входами 32-35 регистра, на которые подается четырехтактная синхронизирующая после1674263 довательность сигналов. Входы 18, 19 и выходы 16, 17 являются парафазными.

Ячейка памяти (разряд) регистра выполнена на элементах И-НЕ 36-43 и содержит первую и вторую группы из четырех элемен- 5 тов И-НЕ, элементы 36, 38, 40, 42 и 37, 39, 41, 43 соответственно. Элементы 36-39 образуют первый четырехстабильный триггер, элементы 38 — 41 — второй, а элементы 40-43 — третий. Каждая пара элементов И-НЕ 36, 10

37 и 38,39, 40, 41 и 42, 43 соединена с одним из тактирующих входов ячейки 28 — 31 соответ, ственно. Для обеспечения связи между четырехстабильными триггерами входы.20 — 23 ячейки регистра ""îåäèíÿþòñÿ с входами 15 элемент,в 37, 36, 39, 38 соответственно, выходы элементов 36 — 39 — с входами элементов 41, 40, 43, 42 соответственно. Каждый из входов 22, 23 ячейки регистра соединен также с входами элементов 36, 37, 20 а каждый из входов 24, 25 — с входами элементов 42, 43. Выходы элементов 36, 37, 40 — 43 соединены с выходами ячейки регистра 26, 27, 12-15 соответственно.

Регистр сдвига работает следующим 25 образом.

По поведению входа-выхода предлагаемый регистр являе-ся двоичным регистром сдвига на 2п разрядов, а по внутреннему поведению — четвертичным регистром сдви- 30 га на и разрядов. В каждой ячейке четырехстабильные триггеры, образованные элементами 36 — 39 и 40--43, будем называть основным и вспомога ельным соответственно. В процессе функционирования ка>к- 35 дая i-я ячейка регистра хранит информацию, соответствующую i-му и (n+i)му разрядам двоичного регистра сдвига в коде О/4 (один нуль — три единицы) в основном либо во вспомогательном четырехста- 40 бильном триггере. Другой триггер каждой ячейки в это время находится в состоянии гашения ("1" на выходе всех его элементов).

Входной преобразователь перекодирует информацию, поступающую на вход регист- 45 ра и из его и-го разряда в виде двух парафазных кодов, в код 0/4, а выходной преобразователь осуществляет обратное преобразование информации в коде О/4, снимаемой с выходов и-й ячейки, в парафаз- 50 ный код и-го и 2п-го разрядов регистра, последний из которых снимается с выхода регистра.

Выходы входного преобразователя подсоединяются к входам основного тригге- 55 ра первой ячейки, а входы выходного преобразователя — к выходам вспомогательного триггера последней ячейки. Наличие триггерной связи между элементами 8 и 9 выходного преобразователя позволяет отключаться от выходов вспомогательного триггера последней ячейки, когда он находится в состоянии гашения (все "1"). При этом на выходах 16 и 17 регистра сохраняется парафазное значение 01 или 10.

Обозначим входы регистра 18, 19 через

Х1, Х2, выходы элементов 4-11 — через У1, У2, УЗ, У4, 23, Z4, Zi, 22, выходы 12 — 15 последней ячейки — через U1, U2, UÇ, U4.

Принятые в регистре соглашения о кодировании, реализуемом входным и выходным преобразователями, можно задать таблицами истинности 1 и 2. Таблица 1

Х1 Х2 Zi 22 У1 У2 У3 У4

О 1 О 1 О 1 1 1

О 1 1 О 1 О 1 1

1 О О 1 1 1 О 1

1 О 1 О 1 1 1 О

Таблица 2

U1 U2 U3 U4 Z1 Z2 Z3 24

О 1 1 1 О 1 О 1

1 О 1 1 О 1 1 О

1 1 О 1 1 О О 1

1 1 1 О 1 О 1 О

На фиг, 3 приведена временная диаграмма работы регистра, Полный период синхронизации состоит иэ двух 4-тактных фаз. На первой фазе (такты с 1-го по 4-й) происходит передача информации из основных триггеров всех ячеек регистра во вспомогательные, причем основные триггеры переходят в состояние гашения, а на 2-й фазе (такты с 5-ro по 8-й) происходит передача из вспомогательных триггеров i-й ячейки в основные триггеры (!+1)-й ячейки, а вспомогательные триггеры переходят в состояние гашения. Если "О" хранится на первом или втором элементах основного (элементы 36, 37) или вспомогательного (40, 41) триггеров, то передача информации в следующий триггер и гашение данного осуществляются на первых двух тактах фазы (такты 1, 2 или 5, 6), а при "О" на третьем или четвертом элементе (38. 39 или

42, 43 ) — на двух последних тактах (3, 4 или

7, 8).

Пусть на вход регистра поступает некоторый парафазный код (например, 01), в каждой из ячеек регистра хранится некоторая информация в коде О/4 на основных триггерах, пусть в 1-й ячейке это будет код

0111, а в и-й ячейке — код 1101, à все вспомогательные триггеры находятся в состоянии гашения 1111, На парафазном выходе регистра триггер из элементов 8, 9 выходно1--4. 1

ro преобразователя хранит некоторый код (например, 10). На входе входного преобразователя. соединенного с выходом выходного преобразователя, — кад 00 и, следовательно. выход входного преобразователя находится в состоянии гашения

1111. На 1-й фазе синхронизации (такты 14) происходят передача информации из основного Во вспомогательный триггеры и гашение основных триггеров, причем для первой ячейки при таком коде это происходит на первых двух, а для и-й — на последних двух тактах. Теперь уже во вспомогательном триггере 1-й ячейки хранится кад 0111, а во вспомогательном триггере и-й — 1101, Основные триггеры находятся в состоянии гашения 1111, На выходе элементов 8 — 11 выходного преобразователя появляется код

0110, а на выходах элементов 4-7 входного преобразователя — код 1011. На второй фазе синхронизации (такты 5-8) происходят передача информации из вспомогательных триггеров в основные триггеры следующих ячеек и гашение вспомогательных триггеров, в основной триггер 1-й ячейки записывается код 1011 с выхода входного преобразователя, в основной триггер 2-й ячейки — код 011". с выходов вспомогательного триггера 1-й ячейки. На парафазном выходе регистра фиксируется код 01. на выходах элементов 10, 11 — код 00, а выходной преобразователь будет в состоянии гашения — 1111.

Длительность всех тактов, кроме 4-ro u

8-го, равна задержке элемента t. Длительность 4-го и 8-го тактов равна удвоенной задержке элемента 2t, чтобы к началу вто-. рой фазы работы входной преобразователь успел перейти из состояния гашения в рабочее состояние, а к началу первой фазы входной преобразователь успевал "атсечься" от входа регистра до начала изменения входных сигналов регистра. Таким образам, длительность периода работы регистра Т = 10t.

За 1 цикл синхронизации (8 тактов — 10t) регистр производит сдвиг информации на один разряд, а за 20 циклов парафазный код, поданный на вход регистра, достигает парафазнога выхода регистра.

Для корректной работы необходимо, чтобы все переходные процессы в элементах регистра завершались в течение одного такта синхронизации, а входные сигналы должны изменяться на первом такте работы регистра, когда входной преобразователь отсечен от входов.

В прототипе данного регистра ячейка из четырех элементов И-HE хранит один бит информации, причем в течение трех тактов каждой фазы в коде О/4, а в течение 1-го

1зктз (пр 1 передаче информации между основным и вспомогательным;риггерзми) --2 нуля из 1. В предложенном реп4стре ячейка хранит 2 битз, з распределение нулей — 1 из

8 н l е гение pBX TBKTUB I; 2 14 8 B T B!4!1B одного такта, Т",ким образам, предложенный регистр потребляет " ;iåðãèè н дн- рВВВ мег4ьше, чем известный

Формула изобретения

Последовательный регистр сдвига, содержащий н каждом разряде первуIQ и ВТ0peto группы из четырех элементан И-НЕ, причем ныхадьг первого, второго, третьего и четвертого элементов И-НЕ каждой группы к;.-. ê,BBãî разряда соединены с первыми вход-1л1:1 второго, третьего, четнертага эг1еме14тон И-НЕ данной группы дзннаго разряда и пепнага элемента И-HE данной группы паследугащега разряда соответственно и с парыл4и входами четнертога элемента ИНЕ дзн11ай4 группы пред11дущега разряда, первого, второго и третьего эл-:Ilå!4òoã И-НЕ дзниай группы данного разряда гcoTBBTcTнениа, третьи входы первого, второго, третьего и четвертого элементов И-НЕ каждой гауппы кзждага разряда являются саатB ñ ò ñ ò B ñ н и о и е р н bl м, в т о р ь! м, T (:.B T ü и м и четвертым тактовыми входами регистра, а т л и ч з ю шийся тем, чта, с целью уменьшения статического потребления энепгии, н него введены входной и выходной преобразователи, каждый из которых содержит первый, второй, тра гий и четвертый элементы И-НЕ, причем гыхады третьего и четнертага элементов И-НЕ первой групг;ы и третьего и четвертого элементов

И-НЕ нтарай группы соединены соответственна с входами второго I; четвертого, BTQрого и третьего, первого и четвертого и первого и третьего элементов И-НЕ выходного преобразователя, выход первого элеMQIIT3 И-НЕ выходного преобразователя соединен с входом второго элемента И-HE данного преобразователя и является прямым.:зыхадал1 регистра, выход второго Bfl8мента И-Н Е выходного преобразователя соединен с входом первого элемента И-НЕ данного преобразователя и является инверснь1м выходом регистра, выходы третьего и четвертого элементов И-НЕ выходного преобразователя соединены соответственно с первыми входами второго и четвертого и первого и третьего элементов И-НЕ вхадного преобразователя, выходы первого, второго, третьего и четвертого элементов И-НЕ каждой группы каждого разряда соединены с четвертыми входами четвертого элемента другой группы предыдущего разряда, пер16742 F)3

2Ì

28

73

29 вого, второго и третьего элементов другой группы данного разряда соответственно, с пятыми входами первого, второго, третье о и четвертого элементов другой группы данного разряда соответственно, с шестыми входами второго, третьего, четвертого элементов другой группы данного разряда и первого элемента другой группы последующего разряда соответственно и с седьмыми входами третьего, четвертого элементов другой группы данного разряда и первого, второго элементов другой группы последующего разряда регистра соответственно, причем выход первого элемента каждой группы первого разряда соединен с вторым входом четвертого элемента данной группы последнего разряда и с шестым входом четвертого элемента другой группы последнего разряда, вторые входы первого и второго элементов И-Н Г и третьего и четвеотого элементов И-НЕ входного преобразователя являются сОответственно инверсным и прямым информационными входами реги5 стра, выходы первого и второго элементов

И-НЕ входного преобразователя соединены соответственно с первыми входами первых элементов И-НЕ второй и первой групп первого разряда регистра, выход третьего

10 элемента И-HE входного преобразователя— с первым входом второго элемента И-НЕ второй группы и с шестыми входами первых элементов И-НЕ первой и второй групп пер- вого разряда регистра, а выход четвертого

15 элемента И-НЕ входного преобразователя— с первым входом второго элемента И-НЕ первой группы и с седьмыми входами первых элементов И-НЕ первой и второй групп первого разряда регистра.

1674263 (3Z)5 (ЗЗ) Tg

О4) s (35) Ъ

18

1Ф

5 б

Я.f

37.1

ЗИ

Ю

481

Ô11 фЯ.1

4И

3И

378

ЯГ

_#_2

402

4Q

ФГГ

ФЗГ (Ю)8

/17)У

/О

11

Составитель А. Дерюгин

Редактор А. Маковская Техред M,Ìoðãåíòàë Корректор М, Демчик

Заказ 2930 Тираж 329 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издагельский комбинат "Патент", г. Ужгород, ул.Гагарина, 101