Формирователь импульсов

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой технике и может быть использовано в интегральных схемах устройств обработки и хранения информации для быстрого формирования выходных логических уровней при наличии емкостной нагрузки. Цель изобретения - повышение быстродействия за счет обеспечения предварительной установки в высокоимпедансном состоянии. По сигналу предустановки на выходе формирователя устанавливается промежуточный уровень выходного напряжения, в связи с чем укорачивается процесс установления логического уровня при изменении информационного сигнала. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛ ИСТИЧ Е С К ИХ

РЕСПУБЛИК (я)э Н 03 К 19/094

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

В (21) 4606543/21 (22) 15.11.88 (46} 30.08.91. Бюл. f4 32 (71) Московский институт электронной техники (72) Н. А. Подопригора, П. M. Гафаров и Е. Il, Сеничкин (53) 621.374(088.8) (56} Патент EP 5Ф 0072686, кл. Н 03 К 19/094, 1983, Кармазинский А. Н. Синтез принципиальных схем цифровых элементов на МДП

-транзисторах, M. Радио и связь, 1983, с.

159-178, рис.4.19в. (54) ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ

Изобретение относится к цифровой технике и может быть использовано в интегральных схемах устройств обработки и хранения информации для быстрого формирования выходных логических уровней при наличии емкостной нагрузки, . Цель изобретения — повышение быстродействия путем обеспечения предварительной установки в высокоимпедансном состоянии.

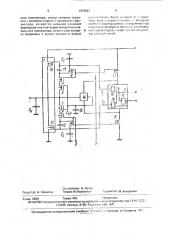

На чертеже приведена принципиальная схема формирователя.

Формирователь импульсов содержит выходной инвертор 1, блок 2 управления,и-канальные транзисторы 3-6, р-канальные транзисторы 7-10, конденсаторы 11-13, инвертор 14, в выходном инверторе 1 — n-канальный транзистор 15 и р-канальный транзистор

16, а в блоке 2 управления — инвертор 17, элемент ИЛИ 18, и элемент ИЛИ-НЕ 19.

Вход и выход инвертора 17 блока 2 управления соединены с соответствующими входами элемента ИЛИ 18 и элемента ИЛИНЕ 19, другие входы которых и вход инвер„„5U„„1674361 А1 (57) Изобретение относится к цифровой технике и может быть использовано в интегральных схемах устройств обработки и хранения информации для быстрого формирования выходных логических уровней при наличии емкостной нагрузки. Цель изобретения — повышение быстродействия путем обеспечения предварительной установки в высокоимпедансном состоянии. По сигналу предустановки на выходе формирователя устанавливается промежуточный уровень выходного напряжения, в связи с чем укорачивается процесс установления логического уровня при изменении информационного сигнала. 1 ил, тора 17 соединены с входными клеммами формирователя. Выходы элементов ИЛИ 18 и ИЛИ-НЕ 19 соединены с затворами и- и р-канальных транзисторов 15 и 16 выходного инвертора 1, истоки которых соединены с шиной питания и общей шиной, стоки — с выходной клеммой формирователя, входом инвертора 14 и стоками и- и р-канальных транзисторов 3 и.7, затворы которых соединены с выходом инвертора 14 и через конденсатор 13 с общей шиной, истоки — со стоками соответствующих и- и р-канальных транзисторов 4 и 8, истоки которых соединены со стоками р- и п-канальных транзисторов 9 и 5 и через конденсаторы 11 и 12 соответственно с затворами р- и и-канальных транзисторов 16 и 15 выходного инвертора 1 и истоками р- и п-канальных транзисторов 9 и 5, затворы которых соединены с затворами соответствующих и и р-канальных транзисторов 4, 10 и 5, 6 соответственно и входными клеммами формирователя. Шина питания через р-канальный транзистор 10 соединена с шинами питания инвертора 14 и блока

167436 I

2 управления, другие шинь! пита}нl>IA которых через п-канальный трэнз:cTGp 6 CGBpMнены с общей шиной.

Формирователь импульсов работае! следующим Образом.

Г!ри подаче cMIHBBGB Bbl};0};01.0 ypoB>I,I на зэтворы трэнзистооов 5, 6 k 8 и Вход инвертора 17 при низком уровне сигнала на

ЗатВОрэх транзисторов 4, 9 и 1 0 нэ Выходах блока 2 управления уста нэ1!!и 1вэ ются cQG I BB}ствующие логические уровни, закрываю}цие транзисторы 15 и l6 Bblxou}AQrQ !AI;BBpTGp:I

1, На ВыхОДнОЙ клемме ф0рми!}овэтеля третье состояние, ()ткрь!Ты транзис-го,зы 5 1

9 разряда конденсаторов I I и 1":! Обрат IGЙ связи л транзисторы 6 и 10. т!а конq=-,нсэторе 13 через инвертор 14 уста}}эвлив=}етс}1 логический уровень, противоположный том:, KQTopbIA сохраняется нэ вы>:оде формMрователя благодаря значАтельной емкост ной нагрузки, ПрЕдПОЛОжИМ, ЧтО На ВЬ!Хсдт! бЫЛ Сформирован высокий логический уровень

О вых = U }}и ГОГДЭ КО}!ДЕ}!Сато!> 13 раэряжен. Из транзисторов 7 и Оаткрыт транзистор

7. Транзисторы 4 и 8 закрыл.и. В реж}Аме работы "Предустановка" зэкрыва}Отся транзиcT0pbl 5, 6, 9 и 1О }л откр}ыва!отся транзис-.,оры

4 и B. Тс1к кэк из трэнз IQTQpOB У и > Открыт только транзистор 7, та ььtcÎKQå напряж::-:ние с выхода через цепь обратной связи подается на затв(}р тргнзист}ара 15, Е} начальный момент переходного процесса нB затворе транзистора 15 уста}-:.-вллвается напРЯ>кение Ucp О}}!и/(1+С2/(n) Б РезУльгэте открывается Выхс}дной транзистор !5.

Напряжение на выходе формMpQB"-тегя, а

TaKv<8 и на затворе транзистора 15 I.I;;нижается. Если будет Выполнено условие

О" (О вых+О вых)/2 = иг /2, ЕСли пРВРУ- та новке предшествова}1 на Выходе фсрмироВатЕЛя НИЗКИЙ ЛОГИЧЕСКИЙ урОВЕНЬ О "вых =- !!

В, то предустановка будет проходи;ь за сче, обратной связи через цепь: rpaHB-.«G;op ",. и 4, конденсатор 11. Для того, чтобы }»ь!>.Од ное напряжение также у:танавл;Banось в-ЛИЧИНОЙ О,лп/2, ДОЛ>КНО БЬ:Г}ОЛНЯТЬСЯ >icliQB(А<}

Сп/Q=.20ор(О}}п-2ОЛ!}l, где Оор-г!Орог;.}BQБ на пряжение р-канального выходного транз}1стора 1, С1 — суммарная г:рразит!!Эя емко!..Ть

На !}ОДЛГ}>ЛК>} ПРИВ-,прь!)- - Я K да; В}Л> >,,.,!1" зистпра 1. чения предварительной установки в высоко4О импедансном состоянии, в него Введе>1ы третий и четвертый р-канальныетранзиСТоры и третий и четвертый и-канальные т»ран" 1. зисторы, инвертор, первый, второй итретий конденсаторы, NcTGK второго р-канального

45, транзистора соединен со стоком третьего и-канального транзистора и через первый конденсатор — с затвором и-канального г> 1„} затвором р-канального транзистора выход, }!! Ного пнвеотооэ и стоком третьего r-канальУ t

} (>:„}

"I г

i!Осле проведения предустэнОВки Бь}ходного напряжения Восстанавливаются исходные зла}!ения логических уровней HB!

}Ходах управле!гия предустановкой формирователя. Окончательное формирование лог}Аческих уроВней "0" или "1" нэ Выходе форм}АрОвэтеля B соОтветствии со значени" ем входного информационного сигнала на Г входах элемента ИЛИ вЂ” НЕ 18 и инвертора 17!} блока1}управ}1ения сопровождаешься уменьшенным Вдвое перепадом напряжения, э

Вместе с тем и временем переключения.

Формула изобретения

Формирователь импу11ьсов, сОр8р>KBIIII:й блок управления, Выходной MHBQpтор, первый и Втс}рой р-канальные трэ!!зисторы, первый IÀ В i opQM и-канальные тра нзисторь!, в блоке уг}равления — инвертор„элемент

ИЛИ и элемент ИЛИ вЂ” HE, вход инвертора и первый вход злемейта ИЛИ вЂ” HF. блока управления соединень с первой входной клеммой формирователя, выход инвертора соединен с первым входом элемента ИЛИ, второй вход элемента ИЛИ и второй вход элемента ИЛИ- НЕ соединены с Второи выходной клеммой формирователя, выходэлеме -ITB ИЛИ и выход элемента ИЛИ вЂ” НЕ блока управленля соединены cGGTBGTGTBBHно с .затворами р- и и-канальных транзисторов выхо(!Ного инвертора, истоки которых соединены с шиной п}лтания и Общей шиной, а стоки — с Выходной клеммой формирователR и стоками }18pBb}M p- } A-канальных транзистооов, затворь! которых соедлнены, а McTQKM соединены cG стокам}л BTQpblx p" и и-канальных транзисторов соответственно, о —: л и ч а ю шийся тем, что, с целью повышения быстродействия путем обеспетранзистора Выходного инвертора и истоком третьего и-ка}-!Эльного транзистора, затвор;(оторого соединен с затвором Второго р-канального транзистора, третьей входной клеммой формирователя и затвором четвер}ОГО П-KBI!ЭЛЬНОГО траНЗИСТОра, MCTOK И СТОК ,QTGpQ Q cG8pMH8rIbi с об цей IMHQM и первОЙ шиной питал}ля блока управления и инверторэ, исток BTQp010 и-канального транзистора с08динен со стоком третьего р-канального транзистора и через второй конденсатор -с

Составитель В. Бутин

Техред M,Mîðãåíòçë оррек гор М, Кучера вая

Редактор А, Лежнина

Заказ 2934 Ч ираж 443 Подписное

ВКИИПИ Государственного комитета по изобрете:-л ям и открытиям 1р!4 ГКНТ ССС.

1 "3035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат Г зтент, г. Ужгород,. ",.ÃßÃý ýèH3, "01 ного транзистора, затвор которого соединен с затвором второ-о и-канального транзистора, четвертой входной клеммой формирователя и затвором четвертого р-канального транзистора, исток ч сток которого соединены с шиной питания и второй шк:- о 4 питайi:i," блока iiп >авлсi:. !я .". iнвео т0,35, вход к1 горого сиз .инеи с выходной клеммой формирователя, в:-. ход инвертора соединен с затворами пер :. ы;, - и и-каналь5 ных транзисторов ..: через тре-.ий кон .à,c==, Toj: с î2i (&!1 к иной.