Устройство для измерения коэффициента ошибок в цифровых трактах передачи информации

Иллюстрации

Показать всеРеферат

Изобретение относится к технике связи. Цель изобретения - уменьшение времени измерения за счет уменьшения времени установки синхронизации. Устройство содержит генератор 1 контрольного сигнала, детекторы 2 - 4 ошибок, счетчики 5 - 9, накопитель 10, элемент ИЛИ 11, элемент задержки 12, анализатор 13 структуры сигнала несовпадений, генератор 14 эталонного сигнала, блок 15 синхронизации, блок 16 выбора интервалов, решающий блок 17 и блок 18 индикации. Сигнал с выхода анализатора 13 поступает на вход блока 15, осуществляя его подстройку в направлении, противоположном направлению сбоя синхронизации, тем самым уменьшается время вхождения устройства в синхронизацию. Устройство по п. 2 формулы отличается выполнением анализатора 13. 1 з.п. ф-лы, 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛ ИСТИЧ Е СКИХ

РЕСПУБЛИК (51)5 Н 041 12/26

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОбРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4745999/09 (22) 03.10.89 (46) 30.08.91. Бюл. 1ч 32 (71) Московский институт инженеров гражданской авиации (72) С.Ж.Кишенский, В.3 Игнатьев, В.Б.Панова и 0.1О.Христенко (53) 621.391,833 (088.8) (56) Авторское свидетельство СССР

М 1040617, кл. Н 04 L 11/08, 1981. (54) УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ КОЭФФИЦИЕНТА ОШИБОК В ЦИФРОВЫХ

ТРАКТАХ ПЕРЕДАЧИ ИНФОРМАЦИИ (57) Изобретение относится к технике связи.

Цель изобретения — уменьшение времени

Устройство относится к технике связи и может быть использовано для построения контрольно-измерительной аппаратуры цифровых систем передачи.

Цель изобретения — уменьшение времени измердния за счет уменьшения времени установки синхронизации.

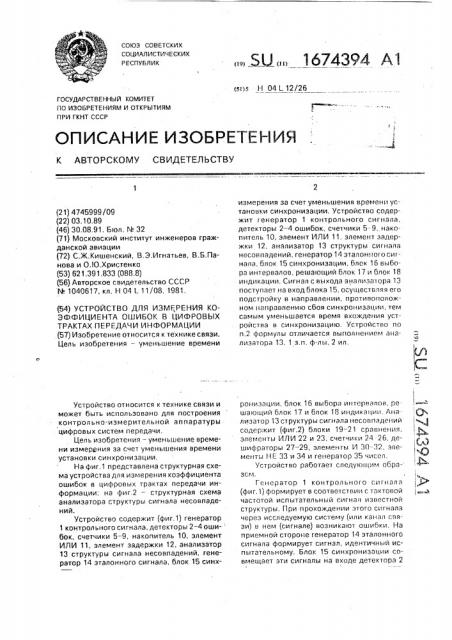

На фиг.1 представлена структурная ñõåма устройства для измерения коэффициента ошибок в цифровых трактах передачи информации; на фиг.2 — структурная схема анализатора структуры сигнала несовпадений.

УстрОйствО содержит (фиг.1) генератор

1 контрольного сигнала, детекторы 2-4 ошибок, счетчики 5-9, накопитель 10, элемент

ИЛИ 11, элемент задержки 12, анализатор

13 структуры сигнала несовпадений, генератор 14 эталонного сигнала, блок 15 синх„„ Ж„„1674394 Al измерения за счет уменьшения времени установки синхронизации. Устройство содержит генератор 1 контрольного сигнала, детекторы 2 — 4 ошибок, счетчики 5-9, накопитель 10, элемент ИЛИ 11, элемент задержки 12, анализатор 13 структуры сигнала несовпадений, генератор 14 эталонного сигнала, блок 15 синхронизации, блок 16 выбора интервалов, решающий блок 17 и блок 18 индикации. СигнЯл с выхода ЯИЯлизаторЯ 13 поступает на вход блока 15, осуществляя eI o подстройку в направлении, противоположном направлению сбоя синхронизации, тем самым уменьшается время вхождения устройства в синхронизацию. Устройство по п.2 формулы отличается выполнением анализатора 13. 1 з.п. ф-лы, 2 ил. ронизяции, блок 16 выбора ингервялов, решающий блок 17 и блок 18 индикации. Анализатор 13 структуры сигнала несовпадений содержит (фиг.2) блоки 19-21 сравнения, элементы ИЛИ 22 и 23, счетчики 24 26, дешифраторы 27 — 29, элеменгы И 30-32, элементы НЕ ЗЗ и 34 и генератор 35 чисел.

Устройство работает следующим обря3 о.м.

Генератор 1 контрольного сигнала (фиг.1) формирует в соответствии с тактовой частотой испытательный сигнал известной структуры. Г1ри прохождении э ого сигналя через исследуемую систему (или канал ".вязи) в нем (сигнале) возникают ошибки. На приемной стороне генератор 14 эталонного сигнала формирует сигнал, идентичныЙ испытательному. Блок 15 синхронизации совмещает эти сигналы на входе детектора 2

1674394 ошибок по фазе, при этом на выходе детектора 2 ошибок формируетсл поток ошибок (сигнал несовпадений) посредством поэлементного сравнения эталонного и контрольного сигналов, Элемент задержки 12 осуществляет формирование двух сигналов, идентичных эталонному, но сдвинутых соответственно относительно контрольного в интервале синхронизма устройства на один и на два такта. Таким образом, на детектор

2 ошибок поступает эталонный сигнал, опережающий на один такт сигнал, принимаемый из канала связи, а на детектор 4 поступает аналогичный эталонный сигнал, запаздывающий относитеп ьно контрольного на один такт. Элемент задержки 12 может быть выполнен, в частности, на регистре сдвига емкостью три разряда, Сигнал несовпадений с выхода детектора 2 ошибок (в интервале синхронизма— истинный сигнал несовпадений) поступает на блок 16 выбора интервалов, где разбивается на блоки по гп элементов. Сигнал с выхода блока 16 выбора интервалов поступает на счетчик 5, где подсчитываются переданные символы (или блоки, что не имеет существен ного значения), соответствующие работе устройства в условиях поддержания синхронизма. Кроме того, сигнал несовпадений (поток ошибок) поступает на накопитель 10 и записывается в нем, В качестве накопителя может выступать также, например, регистр сдвига.

Сигналы с трех детекторов 2-4 поступа1от на соответствующие счетчики 7 — 9, где фиксируется текущее количество ошибок.

При синхронизме устройства вероятность появления ошибки на выходе детектора 2 равна (с достаточной точностью) вероятности ошибки в исследуемой системе (канале свлзи), Обычно эта величина даже для плохих каналов не превышает 10, В то же время, вероятность появления ошибки на выходах детекторов 3 и 4 приблизительно составляет 0,5. Р моменты окончания очередного блока, сформированного блоком 16 выбора интервалов через каждые m тактов в анализаторе 13 структуры сигнала несовпадений осуществляется анализ содержимого счетчиков 7, 8» 9, Их содержимое сравнивается (фиг,2) на блоках 19 — 21 сравнения с пороговым кодом, сформированным в генераторе 35; Значение этого кода выбирается таким, чтобы содержимое счетчиксв 7-9 при сбое синхронизации превышало значение порогового кода, а содержимое того же счетчика при синхронной работе устройства было бы меньше порогового кода, Таким образом, при синхронной работе устройства в момент поступления разрешающего сигнала с блока

16 на блоки 19-21 сравнения с выходов блоков 19 и 21 сравнения (поскольку в них поступают заведомо большие значения кодов

5 счетчиков 8 и 9, работающих в несинхронных каналах), являющихся выходами типа

"Больше", что говорит о том, что содержи. мое этих счетчиков больше порогового кода, поступают сигналы на информационные

10 входы счетчиков 24 и 26, С первого выхода блока 20 сравнения (выход типа "Больше" ) сигнала не поступает, однако формируется сигнал на его втором выходе (выход типа

"Меньше" ) и через элемент WIN 23 анали15 затора формирует сигнал сброса счетчика

25 (фиг.2), Так происходит во все время работы устройства в синхронном режиме.

При сбое тактовой синхронизации (как указывалось ранее, это основная причина

20 выхода устройства из синхронизма) фактически контрольный и эталонный сигналы оказываютсл сдвинутыми друг относитель- ° но друга в детекторе 2 ошибок на один такт и теперь в детекторе 2 вероятность ошибки

25 становится равной 0,5. Одновременно в одном из остальных детекторов 3 или 4 (поскольку сдвиг происходит на один такт) оба сигнала оказываются синфазными и вероятности ошибки в соответствующем детекто30 ре 3 или 4 становится равной вероятность ошибки в канале связи, то есть резко падает. Рассмотрим конкретный вариант работы устройства при таком сбое тактовой синхронизации, когда сигнал с генератора 14 в

35 результате сбоя сдвигается в сторону отставания относительно контрольного сигнала, приходящего с выхода исследуемой системы (канала связи).

В этом случае контрольный сигнал пере40 стает совпадать по фазе с входным сигналом детектора 2, но становится синфазным с сигналом, поступающим на другой вход детектора 3, ранее опережавшим контрольный сигнал, 45 При рассинфазировании сигнала, поступающего на вход детектора 2 ошибок с генератора 14 и контрольного сигнала с первого выхода блока 20 сравнения с окончанием очередных блоков информации

50 поступают информационные импульсы (" Больше" ) на информационный вход счетчика 25. Модуль счета данного счетчика (счетчика 25) выбирается таким образом, чтобы к моменту формирования сигнала с

55 выхода связанного с ним дешифратора 28 связанные с изменением статистики ошибок переходные процессы в трех детекторных каналах закончились (минимальный модуль этого счетчика равен двум, поскольку сбой может произойти в середине блока

1674394 информации и лишь с начала следующего блока содержимое счетчика 24 будет пропорционально вероятности ошибки в канале связи), То есть счетчик 25 является демпфирующим или усредняющим устройством, повышающим надежность выявления сбоя тактовой синхронизации, и различения сбоя и пакета ошибок в канале связи.

Дешифратор 28 настроен на кодовую комбинацию. соответствующую модулю счета счетчика 25. Его срабатывание (при модуле счета счетчика 25 равном К) через К блоков после сбоя синхронизации вызывает формирование сигнала опроса состояния дешифраторов 27 и 29 на элементы И 30 и

33.

Счетчики 24 и 26 работают следующим образом, Сигнал "Больше" с устройства сравнения добавляет единицу к содержимому счетчика, а сигнал "Меньше" сбрасывает счетчики 24 и 26 в исходное (нулевое) состояние. При достижении некоторого максимального состояния, в отличие от счетчика

25 счетчики 24 и 26 остаются в этом состоянии (с максимальным содержимым независимо от дальнейшего поступления информационных импульсов на их информационные входы. Дешифраторы 27 и 29 настроены на нулевую комбинацию.

Разрешающий сигнал с дешифратора

28 вызывает формирование импульса на выходе того элемента И 30 или 32, который соединен через дешифратор 27 (29) со счетчиком 24 (26), находящимся в этот момент в нулевом состоянии, а это тот счетчик из 24 или 26, который соответствует синфазному с контрольным сигналом каналу приемной части устройства. В нашем примере, когда с контрольным сигналом синфазна последовательность, поступающая на вход детектора 3 ошибок, после окончания блока информации, в течение которого произошел сбой синхронизации, содержимое всех счетчиков 7 — 9 становится больше порогово. го кода и на все счетчики 24 — 26 поступает сигнал на увеличение их содержимого на единицу, После блоков информации опрашиваются элементы И 30 и 32. Так как после сбоя синхронизации сигнал детектора 3 стал синфазным с контрольным, количество ошибок становится малым и сигналами

"Меньше" с выхода блока 19 сравнения счетчик 24 устанавливается в нулевое состояние, Счетчик 26 в это же время — в ненулевом состоянии, поскольку рассинфаэирование третьего канала относительно контрольного сигнала составляет два такта. Сигнал с выхода первого элемента И 30 через элемент ИЛИ 22 анализатора

50 m, пооогового кода и модуля счета счетчика

25 анализатора 13. При правильном выборе этих значений пакет ошибок может вызвать срабатывание блока 20 сравнения, но при анализе последующих блоков информации, 55 не выйдя из синхронизма, первый канал будет формировать сигналы на сброс счетчика

25 анализатора 13 и срабатывания элементов устройства, ответственных за формирование сигнала подстройки не произойдет, начиная с дешифратора 28, 10

13 поступает на вход блока 15 синхронизации, осугцествляя его подстройку в направлении. противоположном направлению сбоя синхронизации, то есть в IIaIIIe примере — вынуждает его выдать добавочный импульс на вход генератора 14 эталонного сигнала и тем самым сдвинуть вперед em фазу и ликвидировать рассогласование. После этого вновь синфазным с конгрольным сигналом становится сигнал, поступак> ций на детектор 2 ошибок и устройство возвращается в исходное синфазное состояние.

Аналогично происходит отработка расфазирования в случае опере;кения эталонного сигнала в сравнении с контрольным при сбое тактовой синхронизации, отличие заключается лишь в том, что в этом случае третий канал (с детектором 4 и сопряженными с ним цепями и блоками) и импульс выдается для сдвига генератора 14 на отста ва н и е.

В случае, если произошел сбой синхронизации за счет временного пропадания си нала (это случается гораздо реже, чем сдвиг фазы сигналов на один такт) все каналы устройства являются рассинфазировлнными после формирования сигнала с дешифратора 28. При этом по сигналу с дешифратора 28 разрешается работа элемента И 31, на вь:ходе которого появляется сигнал лишь в том случае, когда и второй и третий каналы несфазированы с контрольным сигналом (нет сигналов с элеMåíтоf3 И

30 и 32, есть сигналы с элементов НЕ 33 и

34. По сигналу с элемента И 31 через в орой элемент ИЛИ 22 анализатора 13 в данном случае (I oI да нужное оптимальное направление подстройки неизвестно) формируется сигнал на подстройку через блок 15 синхронизации генератора 14 эталонного сигнала в одном. постоянном для .устройства, направлении.

При сбое синхронизации, вызванном временным (с произвольным временем) пропаданием сигнала, предлагаемое устройство работает аналогично, устройствупрототипу.

Различение сбоя синхронизации и пакета ошибок достигается выбором интервала

1674394

50

При выявлении сбоя синхронизации (независимо от причины) сигналом с анализатора 13 через элемент ИЛИ 11 в накопителе 10 стираются блоки, соответствующие интервалу, в котором обнаружен сбой синхронизации (К+1 блоков, где единица добавляется за счет блока, в котором произошел сбой синхронизации). Одновременно сигналом с элемента ИЛИ 11 из содержимого счетчика 5 вычитается количество импульсов, равное К+1 при фиксации им числа блоков данных (или m(K+1) — при фиксации им общего числа переданных импульсов), Сигналы со счетчиков б и 5 поступают в решающий блок 17, в котором определяется вероятность ошибки как отношения количества ошибок, зафиксированного счетчиком

6, к Общему числу переданных импульсов, зафиксированному счетчиком 5, Блок 18 индикации отображает значение коэффициента Ошибок.

Следует отметить, что при срабатывании в случае сбоя синхронизации дешифратора 28 сигналом с него сбрасывается в исходное состояние через элемент ИЛИ 23 счетчик 25 анализатора 13, с помощью чего устройства готово после этого момента к дальнейшей подстройке по тому же принципу (если в этот текущий момент синфазность на достигнута).

Кроме того, элемент ИЛИ 22 анализатора 13 мо>кет вторым входом быть присоединен не к элементу И 30, а к элементу И 32, при этом изменяется направление подстройки устройства в случае сбоя синхронизации по причине временного пропадания сигнала (то есть когда сдвиг происходит не на смежную посылку, а на непредсказуемое число тактов и в непредсказуемом направлении), При сбое синхронизации за счет временного пропадания сигнала, если очередная подстройка не приводит к синхронизму, осуществляется Очередное стирание К+1 блоков данных и подстройка продолжается по вышеописанному алгоритму.

Формула изобретения 1. Устройство для измерения коэффициента ошибок в цифрсвых трактах передачи информации, содержащее первый счетчик, последовательно соединенные генератор контрольного сигнала, детектор ошибок, блок выбора интервалов, накопитель, второй счетчик, решающий блок и блок индикации и последовательно соединенные анализатор структуры сигнала несовпадений, блок синхронизации и генератор этала гного сигнала, выход первого счетчика подключен к другому входу решающего блока, о тл и ч а ю щ е е с я тем, что, с целью уменьшения времени измерения за счет уменьшения времени установки синхронизации, в него введены элемент ИЛИ, третий счетчик, последовательно соединенные второй детектор ошибок и четвертый счетчик, выход которого подключен к первому входу анализатора структуры сигнала несовпадений, и последовательно соединенные элемент задержки, третий детектор ошибок и пятый счетчик, выход которого подключен к второму входу анализатора структуры сигнала, первый выход которого подключен к первому входу элемента ИЛИ, а второй выход подключен к второму входу элемента

ИЛИ и к другому входу блока синхронизации, третий вход соединен с выходом третьего счетчика, а четвертый вход соединен с выходом блока выбора интервала, с первым входом первого счетчика и с объединенными вторыми входами третьего, четвертого и пятого счетчиков, первый вход первого детектора ошибок объединен с первыми входами второго и третьего детекторов ошибок, выход первого детектора ошибок подключен к первому входу третьего счетчика и к второму входу накопителя, третий вход которого соединен с выходом элемента ИЛИ и с вторым входом первого счетчика, выход генератора эталонного сигнала подключен к второму входу второго детектора ошибок и к входу элемента задержки, второй выход которого подключен к второму входу первого детектора ошибок.

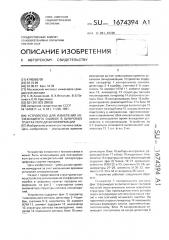

2. Устройство по п.1, о т л и ч а ю щ е ес я тем, что анализатор структуры сигнала несовпадений содержит последовательно соединенные генератор чисел, первый блок сравнения, первый счетчик, первый дешифратор, первый элемент И, первый элемент

НЕ, второй элемент И и первый элемент

ИЛИ. другой вход которого соединен с выходом первого элемен га И, последовательно соединенные второй блок, сравнения, второй элемент ИЛИ, второй счетчик, второй дешифратор, трет лй элемент И и второй элемент НЕ, выход которого подключен к второму входу второго элемента И, третий вход которого соединен с выходом второго дешифратора, последовательно соединенные третий блок сравнения, третий счетчик и третий дешифратор, выход которого подключен к другому входу третьего элемента

И, выход второго блока сравнения подключен к другому входу второго счетчика, выход второго дешифратора подключен к другим входам первого элемента И и второго элемента ИЛИ, выход генератора чисел подключен к первым входам второго и третьего блоков сравнения, первым, вторым и третьим входами анализатора структуры сигнала

1674394

Токпюбпя юсгпалю

Рог. 1 несовпадений являются соответственно вторые входы первого, третьего и второго блоков сравнения, первым выходом является выход первого элемента И, а вторым выходом — выход третьего элемента И.