Цифровой анализатор частотных характеристик четырехполюсников

Иллюстрации

Показать всеРеферат

Изобретение может быть применено для исследования частотных характеристик линейных четырехполюсников в диапазоне инфранизких частот. Цель изобретения - повышение быстродействия - достигается введением преобразователя 7 кода, накапливающего сумматора 8, синусного и косинусного преобразователей 9 и 10 кода, счетчика 11 адреса, блока 12 синхронизации и управления и селектора-мультиплексора 6. Сущность изобретения состоит в уменьшении времени измерения за счет использования для анализа не всего периода анализируемой частоты, а только его части. При работе анализатора тестовый сигнал формируется с помощью генератора 1 управляемой частоты и преобразователя 2 код - аналог. Выходной сигнал с выхода измеряемого четырехполюсника 3 преобразуется аналого-цифровым преобразователем 4 и запоминается в запоминающем блоке 5. 4 ил.

СОЮЗ СОВЕТСКИХ

СОЦИ4Л ИСТИ Ч Е С КИХ

РЕСПУБЛИК (s»s G 01 R 27/28

ГОСУД4РСТВЕННЫИ KOMVI7ET

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР .". .ьа

ОПИСАНИЕ ИЗОБРЕТЕНИЯ - - и».","","

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

2 (21) 4689321/21 (22) 05.05.89 (46) 07.09.91. Бюл. (Ф 33 (72) М.Я.Минц, В.Н.Чинков и А.M.Âîðîíêèí (53) 621.317,75 (088.8) (56) АвторСкое свидетельство СССР

М 1308941, кл. G 01 R 27/28, 1987.

Авторское свидетельство СССР

М 538307, кл, G 01 R 27/28, 1976. (54) ЦИФРОВОЙ АНАЛИЗАТОР ЧАСТОТНЫХ ХАРАКТЕРИСТИК ЧЕТЫРЕХПОЛЮСНИКОВ (57) Изобретение может быть применено для исследования частотных характеристик линейных четырехполюсников в диапазоне инфранизких частот, Цель изобретения— повышение быстродействия — достигается

„„БЫ„, 1675798 А1 введением преобразователя 7 кода, накапливающего сумматора 8, синусного и косинуснога преобразователей 9 и 10 кода, счетчика 11 адреса, блока 12 синхронизации и управления и селектора-мультиплексора

6. Сущность изобретения состоит в уменьшении времени измерения за счет использования для анализа не всего периода анализируемой частоты, а только его части.

При работе анализатора тестовый сигнал . формируется с помощью генератора 1 управляемой частоты и преобразователя 2 код — аналог. Выходной сигнал с выхода измеряемого.четырехполюсника 3 преобразуется аналого-цифровым преобразователем 4 и запоминается в запоминающем блоке 5. 4 ил.

1675798

10

Изобретение относится к цифровой измерительной технике и может быть применено для исследования частотных характеристик линейных четырехполюсников в диапазоне инфрэнизких частот.

Целью изобретения является повышение быстродействия путем уменьшения длительности выборки выходного сигнала исследуемого четырехполюсниха, используемой для анализа.

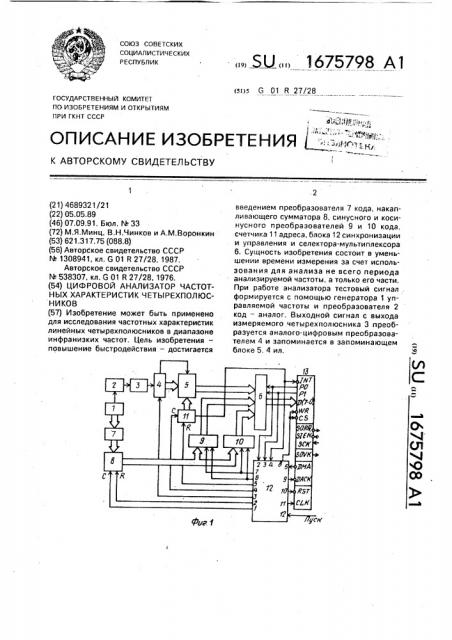

На фиг. 1 представлена структурная схема цифрового анализатора; на фиг. 2—, временные диаграммы, поясняющие работу устройства в режиме записи значений

cos(k а) в вычислитель; на фиг. 3 — функциональная схема блока синхронизации и управления; на фиг. 4 — временные диаграммы, поясняющие работу блока синхронизации и управления.

Цифровой анализатор частотных характеристик содержит последовательно соеди ненные генератор 1 управляемой частоты, преобразователь 2 код — аналог, исследуемый четырехполюсник 3, преобразователь 4 аналог — код, запоминающий блок 5 и селектор-мультиплексор 6, а также преобразователь 7 кода, накапливающий сумматор 8, синусный 9 и косинусный 10 преобразователи кода, счетчик 11 ацреса, блок 12 синхронизации и управления и вычислитель.33, при этом цифровой выход генератора 1 управляемой частоты через последовательно соединенные преобразователь 7 кода и накапливающий сумматор 8 подключен к объ единенным информационным входам синусного 9 и косинусного 10 преобразова: телей кода, выходы которых соответственно подключены к второму и третьему информационным входам селектора-мультиплексора 6, адресный вход запоминающего блока

5 соединен с выходом счетчика 11 адреса, а выход сигнала "Конец преобразования" преобразователя 4 аналог — код связан с входом разрешения записи запоминающего блока 5, первый вход блока 12 является входом запуска анализатора, его второй вход объединен с первым управляющим входом селектора-мультиплексора 6 и сое динен с выходом разряда регистра состояний вычислителя 13, третий вход этого блока объединен с вторым управляющим входом селектора-мультиплексора 6 и подключен к выходу разряда Р1 регистра состояний вычислителя 13, четвертый вход объединен с входом запроса на прерывание . вычислителя 13 и соединен с выходом старшего разряда счетчика 11 адреса, а пятый вход подключен к выходу сигнала запроса на прямой доступ к памяти 13МА вычислите20

50 ля 13, причем первый выход блока 12 соединен с синхровходом сумматора 8, второй выход подключен к входу установки в нуль сумматора 8, третий выход связан с входом запуска преобразователя 4, четвертый и пятый выходы соответственно соединены со счетным входом и входом установки в нуль счетчика 11, шестой выход подключен к объединенным первым управляющим входам синусного 9 и косинусного 10 преобразователей кода, а седьмой выход — к объединенным вторым управляющим входам этих преобразователей, восьмой выход соединен с входом разрешения записи и с входом выбора кристалла вычислителя 13, девятый, десятый и одиннадцатый выходы связаны с входом подтверждения прямого доступа к памяти ВАСК, входом начальной установки и тактовым входом вычислителя 13, Блок 12 синхронизации и управления (БУС) (фиг. 3), состоит из последовательно. включенных кварцевого генератора 14, первого элемента 2И 15, первого делителя 16 частоты, второго делителя 17 частоты, второго элемента 2И 18 и четвертого элемента

ИЛИ 19, при этом выход кварцевого генератора 1 является также одиннадцатым выходом ЬУС 12, выход первого делителя 16 частоты, кроме входа второго делителя 17 частоты, связан с входом распределителя 20 импульсов, выходы которого являются первым, шестым, седьмым и восьмым выходами

БУС 12, первый вход которого подключен к

S-входу первого RS-триггера 21, второму входу второго элемента ИЛИ 22, первому входу третьего элемента ИЛ И 23 и десятому выходу БУС 12, причем выход второго элемента ИЛИ 22 является пятым выходом БУС

12, выход третьего элемента ИЛИ 23 является вторым выходом БУС 12, а прямой выход первого RS-триггера 21 подключен к вторым входам первого элемента ИЛИ 24 и второго элемента 2И 18, при этом первый вход первого элемента ИЛИ 24 обьединен с входом первого формирователя 25 импульсов и соединен с выходом дешифратора 26, входы которого являются вторым и третьим входами БУС 12, четвертый вход которого подключен к R-входу первого RS-триггера 21 и к первому входу второго элемента ИЛИ 22, а второй вход третьего элемента ИЛИ 23 соединен с выходом первого формирователя 25 импульсов, пятый вход БУС 12 связан с S-входом второго RS-триггера 27, прямой выход которого через второй формирователь 28 импульсов соединен с объединен н ыми между собой первым входом четвертого элемента ИЛИ 19 и входом элемента 29 задержки, при этом выход элемента 29 задержки является девятым выходом БУС 12 и а

1675798 подключен к R-входу второго RS-триггера 27.

Принцип работы цифрового анализатора основан на алгоритме вычисления квадратурных составляющих Ах и Ау, амплитуды анализируемой гармоники Амакс и постоянной составляющей Ао по формулам

Aõ

Ис-0С

Сг Сг

Ау =

s, S где

<с г Тоср

2Nm

Работу остальной части устройства можно разбить на несколько режимов.

В первом режиме по команде "Пуск", поступающей на первый вход БУС 12, происходит следующее: формирование импульсов "Сброс" на втором, пятом и десятом выходах БУС 12, которые поступают соответственно на входы установки в нуль накапливающего сумматора 8, счетчика 11 и на вход начальной установки вычислителя

13; на третьем и четвертом выходах БУС 12 начинают формироваться синхронные последовательности импульсов, которые поступают соответственно на вход запуска

35 преобразователя 4 аналог — код и на счетный вход счетчика 11 адреса; на первом, шестом — восьмом выходах БУС 12 начинают формироваться последовательности синхроимпульсов, которые подаются соот 40 ветственно на синхровход накапливающего сумматора 8 (последовательность С, фиг. 2), на первые управляющие входы синусного 9 и косинусного 10 преобразователей кода (последовательность RDN), на вторые управляющие входы этих же преобразователей (последовательность RDM) и на обьединенные входы разрешения записи

WR и выбора кристалла CS вычислителя 13 (последовательность В/В и СЯ), 50 При поступлении импульса "Сброс" на вход начальной установки вычислителя 13 счетчик команд вычислителя 13 устанавливается в исходное состояние, на выходе раэряда PO его регистра состояний

55 устанавливается уровень логического нуля, а на выходе P1 — уровень логической единицы. При этом селектор-мультиплексор 6 подключает к шине данных вычислителя 13 выходную шину косинусного преобразова-г 1

$2 з пг

2 N+1

Амакс = Ax+Ay . Ао =U -CA

2 2.

U —, g U(kArg): — N

U,=, g U (КЛ1д)СОВМа;

09 U (k Atg) 81П 1(Я !

С вЂ”, cos ka; (1) С вЂ” „, cos ka;

-г 1 г

2 И+1 -д

При этом длительность выборки выходного сигнала исследуемого четырехполюсника, необходимая для реализации данного алгоритма, может быть существенно меньше длительности периода этого сигнала, т.е.

Tocp < Ть Требуемая точность измерений достигается за счет выбора достаточного большого числа (2N + 1) дискретных отсчетов сигнала U(k htg), входящих в данную выборку, которое может быть определено из соотношения 2N = Tocp/Л ту, где Ь tg— интервал дискретизации.

Анализатор частотных характеристик четырехполюсников работает следующим образом.

Генератор 1 управляемой частоты формирует последовательность импульсов с частотой следования ауг, которые поступают на вход преобразователя 2 код — аналог, под действием которых на его выходе формируется стимулирующий периодический сигнал, имеющий частоту й4 =Nуi/m и представляющий собой ступенчатую аппроксимацию синусоидального сигнала (m — число интервалов дискретизации, приходящихся

5 на один период стимулирующего сигнала, определяемое разрядностью преобразователя).

Стимулирующий сигнал поступает на вход исследуемого четырехполюсника 3, вы10 ходной сигнал которого подается на вход преобразователя 4 аналог — код. Кроме того, с цифрового выхода генератора 1 управляемой частоты на вход преобразователя 7 поступает код частоты шоу,, который.

15 преобразует его в код аргумента а по закону

1675798

2И+1

При этом С вычисляется по алгоритму

lib

С вЂ” «»kц+

k ==1 а С по алгоритму

Г сов kQ+ 1

k =1

"2 1

2 И+1

В ходе вычисления регистр АА вычислителя 13 используется в качестве аккумулятотеля 10 кода, Вычислитель 13 устанавливается в режим двухбайтового обмена (в поле

DRS его регистра состояний записывается нуль). Под действием импульсных сигналов

RDN и ADM, формируемых на седьмом и шестом выходах БУС 12 соответственно, происходит последовательный опрос старшего и младшего байтов 16-разрядногс кода

cos(k а), формируемого на выходе косинусного преобразователя 10 кода в соответст. вии с кодом ka, который поступает на его вход с еыхода накапливающего сумматора 8.

Работа накапливающего сумматора заключается в следующем. С выхода преобразователя 7 кода на вход накапливающего сумматора 8 поступает код аргумента а„

Под действием синхроимпульсов, формируемых на первом выходе БУС 12, на выходе накапливающего сумматора 8 последовательно формируются коды k а, где k = 0,1,..., N, Под действием импульсных сигналов

WR и CS, поступающих на соответствующие входы вычислителя 13 с 8-го выхода БУС 12, происходит запись байтов N(cosk cz) и

M(cosk а) в регистр DR вычислителя 13, mкуда они затем переписываются в его оперативную память. После окончания цикла записи, т.е. при k =- N, вычислитель 13 устанавливает на выходах РО и Р1 уровни логического нуля, закрывая тем самым селектор-мультиплексор 6, В поле DRS регистра состояний вычислителя 13 записывается единица, отменяющая режим двухбайтового обмена, и вычислитель 13 приступает к последовательному выполнению подпрограмм вычисления ра, регистр А — для временного хранения кода С, а регистр RT — для временного хра,нения кода С .

Затем вычисляется величина С вЂ” С2, 5 код которой записывается в регистр RT вместо кода С . После чего вычислитель переходит в режим ожидания

Параллельно с выполнением первого режима работы в устройстве выполняется второй режим — режим записи кодов мгновенных значений выходного сигнала исследуемого четырехполюсника в

55 запоминающий блок 5.

Под действием импульсов, поступающих с третьего выхода БУС 12 на вход запуска преобразователя 4, нэ его выходе последователЬно формируются коды

U(kAlg). Синхронно с импульсами senYGKB нэ счетный вход счетчика 11 адреса поступают импульсы, под действием которых нэ его выходе последовательно формируются коды адоеса ячеек памяти запоминающего блока 5 от 1 до(2Й+ 1)-й. Период следования этих импульсов соответствует длительности интервала преобразования преобразователя 4 аналог — код, Под действием импульсов

"Конец преобразования", поступающих с соответствующего выхода преобразователя

4 на вход разрешения записи WR запоминающего блока 5, происходит запись кодов

U(khtg) в ячейки памяти запоминающего блока по адресам, определяемым состоянием счетчика 11 адреса, Таким образом, в запоминающий блок записано 2N + 1 кодов мгновенных значений U(k Ьtg), После прихода на счетный вход счетчика 11 (2N+ 2)-ro импульса, на выходе его старшего разряда появляется импульс переполнения, который поступает нэ вход запроса на прерывание

INT вычислителя 13 и на четвертый вход БУС

12. При этом на пятом выходе БУС 12 формируется импульс, поступающий на вход установки в нуль счетчика 11, с приходом которого последний устанавливается в состояние "Нуль", а на третьем и четвертом выходах БУС 12 формирование последовательности импульсов прекращается. На выходах разрядов регистра состояний PO и Р1 вычислителя 13 устанавливаются уровни логической единицы, под действием которых селектор-мультиплексор 6 подключает шину данных вычислителя 13 к выходу запоминающего блока 5. После чеГо устройство переходит в третий режим работы, Необходимо отметить, что длительность второго режима работы больше длительности первого режима, и таким образом второй.режим не влияет на выполнение первого режима. Обеспечивается зто тем, 1675798

10 что частота опроса косинусного преобразователя 10 может равняться 1 — 2 МГц, а частота следования импульсов запуска преобразователя 4 составляет 0,1 — 0,3 МГц.

Третий режим работы устройства за- 5 ключается в следующем.

При поступлении импульса переполнения на вход INT вычислителя 13 последний переходит иэ режима ожидания в режим обработки первой подпрограммы прерыва- 10 ния. При этом, как указывалось, вначале устанавливаются уровни логической единицы на выходах Р0 и Р1, после чего на выходе

DMA формируется сигнал запроса на прямой доступ к памяти, поступающий на пя- 15 тый вход БУС-12.

По этому сигналу БУС 12 на своем четвертом выходе формирует импульс, который поступает на счетный вхоД счетчика 11 адреса, переводя его тем самым из состояния 20

"Нуль" в состояние "Один". После этого на девятом выходе БУС 12 формируется сигнал разрешения прямого доступа к памяти, поступающий на вход РАСК вычислителя 13.

По этому сигналу код 0(1Л tg) с выхода за- 25 поминающего блока 5 записывается в регистр DR вычислителя 13. Затем этот код умножается на код cosN а, хранящийся в (N+ 1)-й ячейке оперативной памяти вычислителя 13, а результат 0(1 htg) cosN а запи-- 30 сывается в (2N + 1)-ю ячейку оперативной памяти. После этого на выходе DMA вычислителя 13 вновь формируется сигнал запроса на прямой доступ к памяти.

Описанные действия полностью новто- 35 ряюстя, но при этом опрашивается уже ячейка запоминающего устройства с адресом "Два", а в ячейку с номером 2N оперативной памяти вычислителя 13 записан код U(2 Лщ)соз((й — 1) а). Так продолжа- 40 ется до тех пор пока в ячейку оперативной памяти с номером N+ 1 не записан код U((N

+ 1) Жц)соз(0). В ячейку оперативной памяти с номером N записан код U f(N+ 2) Ь|ц)соз(1

a}, в ячейку N — 1 записан код Uf(N+ 3)x 45 ханц)соз2а итак далее до тех пор, пока в ячейку с номером 1 не записан код

U((2N+ 1) ЛtgJcos(N а)., При поступлении (2N+ 2)-го запроса на прямой доступ к памяти происходит пере- 50 полнение счетчика 11 адреса. Импульс переполнения с выхода старшего разряда счетчика 11 адреса, как и в предыдущем режиме, поступает на вход INT вычислителя

13 и на четвертый вход БУС 12. При этом на 55 пятом выходе БУС 12 формируется импульс

"Сброс", по которому счетчик 11 адреса ócтанавливается в состояние "Нуль", а вычислитель 13 приступает к обработке второй подпрограммы прерывания. В соответствии с этой подпрограммой вычисляется величина на

0 -1/(2N+ 1) 0(Мц) cosk а.

Код 0«записывается в ячейку оперативной памяти вычислителя 13 по адресу 2N+ 2.

После этого вычислитель 13 вновь начинает опрос запоминающего блока 5 путем формирования на выходе DMA сигнала запроса на прямой доступ к памяти. При этом работа анализатора не отличается от его работы в режиме предыдущего опроса запоминающего блока 5, но коды 0(keg) из регистра DR вычислителя 13 уже умножаются не íà cos(k а), а на константу 1/(2N + 1), а результаты последовательно суммируются в ALU, для чего используется регистр АА вычислителя 13.

Таким образом, к моменту появления на входе INT импульса переполнения счетчика

11 адреса в регистре АА вычислителя 13 записана величина

1 k=2N+1

0= „+„«X и (k«g) k=1

После поступления на вход INT импульса переполнения счетчика 11 адреса вычислитель 13 переходит на выполнение третьей подпрограммы прерывания. К этому моменту в вычислителе 13 имеются код 0- в регистре АА, код С вЂ” в регистре АВ, код С2-С— в регистре RT и код Uc — в ячейке (2N + 2)-й оперативной памяти.

В соответствии с третьей подпрограммой код 0 переписывается из регистра АА в первую ячейку оперативной памяти, после чего код 0О из ячейки (2N + 2)-й переписывается в регистр АА, коды 0 и С перемножаются в матричном перемножителе МОЕ, а код результата вычитается из кода 0<, при этом код разности заносится в регистр АА.

Затем производится деление кода, записанного в регистре АА, на код С2-С2, хранящийся в регистре RT. В результате этих вычислений в регистре АА записан

u,-Gc код A> —, который затем переС вЂ” С2 писывается в регистр RT вместо кода С2-С2.

После этого в регистр АА записывается код 0, хранящийся в первой ячейке оперативной памяти, коды С и А> перемножаются в матричном перемножителе, а результат вычитается из кода О. При этом в регистре

1675798

АА записан код Ао U-CÀ,<, который затем переписывается в регистр последовательного вывода SOUT, На этом выполнение третьей подпрограммы прерывания заканчивается и начина- 5 ется четвертый режим работы, Четвертый режим работы начинается с того, что вычислитель 13 устанавливает на выходе PO уровень логической единицы, а на выходе Р1 уровень логического нуля, При 1С этом селектор-мультиплексор 6 подключает к шине данных вычислитегя 13 выходную шину синусного преобразователя 9, а на втором выходе БУС 12 формируется импульс, под действием которого происходит 15 обнуление накапливающего сумматора 8, Одновременно с этим в поле DRS регистра состояний вычислителя !3 записывается нуль, тем самым устанавливается режим двухбайтового обмена. 5O

После этого под действием импульсных сигналов RDM и RDN, формируемых на meстом и седьмом выходах БУС 12 происходит последовательный опрос старшего и младmего байтов 16-разрядного кода (первый ре- 25 жим), но уже не cos(kfx), а sin(4z ). i оды й(з!и!с а) и M(sinkc) с помощью импульсных сигналов WR u CS записываются в регистре

DR вычислителя 13„откуда они переписываются в его оперативную память. 30

После окончания цикла записи, т.е, при

k = N, вычислитель 13 устанавливает на выходах PO и Р1 уровни логического нуля, закрывая селектор-мультиплексор 6, а в поле

DRS регистра состояний записывается еди- 35 ница, отменяющая режим двухбайтового обмена, Вычислитель переходит на выполнение подпрограммы вычисления

Ж в!и !с а

2 И+1

При этом в качестве аккумулятора используется регистр АА, а окончательный ре- !„ зультат записывается В регистр АВ для временного хранения.

По завершению этой программы вычислитель 13 устанавливает на Выходах РО и Р1 уровни логической единицы, под действием которых селектор-мультиплексор 6 подключает шину данных вычислителя к выходу запоминающего блока 5 и начинается пятый режим работы, 51

Пятый режим работы аналогичен третьему и заключается в том, что вычислитель 13 с помощью сигналов запроса на прямой доступ к памяти DMA производит опрос ячеек памяти запоминающего блока 5. При этом в ячейку оперативной памяти с номером 2N 4 1 вычислителя записан код

U(1Atg)(— sin(N а)), в ячейку 2N — U(2Atg)(sin((— 1) а )) и т.д, В ячейку с номером N + 1 записан код

U((N+ 1) Лщз!п(0)), в ячейку и — u((N — 2)

big)sin а, в ячейку N — 1 — U((N + 3) х

xAtg)sin(а ) и так далее, пока в ячейку с первым номером 1 не будет записан код

U((2N+ 1) Л tg)sin(И а), После поступления

2N + 2 запроса He npAMoM Достffn K памяти происходит переполнение счетчика 11.

Импульс переполнения с выхода старmего разряда счетчика 11 поступает на вход

INT вычислителя 13 и на четвертый вход БУС

12. При этом на пятом выходе БУС 12 формируется импульс "Сброс", по которому счетчик 11 устанавливается в остояние

"Нуль", а Вычислитель 13 переходит на режим обработки четвертой подпрограммы прерывания, в соответствии с которой вычисляется величина

Us = U(k Atg)sin(ka ).

2И+1

Код Us записывается в регистр АА и затем делится на код 3, хранящийся в регистре АВ. В результате деления получается величина А = Us/e, код которой записывается в регистре АВ, После этого вычисляется величина

Амакс = Ах + Ay, КОД котОРОЙ записыВает / 2 2 ся в регистр АА.

Таким образом, в результате всех вычислений в регистрах вычислителя имеются коды следующих величин; код Ах — в регистре RT, код Ау — в регистре АВ, код Амакс — в регистре АА и код А, — в регистре SOUT.

Шестой режим — режим последовательного вывода результатов вычислений. Он начинается с момента выставления сигнала запроса на последовательный вывод информации, который формируется на выходе

SORQ вычислителя 13 после завершения обработки четвертой подпрограммы прерывания.

В ответ на этот сигнал потребитель информации формирует сигнал разрешения последовательной выдачи информации, поступающий на вход SOEN вычислителя 13 и под действием синхроимпульсов, которые подаются от потребителя информации на вход SCK вычислителя 13, производится поСЛЕДОВатЕЛЬНВЯ ВЫДВЧа КОДОВ Ао, Аиакс, Ах И

Ау с выхода ЯО вычислителя 13 потребителю.

По окончании цикла выдачи — приема потребитель информации перестраивает re13

1675798

14 счетчика 11 адреса в состояние "Нуль" и начальная установка счетчика команд вычислителя 13, При поступлении на четвертый вход

БУС 12 импульса переполнения с выхода старшего разряда счетчика 11 адреса первый RS-триггер 21 устанавливается в состояние "Нуль", что приводит к закрытию первого 15 и второго 18 элементов 2И. При этом формирование сигналов на восьмом— шестом, первом, третьем и четвертом выходах БУС 12 прекращается. Кроме того, этот импульс через второй элемент ИЛИ 22 поступает на пятый выход БУС 12.

В третьем и пятом режимах работы устройства БУС 12 обслуживает запросы на пря-. мой доступ к памяти, поступающие на его пятый вход с выхода DMA вычислителя 13.

В четвертом режиме работы БУС 12 раотает следующим образом, При поступлении на второй вход БУС 12 ровня логической единицы с выхода PO выислителя 13 и уровня логического нуля на ретий вход БУС 12 с выхода Р1 на выходе ешифратора 26 устанавливается уровень огической единицы, по переднему фронту оторой срабатывает первый формироваель 25 импульсов, с выхода которого через ретий элемент ИЛИ 23 на второй выход

УС 12 поступает импульс, по которому наапливающий сумматор 8 устанавливается состояние "Нуль", Кроме того, уровень лоической единицы с выхода дешифратора 26 ерез первый элемент ИЛИ 24 поступает на торой вход первого элемента 2И 15, что риводит к его открытию. При этом на восьом — шестом и первом выходах БУС 12 новь начинают формироваться соответстующие последовательности импульсов.

По окончании четвертого режима кодоая комбинация на втором и третьем входах

УС 12 из 01 изменяется на 11. При этом на

ыходе дешифратора 26 устанавливается ровень логического нуля, что приводит к крытию первого элемента 2И 15 и соотетственно, к прекращению процесса форирования последовательностей мпульсов на восьмом — шестом и первом

ыходах БУС 12.

При поступлении на первый вход БУС

12 импульса "Пуск" первый RS-триггер 21 15 устанавливается в состояние "Единица", уровнем которой открывается второй элемент 2И 18 и через первый элемент ИЛИ 24 первый элемент 2И 15. Последовательность тактовых импульсов через открытый первый 20 б элемент 2И 15 начинает поступать на вход первого делителя 16 частоты, выходкой сиг- у нал которого подается на вход распредели- ч теля 20 импульсов и на вход второго т делителя 17 частоты. Соотношение частот 25 д выбрано таким образом, что частота сигнала л на выходе кварцевого генератора 14 равна к тактовой частоте вычислителя 13 (по- т рядка 5 МГц), частота сигнала на выходе т первого. делителя 16 частоты соответствует 30 Б удвоенной частоте опроса синусного 9 и ко- к синусного 10 преобразователей кода знали- в затора (порядка 2 МГц), а частота сигнала íà r выходе второго делителя 17 частоты равна ч частоте преобразования преобразователя 4 35 в аналог — код анализатора (порядка 0,1 — 0,3 и

М Гц), м

Выходной сигнал второго делителя 17 в частоты через открытый второй элемент 2И в

18 поступает на третий выход БУС12 ичереэ 40 четвертый элемент ИЛИ 18 — на четвертый в выход БУС 12. Б

Временные диаграммы перечисленных в сигналов показаны на фиг. 4: импульс у

"Пуск" (а), сигнал на выходе первого RS- 45 sa триггера 21 (б), сигнал на восьмом выходе а

БУС 12 (в), сигнал на седьмом выходе БУС и

12 (г), сигнал на шестом выходе БУС 12 (д), и сигнал на первом выходе БУС 12 (е), сигнал в на третьем выходе БУС 12 (ж) и сигнал на 50 четвертом выходе БУС 12 (з).

Кроме того, импульс "Пуск" с первого входа БУС 12 поступает через второй элемент ИЛИ 22 на пятый выход БУС 12, через третий элемент ИЛИ 23 — на второй выход 55

БУС 12 и на десятый выход БУС 12 непосредственно, Поддействием этих импульсов происходит сброс накапливающего сумматора 8 и

Цифровой анализатор частотных характеристик четырехполюсников, содержащий последовател ьно соединен н ые генератор управляемой частоты, преобразователь код

-аналог, клеммы для подключения исследуемого четырехполюсника и преобразователь аналог — код, а также запоминающий нератор 1 управляемой частоты на новую частоту вуг и формирует импульс "Пуск", который поступает на первый вход БУС 12.

После этого работа устройства повторяется на другой частоте анализа. 5

Работа БУС 12 заключается в следующем, Кварцевый генератор 14 формирует на своем выходе последовательность импульсов TBKTDBoA частоты, которая поступает на первый вход первого элемента 2И 15 и через 10

11-й выход БУС 12 на вход CLK вычислителя

13, являющийся его тактовым входом.

Формула изобретения

1675798 блок и вычислитель, отличающийся тем, что, с целью уменьшения времени измерения, в него введены преобразователь кода, накапливающий сумматор, счетчик адреса, селектор-мультиплексор, блок синхронизации и управления, синусный и косинусный преобразователи кода, при

Этом информационные входы синусного и косинусного преобразователей кода объеДинены между собой и соединены с выходом накапливающего сумматора, информационный вход которого через преобразователь кода подключен к цифровому выходу генератора управляемой частоты„ цифрой выход преобразователя аналог— код через последовательно соединенные

Запоминающий блок и селектор-мультиПлексор связан с входом шины данных вычислителя, причем второй и третий

Информационные входы селектора-мульти тлексора соответственно подключены к выходам синусного и косинусного преобразователей кода, адресный вход запоминающего блока соединен с выходом

Счетчика адреса, а выход "Конец преобразования" преобразователя аналог — код подключен к входу разрешения записи запоминающего блока, первый вход блока

Синхронизации и управления является входом запуска анализатора, а его второй вход соединен с первым управляющим входом селектора-мультиплексора и с выходом регистра соотояний вычислителя, третий вход блока синхронизации и управления соединен с вторым управляющим входом селекто5 ра-мультиплексора и подключен к выходу разряда регистра состояний вычислителя, четвертый вход объединен с входом запроса на прерывания вычислителя и соединен с выходом старшего разряда счетчика адреса, 10 а пятый вход подключен к выходу сигнала запроса на прямой доступ к памяти вычислителя, при этом первый выход блока синхронизации и управления соединен с синхровходом накапливающего сумматора, 15 второй выход подключен к входу установки в "0" накапливающего сумматора, третий выход связан с входом запуска преобразователя аналог-код, четвертый и пятый выходы соответственно соединены с счетным входом и

20 входом установки в "0" счетчика адреса, шестой выход подключен к объединенным первым управляющим входам синусного и косинусного преобразователей кода, а седьмой выход — к объединенным вторым управля25 ющим входам этих преобразователей, восьмой выход соединен с входом разрешения записи и с входом выбора кристалла вычислителя, девятый, десятый и одиннадцатый выходы связаны с входом подтверждения прямогодоступа

:30 к памяти, входом начальной установки и тактовым входом вычислителя соответственно.

1675798

Составитель Н.Михалева

Техред М.Моргентал Корректор В.Гирняк

Редактор Н.Бобкова

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

Заказ 2999 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5