Устройство для адресации

Иллюстрации

Показать всеРеферат

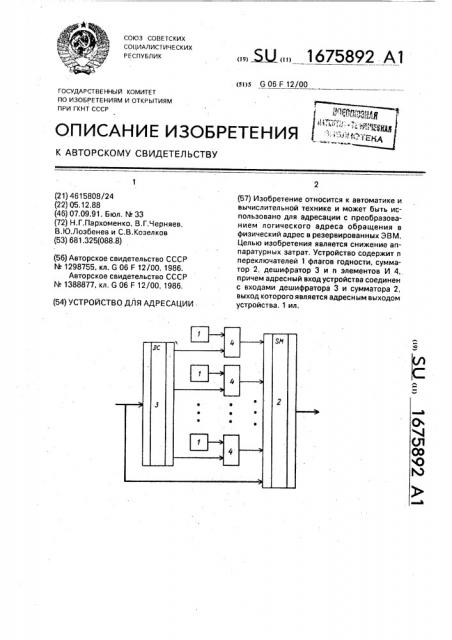

Изобретение относится к автоматике и вычислительной технике и может быть использовано для адресации с преобразованием логического адреса обращения в физический адрес в резервированных ЭВМ. Целью изобретения является снижение аппаратурных затрат. Устройство содержит п переключателей 1 флагов годности, сумматор 2, дешифратор 3 и п элементов И 4, причем адресный вход устройства соединен с входами дешифратора 3 и сумматора 2, выход которого является адресным выходом устройства. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

- (st)s G 06 F 12/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ «ВГЯР т «

"- "f

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4615808/24 (22) 05,12.88 (46) 07.09.91. Бюл. М 33 (72) Н.Г.Пархоменко, В.Г.Черняев, В.Ю.Лозбенев и С, В. Козелков (53) 681.325(088,8) (56) Авторское свидетельство СССР

hL 1298755, кл. G 06 F 12/00, 1986.

Авторское свидетельство СССР

М 1388877, кл. G 06 F 12/00, 1986. (54) УСТРОЙСТВО ДЛЯ АДРЕСАЦИИ Ы 1675892 А1 (57) Изобретение относится к автоматике и вычислительной технике и может быть использовано для адресации с преобразованием логического адреса обращения в физический адрес в резервированных ЭВМ.

Целью изобретения является снижение аппаратурных затрат. Устройство содержит и переключателей 1 флагов годности, сумматор 2, дешифратор 3 и и элементов И 4, причем адресный вход устройства соединен с входами дешифратора 3 и сумматора 2, выход которого является адресным выходом устройства. 1 ил.

1б75892

Переключатели флагов годности установлены в положение низкого уровня (блок годен) или высокого уровня (блок негоден), Составитель А. Баркина

Техред M,Ìoðãåíòaë Корректор И, Myc,ка

Редактор И. Горная

Заказ 3004 Тираж Подписное

ВНИИПИ Государственного комигета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул,Гагарина, 101

Изобретение относится к автоматике и вычислительной технике и может быть использовано для адресации с преобразованием логического адреса обращения в физический адрес в резервированных 3 Á Ì, Целью изобрацФниающряется занижение аппаратурных ад р т „

На чертеже представлена «фн <циональ° . "Ф» ная схема предлагаемого yстройcтea, Устройство содержит и переключателей

1 флагов годности, сумматор 2, дешифратор

3 и и элементов И 4.

Устройство работает следующим обра. зом.

Логический адрес обращения к функциональному .блоку (например, процессору) поступает на вход дешифратора 3 (с нарастающим итогом), который преобразует двоичный позиционный код в двоичный единичный непозиционный код (например, код 101 преобразуется в 11111), Адресу обращения i соответствуют сигналы высокого уровня на выходах с 1-го по i-й дешифратора

Сумматор 2 в общем случае осуществляет сложение (и+1) чисел, где n — число адресуемых блоков памяти (и = 2, где К— к разрядность входного кода), Указанные чис5 ла, поступающие с выходов элементов И 4, являются одноразрядными, а число, поступающее с адресного входа устройства, является К-разрядным, Формирование адреса на выходе сум10 матора происходит в прямом коде (как и на входе устройства).

Формула изобретения

Устройство для адресации, содержащее дешифратор, и переключателей флагов (где

15 n — количество адресуемых блоков памяти), о т л и ч а ю щ е е ся тем, что, с целью снижения аппаратурных затрат, в него введены и элементов И и сумматор, причем выход I-ro переключателя флага (i =1,..., и )

20 соединен с первым входом i-го элемента И, второй вход которого соединен с i-м выходом дешифратора. а выход — с 1-м входом сумматора, причем вход дешифратора (и+1)й вход сумматора объединены и являются

25 адресным входом устройства, выход сумматора является адресным выходом устройства.