Устройство для определения скользящего среднего арифметического

Иллюстрации

Показать всеРеферат

Изобретение относится к средствам специализированной цифровой вычислительной техники для определения среднего арифметического применительно к системам цифрового динамического анализа и может использоваться при решении задач аппроксимации, сглаживания сигналов, изменения динамических и частотных характеристик выборок в акустике, локации, связи, медицине, биологии, в системах аварийного контроля ядерной энергетики. Целью изобретения является расширение функциональных возможностей устройства за счет вычисления скользящего трехточечного среднего четных и нечетных величин. Она достигается путем введения в устройство четырех регистров, двух блоков усреднения , двенадцати элементов И, трех сумматоров, элемента НЕ и двух элементов ИЛИ. Наибольший эффект от использования изобретения достигается при эксплуатации его в системах цифрового динамического спектрального анализа сигналов в скользящем режиме обработки. Высокое быстродействие позволяет включать его в аппаратуру наблюдения, слежения, контроля, работающую в условиях реального масштаба времени. Устройство предназначено для двух ступеней сглаживания сигналов. 1 з.п. ф-лы, 4 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)я 6 06 F 15/36

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1 (21) 3178097/24 (22) 07.08,87 (46) 07.09.91, Бюл. М 33 (72) А.В.Белинский и В.А.Калинников (53) 681.325(088.8) (56) Авторское свидетельство СССР

М 635491, кл. G 06 F 15/36, 1977.

Авторское свидетельство СССР

М 334485, кл. G 06 F 15/36, 1980. (54) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ

СКОЛЬЗЯЩЕГО СРЕДНЕГО АРИФМЕТИЧЕСКОГО (57) Изобретение относится к средствам специализированной цифровой вычислительной техники для определения среднего арифметического применительно к системам цифрового динамического анализа и может использоваться при решении задач аппроксимации, сглаживания сигналов, изменения динамических и частотных характеристик выборок в акустике, локации, Изобретение относится к средствам специализированной цифровой вычислительной техники для определения среднего арифметического применительно к системам цифрового динамического анализа и может использоваться при сглаживании цифровых сигналов в областях акустики, сейсмологии, гидролокации, медицины, биологии, связи, в системах диагностики ядерных энергетических установок.

Целью изобретения является расширение функциональных возможностей за счет возможности вычисления скользящего трехточечного среднего четных и нечетных величин.

„„ 4 „„1675903 А1 связи, медицине, биологии, в системах аварийного контроля ядерной энергетики, Целью изобретения является расширение функциональных возможностей устройства за счет Вычисления скользящего трехточечного среднего четных и нечетных величин, Она достигается путем введения в устройство четырех регистров, двух блоков усреднения, двенадцати элементов lfl, трех сумматоров, элемента НЕ и двух элементов

ИЛИ. Наибольший эффект от использования изобретения достигается при эксплуатации его в системах цифрового динамического спектрального анализа сигналов в скользящем режиме обработки. Высокое быстродействие позволяет включать его в аппаратуру наблюдения, слежения, контроля, работающую в условиях реального масштаба времени. Устройство предназначено для двух ступеней сглаживания сигналов. 1 з.п. ф-лы, 4 ил.

Устройство предназначено для вычисления скользящего среднего арифметического цифровых последовательностей на базе трехточечного алгоритма усреднения с возможностью получения сглаженных цифровых последовательностей относительно четных и нечетных величин по номерам дискретных значений входного сигнала. Устройство позволяет путем сглаживания цифровых последовательностей влиять на частотные характеристики обрабатываемых сигналов, например, перед их спектральным анализом, устранять нежелательные пики в цифровых сигналах, сглаживать дребезг огибающей цифрового сигнала, 1675903

10 зом

40

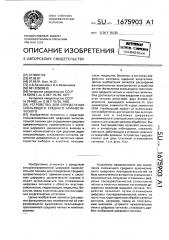

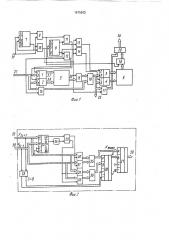

На фиг. 1 изображена функциональная схема предлагаемогс устройства; на фиг. 2 — схема блока ус1зеднения; на фиг, 3— блок-схема операций в блоке усреднения; на фиг. 4 — временная диаграмма работы устройства.

Устройство (фиг, 1) содержит регистры

1 — 4, блоки 5 и 6 усреднения, триггеры 7 и 8, элементы И 9 — 18, элементы ИЛИ 19 и 20, стробирующий вход 21, информационный вход 22 и выходы 23 и 24.

Блок усреднения (фиг. 2) содержит сумматоры 25 — 27, элементы И 28-33, элемент

НЕ 34, элементы ИЛИ 35 и 36. входы 37 и 38 блока и выход 39 блока.

Устройство работает следующим обраТекущие дискретные значения Xi(t), где

1 — номер значения, начиная от единицы, t— время, поступают на входы регистров 1 и 2 и вход элемента 1/ 15. В зависимости от стробирования регистров 1 и 2 от элементов

И 12 и 11 соответственно нечетные значения X2i-1(1) могут бь;ть записаны либо в регистр 1, либо в регистр 2, а также переданы на выход 23 первой ступени сглах<ивания, т.е. на выход элемента ИЛИ 19, Все устройство им;-эет две ступени сглаживания 10 четным и чече. ным значениям и соответственно два выхода 23 и 24. Во

ВТороА ступени сглаживания обработанный первый раз сигнал подвергается повторчо му сглаживанию (фиг, 4).

С помощью блока 5 усреднения ооганизуется режим сглаживания четных значений Х21(т) пс сосе,цним нечетным значениям Х4-з(<) и Х4-1(1:) при отсчете i GTносительно синхроимпульс в С (фиг, 4).

На выход элемента ИЛИ 19 подаются либо истинные нечегные значения Хгьт(1) через элемент И 15, либо сглаженные четные значения X2I (t) через элемент И 16, BG второй ступе1н сглажива1отся нечетные значения X2i+1{t};1o ссседним четным значениям, При это 1 в регистры 3 и 4 записывают величины Х4-2(t) и Х4(т) соответственно (фиг, 4), на основе которых в блоке 6 вычисляется сглаженное значение X2i+1. Через элементы И 17 и 18 и ИЛИ 20 данные передаются на второй выход 24 устройства.

Сущность работы второй ступени аналогична работе первой ступени.

Управление устройством производится следующим образом, Синхроимпульсы С (фиг, 4) поступают на счетный вход триггера 7, который с помощью элементов И 9 и 10 разбивает их на нечетные и четные стробы, C помощью триггера 8, на счетный вход которого поступает четная последова ельность стробов, и элементов И 13 и 14 формируются последовательности стробов с нсмерами 4i-2 и 41 относительно синхроимпульсов, по которым производится запись в регистры 3 и 4, На элементах И 12 и 11 формируются стробы с номерами 41-3 и 4i-1, по которым производится запись данных в регистры

1 и2, По стробу с выхода элемента И 9 через элемент И 15 передаются все истинные нечетные значения с информационного входа

22. Зтот же строб открывает элемент И 18 для прохода усредненных нечетных значений. По стробу с выхода элемента И 10 открываются элементы И 16 и 17 для прохода усредненных честных значений.

Блок 5 усреднения (фиг. 2) предназначен для вычисления среднего Х21(<) в системе скользящего сглаживания сигналов по трехточечному алгоритму, Она работает следующим образом, По записанным в регистрах 1 и 2 данным с помощью сумматора 25 производится сравнение X2I-1(1) и X2i+1(1:) Если Х21+1(т) X2i-;(<), то в соответствии с состоянием пернаго выходаэлемента И 29, управляющего элементами И 30 и 31, через элементы

Yi 30 и ИЛИ 35 значения Хъ+1(т) поступают на вход А, а значения X2i-1(t) через элементы

И 33 и ИЛИ 36 — на вход В второго сумматора 26, При Хг;+1(т) < Хгьт(1) — наоборот: Хг -1(т) через элементы И 3 1 и ИЛИ 35 поступает на вход А, а Х21+1(т) через элементы И 32 и ИЛИ

36 — на вход В сумматора 26.

С помощью элемента И 28определяется признак суммирования Z: если Хгьт() и

Хгн-1(<) имеют разные знаки — признак сложения, иначе — признак вычитания, который подается на фун <циональные входы сумматора 26, Посредством этих операций определяется Хмакс(т) и Хмии(т), В конечном счете в сумматоре 26 вычисляется число, Q =воз((Хмакс(<) Хмин(т))/2) (знак не учитывается), которое затем в сумматоре 27 вычитается из Хмакс(т). На выходе

39 сумматора 27 формируется среднее арИфМЕтИЧЕСКОЕ Хср(т) =Хмакс(т) - Q, т.Е X2i(t)=

= Х2 1(т) - Q, Блок 6 работает и стробируется аналогично блоку 5.

На фиг. 3 представлена блок-схема выполнения операций при работе блока усреднения. На фиг. 4 слева номерами обозначены блоки на фиг, 1, При необходимости устройство может быть расширено за.счет подключения аналогичных секций сглаживания со схемами усреднения, Внешний процессор по мере необходимости может считывать данные с

1675903 любого из выходов 23 или 24. При выполнении устройства на быстродействующих элементах возможно проводить вычисления с интервалом времени между данными до 5 нс.

Формула изобретения

1. Устройство для определения скользящего среднего арифметического, содержащее два триггера, четыре элемента И и первый элемент.ИЛИ, причем прямой выход первого триггера соединен с первым входом первого элемента И, прямой выход второго триггера соединен с первым входом второго элемента И, второй вход которого соединен с выходом третьего элемента И, первый вход которого сое,анен со стробирующим входом устройства, о т л и ч аю щ е е с я тем, что, с целью расширения функциональных возможностей путем вычисления скользящего трехточечного среднего четных и нечетных величин, оно содержит пятый, шестой, седьмой, восьмой, девятый и десятый элементы И, второй элемент ИЛИ, четыре регистра и два блока усреднения, причем стробирующий вход устройства соединен с вторым входом первого элемента И и синхровходом первого триггера, инверсный выход которого соединен с информационным входом первого триггера и вторым входом третьего элемента И, выход которого соединен с синхровходом второго триггера и первыми входами четвертого, пятого и шестого элементов И, выход первого элемента И соединен с первыми входами седьмого, восьмого, девятого и десятого элементов И, второй вход четвертого элемента И соединен с вторым входом восьмого элемента И, информационным входом второго триггера и инверсным выходом второго триггера, прямой выход которого соединен. с вторым входом седьмого элемента И, выходы второго и четвертого элементов И соединены с входами разрешения записи первого и второго регистров соответственно, информационные входы которых соединены с вторым входом шестого элемента И, выходом первого элемента

ИЛИ и являются первым выходом устройства, информационный вход которого соединен с информационными входами третьего и четвертого регистров и вторым входом девятого элемента И, выход которого соединен с первым входом первого элемента

ИЛИ, второй вход которого соединен с выходом пятого элемента И, второй вход которого соединен е выходом первого блока усреднения, первый и второй входы которого соединены с выходами третьего и четвертого регистров, входы разрешения записи которых соединены соответственно с выходами восьмого и седьмого элементов И, выходы первого и второго регистров соединены с первым и вторым входами второго блока усреднения, выход которого соединен с вторым входом десятого элемента

И, выход которого соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом шестого элемента И, выход второго элемента ИЛИ является вторым выходом устройства, 2. Устройство по и, 1, отл и ч а ю щеес я тем, что блок усреднения содержит три сумматора, шесть элементов И, два элемента ИЛИ и элемент НЕ, причем первый вход блока соединен с первым информационным входом первого сумматора и первыми входами первого и второго элементов И, второй вход блока соединен с вторым информационным входом первого сумматора и первыми входами третьего и четвертого элементов И, вторые входы первого и третьего, второго и четвертого элементов И соединены соответственно с прямым и инверсным выходами шестого элемента И, первый и второй входы которого соединены с выходом преломления первого сумматора и выходом элемента НЕ, вход которого соединен с выходом первого сумматора, выходы первого и третьего элементов И соединены с первым и вторым входами первого элемента ИЛИ, выход которого соединен с первыми информационными входами второго и третьего сумматоров, выходы второго и четвертого элементов И соединены с первым и вторым входами второго элемента

ИЛИ, выход которого соединен с вторым информационным входом второго сумматора, первый и второй знаковые разряды которого соединены с инверсным и прямым выходами шестого элемента И. первый и второй входы которого соединены со знаковыми разрядами первого и второго входов блока, выход которого соединен с выходом третьего сумматора, второй информационный вход которого соединен с выходом второго сумматора, 57

Аг.г

1б75903

Составитель О. Березикова

Техред М.Моргентал Корректор И. Муска

Редактор И. Горная

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

Заказ 3004 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5