Универсальная двоичная ячейка

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может быть использовано при построении различных устройств дискретной обработки информации. Целью изобретения является упрощение универсальной двоичной ячейки. Универсальная двоичная ячейка содержит три двухэмиттерных транзистора, три транзистора, четыре резистора и два диода. Введение новых .связей позволяет упростить универсальную двоичную ячейку при сохранении выполняемых функций. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛ ИСТИЧ Е СКИХ РЕСПУБЛИК (s>ls Н 03 К 3/286

ГОСУДАРСТВЕННЫИ КОМИТЕТ

flP ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ ". :

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4608858/21 (22) 23.11.88 (46) 07.09.91. Бюл. М 33 (71) Институт кибернетики с вычислительным центром Научно-производственного объединения "Кибернетика" (72) Т.Ф. Бекмуратов, Б.М.Мансуров, M.K.Арипджанов, М.Б.Бабаханов и Н,Э.Султанов (53) 621,374 (088.8) у (56) Букреев И.Н. и др. Микроэлектронные схемы цифровых устройств. — M.: Советское радио, 1975, с.92, рис. 3-13.

Шагурин И.И. Транзисторно-транзисторные логические схемы. — M.: Советское радио, 1974, с.145, рис. 4.18.

Изобретение относится к импульсной технике и может быть использовано при построении различных устройств дискретной обработки информации, Целью изобретения является упрощение универсальной двоичной ячейки.

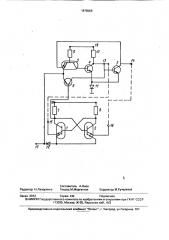

На чертеже приведена принципиальная электрическая схема универсальной двоичной ячейки, Универсальная двоичная ячейка содержит три двухэмиттерных транзистора 1 — 3, транзисторы 4-6, резисторы 7-10, диоды 11 и 12, первый 13 и второй 14 выходы, входы

15 и 16 установки сброса. тактовый вход 17, шину 18 питания.

Коллектор многоэмиттерного транзистора 3 соединен с базой транзистора 3, » . Ы 1676068 А1 (54) УНИВЕРСАЛЬНАЯ ДВОИЧНАЯ ЯЧЕЙКА (57) Изобретение относится к импульсной технике и может быть использовано при построении различных устройств дискретной обработки информации. Целью изобретения является упрощение универсальной двоичной ячейки. Универсальная двоичная ячейка содержит три двухэмиттерных транзистора, три транзистора, четыре резистора и два диода. Введение новых, связей позволяет упростить универсальную двоичную ячейку при сохранении выполняемых функций. 1 ил, коллектор которого соединен с коллектором транзистора 6 и базой транзистора 5, коллектор которого является выходом 13 и соединен с эмиттером транзистора 3, база которого через резистор 9 соединена с шиной 18 питания, которая через резистор 10 соединена с коллекторам транзистора 4, эмиттер транзистора 3 соединен с змиттеоом тоанзистооа 6 и тактовым входом 17.

Эмиттеры транзисторов 4 и 5 через диод 11 соединены с общей шйной, база транзистора 6 соединена с коллектором транзистора

1 с первым выводом резистора 7 и базой транзистора 2, коллектор которого соединен с первыми выводом резистора 8 и базой транзистора 1, вторым выводом резисторы 7 и 8 подключены к шине 18 питания.

Вторые эмиттеры транзисторов 1 и 2 соединены через диод 12 с тактовым входом 17.

Первый эмиттер транзистора 1 является

1676068 входом установки 15, а первый вход транзистора 2 является входом 16 сброса.

При работе универсальной ячейки в счетном режиме выход 13 соединен с входом 15, а выход 14 соединен с входом 16 триггера памяти (на чертеже показаны пунктирными линиями).

Универсальная двоичная ячейка работает следующим образом, Сначала рассмотрим работу ячейки в качестве RS òðèããåðà.

В исходном состоянии присутствуют сигнал на входе 17 Т=.О и сигналы, действующие на входах 15 или 16, так как при Т=О постоянно открыт диод 12 и открыты тран, зисторы 1 и 2.

На входы 15 и 16 подают комбинацию, сигналов $=1, R=O. С поступлением импуль. са на вход 17 (Т-1) диод 12 закрывается и . так как на обоих эмиттерах транзистора 1 действуют сигналы с высоким уровнем, то этот транзистор 1 закрывается. После окончания тактирующего импульса включается . транзистор 6 (на его базе высокий уровень) и закрывается транзистор 5 (так как коллектор транзистора 6 соединен с базой транзистора 5, при открытии транзистора 6 на коллекторе этого транзистора и соответственно на базе транзистора 5 низкий уровень). В результате на выходе 15 устанавливается состояние "1" (0-1). В состояние "0" (0-0) ячейка устанавливается комбинацией сигналов на входах 16 и 15

R- 1, 8- 0 после окончания действия тактирующего импульса. Комбинация сигналов S- R Т- 1 для этого триггерного устройства является запрещенной.

Для организации счетного триггера необходимо соединить выходы 14 и 13 с входами 16 и 15 соответственно.

5 Формула изобретения

Универсальная двоичная ячейка. содержащая два диода, первые эмиттеры первого и второго двухэмиттерных транзисторов соединены соответственно с

10 входами установки и сброса, базы подключены к коллекторам соответственно второго и первого двухэмиттерных транзисторов и,соответственно через первый и второй резисторы соединены с шиной питания, 15 база третьего двухэмиттерного транзистора через третий резистор соединена с шиной питания, коллектор — с базой первого транзистора, эмиттер которого через первый диод соединен с общей шиной и подключен к

20 эмиттеру второго транзистора, коллектор которого соединен с первым эмиттером третьего -транзистора, первый вывод четвертого резистора соединен с шиной питания, эмиттертретьеготранзисто25 ра соединен с тактирующим входом, коллекторы первого и второго транзисторов соединены соответственно с первым и вторым выходами, о т л и ч а ю щ е е с я тем, что, с целью упрощения, вторые эмит30 теры первого и второго двухэмиттерных транзисторов через второй диод соединены с тактирующим входом и вто р ы м эмитте ром третьего двухэмиттерного транзистора, коллектор которого сое35 динен с вторым выводом четвертого резистора, базой второго транзистора и коллектором третьего транзистора, база которого соединена с коллектором первого двухэмиттерного транзистора.

Составитель А.Янов

Редактор Н.Лазоренко Техред М.Моргентал Корректор М,Кучерявая

Заказ 3012 Тираж 950 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101