Многофункциональный логический модуль

Иллюстрации

Показать всеРеферат

Изобретение относится к микроэлектронике и импульсной технике и может быть использовано для реализации симметрических булевых функций переменных . Цель изобретения - повышение быстродействия многофункционального логического модуля. Многофункциональный логический модуль содержит выполненные на МОП-транзисторах п элементов НЕ 1-1 - 1-п (п - число аргументов реализуемых булевых функций), п+ 1 чередующихся ярусов элементов И 2-1 - 2-10, 4-1 - 4-6, 6-1, 6-2 и ИЛ И 3-1 - 3-8, 5-1 - 5-4,7,1-й из которых (I 1,п+1) содержит 2 (п-1+1) логических эле

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)л Н 03 К 19/094

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

@ х . /,, ;,р,!

-,;

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4699788/21 (22) 01.06.89 (46) 07,09,91. Бюл, М 33 (72) Н.А.Егоров, В.И,Гриштанович, Л,Б.Авгуль и Н,И,Антонов (53) 621.325.65(088.8) (56) Применение интегральных микросхем в электронной вычислительной технике:

Справочник./Под ред. В.Н. Ф айзулаева, B.Â.Òàðàáðèíà. — M. Радио и связь, 1987, с.56, рис.3.55.

Авторское свидетельство СССР

М 1264336, кл. Н 03 К 19/094, 1985.

Авторское свидетельство СССР

М 966689, кл. G 06 F 7/00, 1981, ».. Ы 1676093 Al (54) МНОГОФУНКЦИОНАЛЬНЫЙ ЛОГИЧЕСКИЙ МОДУЛЬ (57) Изобретение относится к микроэлектронике и импульсной технике и может быть использовано для реализации симметрических булевых функций переменных. Цель изобретения — повышение быстродействия многофункционального логического модуля. Многофункциональный логический модуль содержит выполненные íà MOll-транзисторах п элементов

НЕ 1-1 — 1-n (n —.число аргументов реализуемых булевых функций), n+ 1 чередующихся ярусов элементов И 2-1 — 2-10, 4-1 — 4-6, 6-1, 6-2 и ИЛ И 3-1 — 3-8, 5-1 — 5-4,7, 1-й из которых (i = 1,п+1) содержит 2 (n — I+1) логических эле1676093

30

50 ментов, и информационных шин, n+1 настроечных шин, одну выходную шину и две шины питания, На информационные шины поступают двоичные переменные х1„.х, на настроечные шины — сигналы настройки

Изобретение относится к микроэлек- 5 тронике и импульсной технике и предназначено для реализации симметрически булевых функций (c,á.ô.)n переменных.

Цель изобретения — повышение быстродействия многофункционального логического модуля.

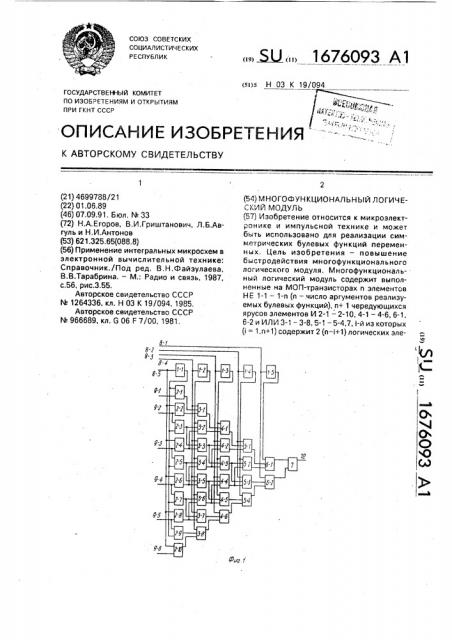

На фиг.1 представлена структурная схема многофункционального логического модуля при n=5; на фиг.2-6 — соответственно принципиальные схемы выполненных на, МОП-транзисторных элементов

НЕ, двухвходового элемента И, трехвходового элемента И, двухвходового элемента

ИЛИ и трехвходового элемента ИЛИ, на которых построен модуль.

Многофункциональный логический модуль при n=5 (фиг.1) содержит п=5 элементов НЕ 1-1 — 1-5, 2n=10 двухвходовых элементов И первого яруса 2-1 — 2-10, 2(n-1) 8 трехвходовых элементов ИЛИ второго яруса 3-1 — 3-8, 2(п-2)=6 трехвходовых элементов И третьего яруса 4-1 — 4-6, 2(n-3)-4 трехвходовых элементов ИЛИ четвертого яруса 5-1 — 5-4, 2(n-4) 2 трехвходовых элементов И пятого яруса 6-1 — 6-2, один двухвходовый элемент ИЛИ шестого яруса 7, и-5 информационных шин 8-Il—

8-5, n+ 1- 6 настроечных шин 9-1 — 9-6, выходную шину 10.

Элемент НЕ (фиг.2) собран на нагрузочном 11 и переключательном 12 МОПтранзисторах, включенных между шинами

13 и 14 питания. Входная шина 15 элемента соединена с затвором транзистора 12, выходная шина 16 — со стоком транзистора 12 (истоком транзистора 11).

Двухвходовый элемент И (фиг.3) собран на переключательных 17 и 18 и нагрузочном

19 МОП вЂ” транзисторах, включенных между шинами 20 и 21 питания. Первая 22 и вторая 23 входные шины элемента соединены соответственно с затворами транзисторов

17 и 18, выходная шина 24 — с,истоком транзистора 18 (со стоком транзистора 19).

Трехвходовый элемент И (фиг,4) собран на переключательных 25 — 27 и нагрузочном

28 МОП-транзисторах, включенных между шинами 29 и 30 питания. Первая 31, вторая л ....к, значения которых принадлежат множеству 0,1, На выходной шине реализуется симметрическая булевая функция F =

F(xI,x,), определяемая вектором настройки л (Р) =(лс, л 1 ...,.„ ), 6 ил.

32 и третья 33 входные шины элемента соединены соответственно с затворами транзисторов 25-27, выходная шина 34— с истоком транзистора 27 (со стоком транзистора 28).

Двухвходовый элемент ИЛИ (фиг.5) собран на переключательных 35 и 36 и нагрузочном 37 МОП-транзисторах, включенных между шинами 38 и 39 питания. Первая 40 и вторая 41 входные шины элемента соединены cooTB|.TGTBBHHo с затворами транзисторов 35 и 36, выходная шина 42 — с истоками транзисторов 35 и 36 (со стоком транзистора 37).

Трехвходовый элемент ИЛИ (фиг.6) собран на переключательных 43 — 45 и нагрузочном 46 МОП-транзисторах, включенных между шинами 47 и 48 питания. Первая 49, вторая 50 и третья 51 входные шины элемента соединены с затворами транзисторов соответственно 43 — 45, выходная шина

52 — с истоками транзисторов 43-45 {со стоком транзистора 46).

Предлагаемый модуль работает следующим образом.

На информационные шины 8-1 — 8-5 поступают двоичные переменные х ...х соответственно, на настроечные шины 9-1—

9-6 — сигналы настройки л ...л соответственно, значения которых принадлежат множеству (0,1), На выходной шине 10 реализуется симметричная булевая функция

F - F(x<,xs). определяемая вектором настройки к (F) = (к,, rc>, л, гц, ц, ль ).

Поясним алгоритм настройки модуля, Пусть симметричная булевая функция (с.б.ф.) F существенно зависит от и аргументов х1 х2 хл и а1 а2,...,аг — рабочие числа F, где 0 < r < и. Такую с.б,ф, обычно а1 в2,...,зг обозначают через Fn . Если г =

1, то с.б.ф. F< называется элементарной (или фундаментальной) с.б,ф, (э.с.б.ф.). Произвольная с,б,ф. F = E(xj,x2,...,хл) может быть задана двоичным вектором ж(Е) = (л>, zr>,..., л ), где л — значение F на(любом) наборе значений п аргументов с i единицами (О 9! и), Очевидно, что д-1 тогда и только тогда, 1676093 когда!е(а1,а2, „ar} и, кроме того, имеет

МЕСТО Р =д» Рй гЛ1 1 й... 1а!» Fn. СЛЕдОВательно, определение компонентов вектора настройки л(Р) =(,л1, „ ) на реализацию некоторой .. б,ф. F сводится к 5 нахождени)о таких элементарных с.б.ф., дизьюнкция двоичных номеров которых дает двоичный номер требуемой функции

F.

Пример. Найти вектор настройки устройства на реализацию с.б.ф.

F = F{x),õ5) = х1х2хз(х4\/х5)1 (х!Х2хз мх1х2хз!" я Х1Х2ХЗ) Х4Х5 (Х1Х2ХЗ а Х1Х2Х31! Х1Х2ХЗ) Х444 Х5 я

> х1х2хз(х49 х5).

Как отмечалось, заданную с.б.ф. можно представить в виде

F(X1,Х5) = Й Л1 Fj Л2 Й ЯЗ Р5 ,7г4 F5 л5 F3.

Причем двоичные номера э.с,б.ф, для.n=5 20 имеют вид:

0 О

F 5 -N5 - (1000 ОООО ОООО ОООО 0000 0000 0000 0000)

1 1

F5 N5 - (0110 1000 1000 0000 1000 0000 0000 0000);

2 2

F5 -N5 - (0001 0110 0110 1000 0110 1000 1000 0000); з з

F5 -N5 - (0000 0001 0001 0110 0001 0110 0110 1000); 25

4 4

F5 -N5 (0000 0000 0000 0001 0000 0001 0001 0110);

F5 -N5 - (0000 0000 0000 0000 0000 0000 0000 0001).

5 5

Двоичный номер заданной с.б.ф.

NF - (0111 1110 1110 1001 1110 1001 1001 0110).

Очевидно NF = N5 N52" N53 30 или

F =(x1,õ5) = F5 F5 V F5 .

Тогда вектор настройки модуля на реализацию заданной с.б,ф, имеет вид л (Г) = (0,1,1,0,1,0). 35

Следовательно, сигналы логического нОн должны быть поданы на первую 9-1, четвертую 9-4 и шестую 9-6 настроечные шины, сигналы логической и1н — на вторую 9-2, третью 9-3 и пятую 9-5 настроенные шины 40 модуля.

Быстродействие модуля, определяемое глубиной схемы, равно

Т = (и+2) г, где т- задержка на вентиль. 45

Формула изобретения

Многофункциональный логический модуль, содержащий n (n — число аргументов реализуемых булевых функций) информаци- 50 онных шин, и+1 настроечную шину и одну. выходную шину, и элементов НЕ, элементы

И и ИЛИ на МОП-транзисторах, входная шина i-го элемента Н Е, (1=1, и) соединена с!-й информационной шиной модуля, о т- 55 л ича ющийся тем,что.сцелью повышения быстродействия, содержит n+1 ярусов логических элементов И и ИЛИ, выходная шина логического элемента (и+1)го яруса соединена с выходной шиной многофункционального логического модуля, (2!-1)-й ярус (j = 1,) () содержит

П

{2п-2) + 21 элементов И, 2S-й ярус

П вЂ” 1 (S = 1, ) (содержит 2(п-2S+ 2) элементов ИЛИ, (и+1)-й ярус содержит один элемент И, если n — четное, или один элемент

ИЛИ, если и — нечетное. первая входная шина (2g-!)-го элемента И r-го яруса (g= л-2r+ 2, r= 2)-!. J - 1, ) — () соединена

2 с выходной шиной r-го элемента НЕ, входная шина которого соединена с первой входной шиной 2g-го элемента И r-яруса первая входная шина (2чч-1)-го элемента ИЛИ t-го яруса (v= n= 2t+ 2, t 2S, 1 и 1

S 1,} — — () соединена с входной шиной

t-f0 элемента НЕ, выходная шина которого соединена с первой входной шиной 2v-го элемента ИЛИ 7-го яруса, вторая входная шина первого элемента И первого яруса соединена с первой настроечной шиной модуля, g-я настроечная шина которого {g=

2,n) соединена с вторыми входными шинами 2 в -го и (2 в +1)-ro элементов И первого яруса (в=1,п-1), (п+ 1)-я настроечная шина соединена с второй входной шиной

2п-ro элемента И первого яруса. выходные шины первого и второго логических элементов в-го яруса (а =1,п-1) соединены соответственно с второй и третьей входными шинами первого логического элемента в + 1 -го яруса, выходная шина (2р-1)-го логического элемента в - го яруса (р=Гй-1,в= 1, и-1) соединена с вторыми входными шинами 2 (р 1) го и (2р 1) го логических элементов (в + 1)-го яруса, третьи входные шины которых соединены с выходной шиной 2р-го логического элемента в - ro яруса, вы:;одные шины (2п-2 и) + 1)-го и 2(n-cd+1)-rq логических элементов и -го яруса (cd -1д-.1) соединены соответственно с второй и третьей входными шинами 2(n- cd)-ro логического элемента (cd+ 1)-го яруса, выходные шины первого и второго логических элементов п-го яруса соединены соответственно с первой и второй -ходными шинами логического элемента (и+1)-го яруса.

1676093 г2 ( л

Puz.2

Составитель С.Скворцов

Редактор Н.Гунько Техред M. Мор гентал Корректор IVI.Màêñèìèøèíåö

Заказ 3014 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР i13035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул, Гагарина, 101