Двоично-десятичный счетчик

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной и вычислительной технике, в частности к импульсным счетчикам с фазоимпульсным представлением информации, и может быть использовано в устройствах промышленной автоматики и вычислительной техники с повышенными характеристиками экономичности и надежности функционирования . Цель изобретения - повышение достоверности функционирования и автоматизации процесса восстановления работоспособности. Двоично-десятичный

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)5 Н 03 К 23/72

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

5/ 5z И/ Р5,т г7 ля (21) 4738125/21 (22) 13.09.89 (46) 07.09.91. Бюл, М 33 (72) А, Н.Пархоменко, В. В, Голубцов, В.С.Харламов и А.Е.Корняков (53) 621.374.323(088.8) (56) Интегральные микросхемы. Справочник./Под ред. Б.В. Тарабрина. — М.: Радио и связь, 1983, с.239, Авторское свидетельство СССР

М 1370784, кл. Н 03 К 23/72, 1987. (54) ДВОИЧНО-ДЕСЯТИЧНЫЙ СЧЕТЧИК. Ж» 1676098 А1 (57) Изобретение относится к импульсной и вычислительной технике, в частности к импульсным счетчикам с фазоимпульсным представлением информации,. и может быть использовано в устройствах промышленной автоматики и вычислительной техники с повышенными характеристиками экономичности и надежности функционирования. Цель изобретения — повышение достоверности функционирования и автоматизации процесса восстановления работоспособности, Двоично-десятичный (Ь

"4

О

О

СО

1676098

40 счетчик реализован по многоразрядной схеме на IK-триггерах 6.1-6.5 с встроенными средствами контроля правильности срабатывания и элементах И 11,1-11.3, 13,14,16, 18.1-18.4, 19,1 — 19.4, И вЂ” ИЛИ 7.17.4, 8,1-8.3, 9.1-9.3, ИЛИ 10,1 — 10.3

12,15,17.1-17.4, Наличие в структуре двоично-десятичного счетчика средств функционального контроля основных его элементов — триггеров и средств автоматической реконфигурации работоспособной структуры позволяет автоматизировать

Изобретение относится к импульсной и вычислительной технике, в частности к импульсным счетчикам с фазоимпульсным представлением информации, и может быть применено в устройствах промышленной автоматики и вычислительной техники.

Цель изобретения — повышение достоверности функционирования и BBтоматизация процесса восстановления работоспособности.

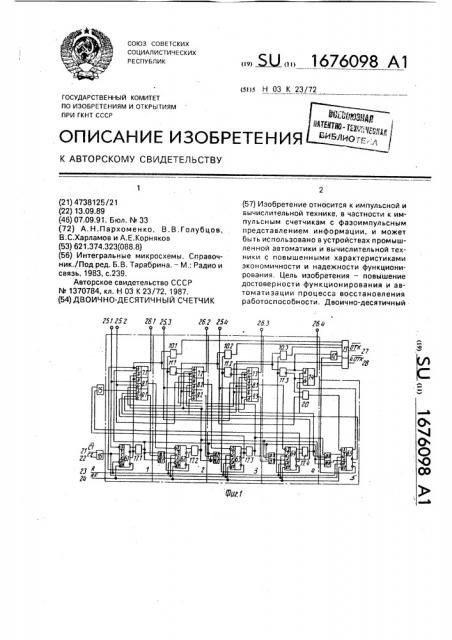

На фиг.1 представлена структурная схема предлагаемого двоично-десятичного счетчика на фиг.2 — функциональная схема триггера каждого разряда; на фиг,3 — временная диаграмма его работы.

Двоично-десятичный счетчик содержит основные 1 — 4 и резервный 5 разряды, триггеры 6.1-6.5 разрядов, первые 7.1-7.4, вторые 8,1-8.3 и третьи 9.1-9.3 элементы

2-2И-ИЛИ разрядов, вторые 10.1-10,3 элементы ИЛИ разрядов. элементы И/И вЂ” НЕ

11,1-11,3 разрядов, второй 12 элемент ИЛИ устройства, второй 13 и третий 14 элементы

И устройства, первый 15 элемент ИЛИ устройства, первый 16 элемент И устройства, первые 17.1-17.4 элементы ИЛИ разрядов, первые 18.1-18.4 и вторые 19;1-19.4 элементы И разрядов, третий элемент И 20 четвертого разряда, Первый 21 и второй 22 синхровходы (фиг.1) устройства соединены соответственно с первым и вторым входами первого элемента И 16 устройства, выход которого соединен со счетными входами триггеров

6.1-6.5. Вход 23 установки в "0" устройства соединен с R-входами триггеров 6,1-6.5, Вход 24 установки в исходное состояние средств функционального контроля устройства соединен с Rt=-входами триггеров

6. 1 — 6,5. процесс восстановления работоспособности счетчика при отказе одного из разрядов, что повышает долговечность интегральной микросхемы и сокращает время восстановления работоспособности устройств автоматики и вычислительной техники на этапе их эксплуатации. Работа предложенного двоично-десятичного счетчика поясняется таблицами, приведенными в описании изобретения, и временной диаграммой работы триггера каждого разряда. 5 табл„З ил, Вход 25.1 предустанова первого разряда соединен с вторым входом первой группы входов элемента 2 — 2И вЂ” ИЛИ 8.1 и с инверсным Я-входом триггера 6.1. Вход25,2 предустанова второгого разряда соединен с первым входом второй группы входов элемента 2 — 2И вЂ” ИЛИ 8.1 с вторым входом первой группы входов элемента 2 — 2И вЂ” ИЛИ 8.2.

Вход 25.3 предустанова третьего разряда соединен с вторым входом второй группы входов элемента 2 — 2И-ИЛИ 8.2 и вторым входом первой группы входов элемента 22И вЂ” ИЛИ 8.3. Вход 25.4 предустанова четвертого разряда соединен с вторым входом второй группы входов элемента 2 — 2И-ИЛИ

8.3 и вторым входом элемента И 20.

Прямой выход триггера 6,1 соединен с первым входом элемента ИЛИ 17,1, выход которого соединен с вторым входом первой группы входов элемента 2 — 2И-ИЛИ 7,1, первыми входами элементов И 18,1 — 18. 3 и

19.1 — 19.3, четвертым входом элемента И

18.4 и с входом элемента И 19.4. Выход

"Отказ" триггера 6,1 соединен с вторым входом элемента ИЛИ 17,1, первым входом второй группы входов элемента 2 — 2И вЂ” ИЛИ 7.1 и с первым входом первой группы входов элемента 2 — 2И-ИЛИ 8,1. Выход "Отсутствие отказа" триггера 6.1 соединен с первым входом первой группы входов элемента 22И вЂ” ИЛИ 7.1 и первыми входами элементов

ИЛИ, 10.1 и И/И-НЕ 11.1. Выход элемента

2 — 2И вЂ” ИЛИ 7,1 является первым 26.1 информационным выходом устройства, Выход элемента 2-2И-ИЛИ 8.1 соединен с инверсным S-входом триггера 6.2, Выход элемента 2 — 2И вЂ” ИЛИ 9.1 соединен с вторым входом элемента И 18,1, выход которого соединен с

1-входом триггера 6,2, Выход элемента И

19,2 соединен с К--входом триггера 6.2.

Прямой выход триггера 6,2 соединен с первым входом элемента ИЛИ 72, выход

1676098

20

25 соединен с вторым входом элемента ИЛИ 40

50

55 которого соединен с вторым входом второй группы входов элемента 2-2И вЂ” ИЛИ

7.1, вторым входом первой группы входов элемента 2 — 2И вЂ” ИЛИ 7.2, вторым входом второй группы входов элемента 2-2ИИЛИ 9.3, с вторыми входами элементов И

18.2 и 19.2, третьим входом элемента И 18.3 и с третьим входом элемента И 18.4. Выход

"Отказ" триггера 6.2 соединен с вторым входом элемента ИЛ И 17.2. В ыход "Отсутствие отказа" триггера 6.2 соединен с вторыми входами элементов ИЛИ 10.1 и И/И-НЕ

11,1, Выход элемента ИЛИ 10.1 соединен с первым входом элемента И 13. Прямой выходэлемента И/И вЂ” НЕ 11.1 соединен с вторым входом второй группы входов элемента 2 — 2И вЂ” ИЛИ 8,1, входсв. первой группы входов злемечта 2-2И вЂ” ИЛИ 9.2, первым входом первой группы входов элемента 2 — 2И вЂ” ИЛИ 7.2 и с первыми входами элементов ИЛИ 10.2 и И/И-НЕ 11.2. Выход элемента 2 — 2И вЂ” ИЛИ 7.2 является вторым информационным выходом 26.2 устройства, Выход элемента 2-2И-ИЛИ 8.2 соединен с инверсным S-входом триггера 6.3, Выход элемента 2-2И-ИЛИ 9.2 соединен с третьим входом элемента И 18.2.

Выход элемента И 18.2 соединен с 1входом триггера 6.3, К-вход которого соединен с выходом элемента И 19.2. Прямой выход триггера 6.3 соединен с первым входом элемента ИЛИ 17.3, выход которого соединен с вторым входом элемента И 18.3, вторым входом второй группы входов элемента 2 —.2И вЂ” ИЛИ 7,2, вторым входом первой группы входов элемента 2 — 2И вЂ” ИЛ И 7.3, первым входом второй группы входов элемента 2-2И-ИЛИ 9,3 и с первым входом элемента И 18.4. Выход "Отказ" триггера 6.3

17.3 и первым входом элемента ИЛИ 15.

Выход "Отсутствие отказа" триггера 6,3 соединен с вторыми входами элементом ИЛИ

10.3 и И/И вЂ” НЕ 11.3, Выход элемента ИЛИ

10.3 соединен с вторым входом элемента И

13. Прямой выход элемента И/И-НЕ,11.2 соединен с первым входом второй группы входов элемента 2-2И-ИЛИ 8.2, входом первой группы входов элемента 2 — 2И вЂ” ИЛИ

9,3, первым входом первой группы входов элемента 2 — 2И вЂ” ИЛИ 7,3 и с первыми входами элементов ИЛИ 10.3 и И/И вЂ” НЕ 11.3.

Выход элемента 2-2И-ИЛИ 7,3 является третьим информационным выходом 26,3 óñтройства. Выход элемента 2-2И вЂ” ИЛИ 8,3 соединен с инверсным S-входом триггера

6.4. Выход элемента 2-2И-ИЛИ 9.3 соединен с вторым входом элемента И 19,3.

Выход элемента И 18.3 соединен с 1-входом триггера 6,4, К-вход которого соединен

10

35 с выходом элемента И 19.3. Прямой выход триггера б:4 соединен с первым входом элемента ИЛИ 17.4, выход которого соединен с вторым входом элемента И 18.4, вторым входом второй группы входов элемента 2 — 2И вЂ” ИЛИ 7.3 и с вторым входом первой группы входоа элемента 2 — 2И вЂ” ИЛИ

7.4, И н версн ый выход триггера 6.4 соединен с вторым входом второй группы входов элемента 2 — 2И вЂ” ИЛИ 9.1. Выход "Отказ" триггера 6.4 соединен с вторым входом элемента

ИЛИ 17,4 и вторым входом элемента ИЛИ

15. Выход "Отсутствие отказа" триггера 6.4 соединен с вторыми входами элементов

ИЛИ 10.3 и И/И-НЕ 11.3, Выход элемента

ИЛИ 10,3 соединен с третьим входом элемента И 13. Прямой выход элемента И/И—

НЕ 11.3 соединен с первым входом первой группы входов элемента 2 — 2И вЂ” ИЛИ 7.4, первым входом элемента ИЛИ 12, первым входом элемента И 14, первым входом второй группы входов элемента 2 — 2И вЂ” ИЛИ 8.3 и с первым входом второй группы входов элемента 2 — 2И вЂ” ИЛИ 9.1. Инверсный выход элемента И/И-НЕ 11.3 соединен с первым входом второй группы входов элемента 22И-ИЛИ 7.4 и с первым входом элемента И

20, выход которого соединен с инверсным

S-входом триггера 6.5. Выход элемента 22И вЂ” ИЛИ 7.4 является четвертым информационным выходом 26.4 устройства.

Выход элемента И 18.4 соединен с 1-входом триггера 6,5, К-вход которого соединен с выходом элемента И 19.4. Прямой выход триггера 6.5 соединен с вторым входом второй группы входов элемента 2 — 2И вЂ” ИЛИ

7.4. Инверсный выход триггера 6,5 соединен с вторым входом первой группы входов элемента 2 — 2И вЂ” ИЛИ 9.1 и вторым входом второй группы входов элемента 2 — 2И вЂ” ИПИ 9.2.

Выход "Отсутствие отказа" триггера 6,5 соединен с вторыми входами элементов ИЛИ

1? и И 14, Выход элемента ИЛИ 12 соединен с четвертым входом элемента И 13, выход которого является выходом 27 "Отсутствие отказа" устройства. Выход элемента ИЛИ 15 соединен с первым входом первой группы входов элемента 2 — 2И-ИЛИ 9.1. Выход элемента И 14 является выходом 28 "Отсутствие частичного отказа" устройства.

Триггер каждого разряда (фиг.2) содержит первый 29 и второй 30 элементы И—

ИЛИ-НЕ, первый 31 и второй 32 элементы

И, первый-четвертый 33-36 элементы ИНЕ, первый 37 элемент НЕ, третий элемент

И 38, второй элемент НЕ 39, четвертый элемент И 40, элемент И/И-НЕ 41 и элемент

7И вЂ” ИЛИ/7И вЂ” ИЛИ вЂ” НЕ 42, R-вход 43 триггера каждого разряда (фиг,2) соединен с первым входом элемента

1676098

И 40, вторым входом первой и первым входом второй групп входов элемента И-ИЛИНЕ 29, с первым входом элемента И 31 и первым входом элемента И вЂ” НЕ 36. I-вход

44 трипера каждого разряда соединен с третьим входом второй группы входом элемента И вЂ” ИЛИ вЂ” HE 29, вторым входом элемента И/И вЂ” НЕ 41 и вторым входом третьей группы входов элемента 7И-ИЛИ/7ИИЛИ-HE 42.Синхровод 45 триггера каждого разряда соединен с четвертым входом второй группы входов элемента И вЂ” ИЛИ-НЕ 29, первым. входом первой группы входов элемента И-ИЛИ вЂ” НЕ 30 и с входом элеменга

НЕ 37, К-вход 46 триггера каждого разряда соединен с вторым входом первой группы входов элемента И-ИЛИ-НЕ 30, первым входом элемента И/И-НЕ 41 и с первым входом четвертой группьi входов элемента

7И-ИЛИ/7И вЂ” ИЛИ-Н Е 42. 5-вход 47 триггера каждого разряда соединен с четвертым входом первой и первым входом второй групп входов элемента И вЂ” ИЛ И-Н Е 30, с третьим входом элемента И 32 и третьим входом элемента И вЂ” НЕ 35. RF-вход 48 триггера каждого разряда соединен с первым входом седьмой группы входов элемента

7И вЂ” ИЛИ/7И вЂ” ИЛИ вЂ” НЕ 42. Выход элемента

И-ИЛИ-НЕ 29 соединен с вторым входом элемента И 32 и вторым входом второй группы входов элемента И вЂ” ИЛИ вЂ” НЕ 30, выход которого соединен с вторым входом элемента И 31 и первым входом первой группы входов элемента И-ИЛИ-НЕ 29, Выход элемента И 31 соединен с первым входом элемента И вЂ” НЕ 33, третьим входом второй, вторым входом четвертой и с вторым входом пятой групп входов элемента 7И—

ИЛИ/7И вЂ” ИЛИ-Н Е 42. Выход элемента И 32 соединен с вторым входом элемента И-НЕ

34, четвертым входом первой, первым входом третьей и с вторым входом шестой групп входов элемента 7И вЂ” ИЛИ/7И вЂ” ИЛИНЕ 42. Выход элемента И вЂ” НЕ 33 соединен с вторым входом элемента И-НЕ 35, первым входом элемента И 38 и первым входом элемента И 32. Выход элемента VII--HE

34 соединен с вторым входом элемента

И вЂ” НЕ 36, вторым входом элемента И 38 и третьим. входом элемента И 31, Выход weмента НЕ 37 соединен с вторым входом элемента И-HE 33, первым входом элемента И-НЕ 34, третьим входом первой и с вторым входом второй групп входов элемента 7И вЂ” ИЛИ/7И-ИЛИ-НЕ 42. Выход элемента И 38 соединен с входом элемента Н Е 39 и третьим входом третьей, четвертой, пятой и шестой групп входов элемента

7И вЂ” ИЛИ/7И-ИЛИ-НЕ 42. Выход элемента

НЕ 39 соединен с вторым входом первой и

40 первым входом второй групп входов элемента 7И-ИЛИ/7И вЂ” ИЛИ вЂ” НЕ 42, Выход элемента И 40 соединен с пятыми входами первой и второй, с четвертыми входами третьей, четвертой, пятой и шестой групп входов элемента 7И вЂ” ИЛИ/7А — ИЛИ вЂ” НЕ

42. Инверсный выход элемента И/И вЂ” HE

41 соединен с пятыми входами третьей и четвертой групп входов элемента 7И—

ИЛИ/7И вЂ” ИЛИ вЂ” НЕ 42, Прямой выход элемента И/И вЂ” НЕ 41 соединен с пятыми входами пятой и шестой групп входов элемента 7И вЂ” ИЛИ/7И-ИЛИ вЂ” НЕ 42, прямой выход которого является выходом "Отказ" триггера и соединен с вторым в:<одом своей седьм и группы входов. Инверсный выход элемента 7И вЂ” ИЛИ/7И вЂ” ИЛИ-НЕ 42 является выходом 51 "Отсутствие атк за" триггера каждого разряда. Выход элемента И вЂ” НЕ 35 является прямым выходом триггера каждого разряда и соединен с третьим входом элемента И вЂ” НЕ 36, третьим входом первсй группы входов элемента И вЂ” ИЛИ вЂ” НЕ 30 и первыми входами первой и пятой групп входов элемента 7И вЂ” ИЛИ/7И вЂ” ИЛИ-НЕ 42. Выход элемента И вЂ” НЕ 36 является инверсным выходом 50 триггера и соединен с вторым входом второй группы входов элемента И—

ИЛИ вЂ” НЕ 29, первым входом элемента И-НЕ

35, четвертым входом второй и с первым входом шестой групп входов элемента 7ИИЛИ/7И вЂ” ИЛИ вЂ” НЕ 42.

Рассмотрим функциональное назначение элементов логической структуры предлагаемого двоично-десятичного счетчика, Разряды 1 — 4 являются основными разрядами двоично-десятичного счетчика, выполняющими заданный набор функций устройства. Разряд 5 является резервным разрядом двоична-десятичного счетчика и предназначен для автоматического замещения одного из основных разрядов при его отказе, Триггеры 6.1-6.5 предназначены для хранения числа накопленных импульсов, поступивших на синхровходы 21 и 22 устройства при разрешении их счета, Кроме этой функции в структуре каждого триггера имеются средства встроенного контроля, которые позволяют непрерывно контролировать правильность срабатывания всех логических элементов триггера каждого разряда.

Первые элементы 2 — 2И вЂ” ИЛИ 7,1-7.4 предназначены для коммутации на соответствующие информационные выходы

26.1 — 26,4 устройства значений сигналов с прямых выходов триггеров данного или последующего разрядов.

1676098

Вторые элементы 2 — 2И вЂ” ИЛИ 8.1 — 8.3 и элемент И 20 осуществляют коммутацию входа предустанова 25,1 — 25.4 на инверсный вход триггера данного или последующего разряда, в зависимости от его исправного (или неисправного) состояния.

Третьи элементы 2 — 2И вЂ” ИЛИ 9,1 — 9,3 обеспечивают алгоритм функционирования двоично-десятичного счетчика, учиты-» вая работоспособность соответствующих триггеров разрядов, Элементы ИЛИ 10.1 — 10.3 и 12 предназначены для обобщения сигналов "Отсутствие отказа" триггеров 6,1-6.5 разрядов, Элементы И/И вЂ” НЕ 11,1 — 11.3 используются для формирования функций учета исправного (неисправного) со"тояния триггеров одноименного и всех предыдущих разрядов На прямом и инверсном выходах элемента И/И-НЕ 11.1 формируются соответственно функции г.!лг.г и Е1" Е2 {где

F>, имея значение логической единицы, означает исправность соответствующего триггера; F>, имея значение логического нуля, означает неисправность соответствующего триггера). Соответственно на выходах элемента И/И вЂ” НЕ 11.2 формируются функции

Fi Рг Рз и FI< Fz Fg, а на выходах элемента

И/И вЂ” Н Е 1,3 формируются F1 F2 F3 + F4 и

F)> Fg< F3

Элемент И 13 обобщает сигнал "Отсутствие отказа" во всех триггерах 6.1-6.5 разрядов и формирует на своем выходе сигнал

"Отсутствие отказа" устройства в целом.

Элемент И 14 формирует на своем выходе сигнал "Отсутствие частичного отказа" означающего, что в устройстве нет откаэавmего ни одного триггера разрядов. При отказе хотя бы одного из триггеров 6.1 — 6.5 на выходе элемента И 14 формируется нулевой логический потенциал, сигнализирующий о наличии частичного отказа в устройстве.

Элементы ИЛИ 17,1-17.4 предназначены для блокировки значения логического уровня сигнала на прямом выходе отказавmего триггера на логику работы исправных элементов устройства, Первые 18,1 — 18,4 и вторые 19.1-19.4 элементы И являются входной логикой !- и

К-входов триггеров разрядов двоично-десятичного счетчика.

Элементы И вЂ” ИЛИ-НЕ 29 и 30, И 31 и 32, HE 37 и И-НЕ 33 и 34 образуют схему вспомогательного триггера с входной логикой работы IK- или RS-триггера (фиг.2).

Элементы И-НЕ 35 и 36 образуют схему основного триггера каждого разряда.

Элемент HE 37 предназначен для организации двухтактного режима работы !К10

55 триггера при Hàëè÷èè одного тактового входа 45. Кроме того, на выходе элемента НЕ

37 вырабатывается сигнал разрешения сравнения сигналов на противоположных плечах (выходах) основного и вспомогательного триггеров (фиг,2 точки А и Q, точки А и

Q) в режиме хранения информации.

Элемент И 38 обеспечивает контроль наличия сигнала запрета работы основного триггера и формирует на своем выходе сигнал строба сравнения, задержанного относительно положительного фронта тактового сигнала С на время не менее

3T: (где T ð — время срабатывания одного логического элемента структуры триггера), т.е. на время срабатывания элементов НЕ

37, И-HF 33 и 35, а также на время срабатывания самого элемента И 38. Особенностью элемента И 38 является то, что его время срабатывания должно быть не менее Т р. т.е. если для остальных логических элементов структуры IK-триггера время срабатывания "-»îçìoæío не более Т >, то для элемента

И 38 оно должно быть не менес Тср. Данное ограничение можно выполнить при разработке технологии микросхемы.

Элемент НЕ 39 предназначен для формирования на своем выходе сигнала строба сравнения. задержанного на время 4Т р относительно отрицательного фронта тактового сигнала С.

Элемент И 40 предназначен для формирования сигнала запрета сравнения во второй, третьей, четвертой, пятой, шестой и первой группах входов элемента 7И—

ИЛИ/7И вЂ” ИЛИ-НЕ 42 в момент асинхронной установки II"-триггера по его входам Я

43 и S 47, соответственно, в нулевое или еди ничное состоя н ие.

Элемент И/И вЂ” HE 41 на своих прямом и инверсном выходах формирует сигнал функций К и I v КK, которыми открываются соответственно пятая и шестая, а также третья и четвертая группы входов элемента 7ИИЛИ/7И вЂ” ИЛИ вЂ” НЕ 42, который осуществля» ет на своих группах входов контроль правильности срабатывания всех логических элементов структуры !К-триггера. В случае нарушения логики функционирования (отказ какого-либо логического элемента структуры триггера) на прямом выходе элемента 7И вЂ” ИЛИ/7И вЂ” ИЛИ вЂ” НЕ 42 формируется сигнал "Отказ", который посредством своей обратной связи через в-орой вход седьмой группы входов осуществляет так называемый "эффект самозахвата", т.е., устанавливается в устойчивое состояние логической единицы.

В общем случае на входах элемента 7И—

ИЛИ/7И вЂ” ИЛИ-НЕ 42 реализуется функци1676098

12 онал отказа, который можно представить следующим аналитическим выражением;

F = (CIKRS) Р3 (CIKRS) А V(CIKRS) . А Q У(С!КЯЯ) А QyС А Q R SVC À Q R к5 (!) 5 где С, С вЂ” единичное и нулевое состояние тактового сигнала на С-входе 45 !К-триггеpа;

i, — единичное и нулевое состояние сигнала на входе 44 !К-триггера; 10

К, К вЂ” единичное и нулевое состояние сигнала на К-входе 46 !К-триггера, R — единичное состояние сигнала íà Rвходе 43 IK-триггера;

S — единичное состояние сигнала на S- 15 входе 47 I К-триггера;

А, А — единичное и нулевое состояние сигналов соответственно в точках А и А на фиг,2;

Q, 0 — состояния сигналов на прямом 49 20 и инверсном 50 выходах IK-триггера, Триггер каждого разряда в процессе функционирования двоично-десятичного счетчика работает следующим. образом.

После включения питания íà RF-вход 48 25 триггера каждого разряда подается нулевой уровень сигнала для установки в исходное состояние средств функционального контроля, так как в силу случайного характера переходных процессов во время включе- 30 ния питания элемент 7И-ИЛИ/7И вЂ” ИЛИНЕ 42 с обратной связью (однофазный триггер) может установиться в единичное состояние на своем прямом выходе. соответствующее сигналу отказ любого иэ 35 триггеров разрядов.

Далее, при исправном состоянии всех логических элементов, работа триггера каждого разряда подчиняется (соответствует) закону функционирования, приведенному в 40 сокращенной табл.1 переходов IK-триггера.

Из табл.1 видно, что IK-.òðèããåð работает в двух режимах:: в синхронном режиме

IK-триггера и в асинхронном режиме RSтриггера. 45

Рассмотрим подробнее каждый из режимов работы универсального fK-триггера каждого разряда и работу элементов функционального контроля за правильностью срабатывания основных логических эле- 50 ментов триггера в ходе его функционирования.

В синхронном режиме работы! К-триггер каждого разряда функционирует в соответствии с табл.2 переходов. 55

В процессе своего функционирования первая ступень IK-триггера подчиняется закону, представленному следующими аналитическими выражениями;

1 (А = "1 ") =- IKC/RS/VIKAC/RS/; (А = "1 ")=

= I КС/R S/v I KAC/R S/, (2) где !, — единичное и нулевое соответственно состояния сигналов на I-входе IKтриггера;

К, К вЂ” единичное и нулевое соответственно состояния сигналов на К-входе IKтриггера;

С вЂ” единичное состояние сигнала на тактовом входе !К-триггера;

R — единичное состояние сигнала на йвходе триггера;

S — единичное состояние сигнала íà Sвходе триггера;

А, А — единичное состояние сигнала на выходах элементов И 31 и 32 IK-триггера, В табл.1 и 2 приняты следующие сокращения: — вход i 44 IK-триггера; К вЂ” вход

К 46 IK-триггера; R — вход R 43 iK-триггера;

S — вход S 47 IK-триггера; С вЂ” тактовый вход

С 45 iK-триггера; RF — вход 48 установки в исходное состоянйе средств функционального контроля (СФ К) К-; 0 — прямой выход 49 триггера; б — инверсный выход 50 триггера; F — выход 51 "Отсутствие отказа" триггера, Š— выход 52 "Отказ" .IК-триггера;

Х вЂ” информация низкого или высокого логического уровня на соответствующем входе триггера; С4, Qn — предыдущее состояние сигнала на прямом и инверсном соответственно выходе триггера; Т„- момент времени до подачи отрицательного фронта тактового импульса; Т„+ — момент времени после подачи отрицательного фронта тактового импульса; Н- неопределенное состо-, яние сигнала на соответствующем выходе триггера; - переход от высокого уровня сигнала к низкому на С-входе 45 триггера.

За выполнением условий выражения (2) следят четвертая, пятая, шестая и третья структуры (группы входов) элемента 7ИИЛИ/7И вЂ” ИЛИ вЂ” НЕ 42.

В процессе своего функционирования вторая ступень iK-триггера (основной триггер) подчиняется закону, представленному следующими аналитическими выражениями; (Q="1")=А С;(Q="1")=А С, (3)

За выполнением условий выражения (3) следят первая и вторая группы входов элемента 7И-ИЛИ/7И-ИЛИ-HE 42.

Функционал отказа любого из логических элементов первой ступени (вспомогательного триггера), реализованный в предлагаемом техническом решении ! К-триггера каждого разряда, можно представить следующим «налитическим выражением:

13

1676098

14 представить выражением

F=Q А CVQ А С. (5)

В случае нарушения условий функционирования, представленных в вь ражении (3), на выходе (прямом) элемента 7И—

ИЛИ/7И вЂ” ИЛИ вЂ” НЕ 42 также вырабатывается сигнал "Отказ" IK-триггера. 2

Рассмотрим последовательность срабатывания всех элементов логической стурктуры предлагаемого IK-триггера в его четырех основных режимах функционирования: хранение, установка "0", установка 2

"1" и инверсия.

В режиме хранения (табл.2, п.3) с приходом положительного фронта тактового импульса на С-вход триггера каждого разряда изменение состояния во вспомогательном 3 триггере не производится. Это обусловлено следующим образом. Примем, что предыдущее состояние IK-триггера было единичным. Тогда при нулевых логических уровнях сигнала на I- и К-входах и единичных уров- 3 нях сигналах íà R-, S- u RF-входах будут закрыты вторые группы входов элементов

И вЂ” ИЛИ вЂ” НЕ 29 и 30, а открыты первые структуры И элементов И-ИЛИ-HE 29 и 30. Таким образом, срабатывание вспомогательного 4 триггера не происходит. Контроль правильности хранения предыдущего состояния в

IK-триггере каждого- разряда происходит следующим образом. В результате вы-, полнения триггером режима хранения 4 состояний основного и вспомогательного триггеров должны совпадать. В предлагаемом устройстве это осуществляется первой и второй группами входов элемента 7И-ИЛИ/7И-ИЛИ-НЕ 42 (фиг.2), 5 на входе которых подаются сигналы с противоположных плеч основного и вспомогательного триггеров (точки А и О, А и Q на фиг.2 соответственно), а также сигнал разрешения проведения сравнения 5 при тактовом сигнале С = 0 с выхода элемента HE 32 и после допустимого времени срабатывания всех элементов основного и вспомогательного триггеров, равного 4Тср, F = IKC(RS) А IKC(RS) А IKAQ(RS)

С IKAQ(RS) С, (4)

В случае нарушения условий функционирования, представленных в выражении (2) на выходе (прямом) элемента 7И—

ИЛИ/7И-ИЛИ-НЕ 42 уже в момент срабатывания логических элементов первой ступени вырабатывается сигнал "Отказ" IKтриггера.

Функционал отказа любого из логических элементов второй ступени (основного триггера), реализованный в техническом решении IK-триггера каждого разряда, можно с выхода элемента НЕ 39. При исправном функционировании всех основных логических элементов триггера каждого разряда на выходе 52 присутствует сигнал низкого

5 логического уровня и в противном случае триггер 42 формирует на своем прямом выходе высокий логический уровень сигнала.

При установке IK-триггера в состояние

10 "0" (табл.2, п.4) с приходом положительного фронта синхроимпульса на входе 45 производится запись нулевого состояния во вспомогательный триггер и, на время действия его высокого уровня, в основ15 ном триггере хранится предыдущее состояние, так как с выхода элемента HE 37 на входы элементов И вЂ” НЕ ЗЗ и 34 поступает нулевой логический уровень сигнала, блокирующий возможное воздействие

0 переходных процессов в элементах ИИЛИ-НЕ 29 и 30, И 31 и 32 вспомогатель. ного триггера на состояние основного триггера (элементы И вЂ” НЕ 35 и 36). Срабатывание элементов вспомогательного тригге5 ра происходит следующим образом. При предыдущем единичном состоянии триггера каждого разряда вторая группа входов элемента И-ИЛИ вЂ” HE 30 открыта и на его выходе через время T р будет установлен

0 сигнал нулевого логического уровня. Первая и вторая группы входов элемента И—

ИЛИ--НЕ 29 будут закрыты нулевыми потенциалами с выхода элемента И вЂ” НЕ 36 и с выхода элемента И-ИЛИ-НЕ 30. Через

5 время 2Тср с момента поступления положительного фронта синхроимпульса на вход 45, на выходах элементов И вЂ” НЕ 33 и

34 установится высокий логический уровень сигнала, Таким образом, через время

0 2Тср с момента поступления положительного фронта синхроимпульса на входах элементов И 31 и 32 присутствуют следующие сигналы; элемент И 31 будет закрыт нулевым логическим уровнем сигнала с вы5 хода элемента И вЂ” ИЛИ вЂ” НЕ 30, элемент И 32 пропустит на свой выход высокий логический уровень сигнала, так как на его входах будут присутствовать все высокие логические уровни сигналов (с выхода эле0 мента И вЂ” НЕ ЗЗ, с выхода элемента И вЂ” ИЛИ—

НЕ 29 и с S-входа триггера), Следовательно, через время ЗТср на выходе элемента И 31 (см. А на фиг,З) будет установлен сигнал нулевого логического уровня, а на выходе

5 эл мента И 32 (А на фиг.3) — высокий логический уровень сигнала.

Контроль правильности срабатывания основных элементов вспомогательного триггера будет осуществлен следующим, образом. Через время, несколько большее, 15

1676098

16 чем ЗТср на выходе элемента И 38, появится высокий логический уровень сигнала, который является стробом сравнения третьей и четвертой групп входов элемента 7И-ИЛИ/7И-ИЛИ вЂ” НЕ 42, осуществляющих контроль правильности срабатывания логических элементов вспомогательного триггера. Если в результате срабатывания основных логических элементов вспомогательного триггера будет

10 ного триггера) сработала правильно и на прямом выходе .элемента 7И вЂ” ИЛИ/7И—

ИЛИ-НЕ 42 присутствует сигнал логического "0". При неправильном срабатывании (отказе какого-либо из основных элементов

30 вспомогательного триггера) равенство (6) нарушается и элемент 7И вЂ” ИЛИ/7И-ИЛИНЕ 42 пропускает высокий логический уровень сигнала на свой прямой выход и устанавливается в устойчивое единичное состояние, сигнализируя о возникновении

35 отказа, На выходе 52 (F) триггера любого из разрядов формируется сигнал "Отказ", означающий, что первая ступень! К-триггера сработала неправильно.

Функционирование и контроль правильности срабатывания основных логических элементов основного триггера в этом

40 режиме производится следующим образом.

По окончании действия сигнала на тактовом входе 45 и при правильном срабатывании элементов вспомогательного триггера на одном из элементов И вЂ” НЕ 33 и 34 формируется сигнал логического "0", который установит сигнал на выходе элемента И 38 в

50 одноименное состояние, что приведет к формированию высокого логического уровня сигнала на выходе элемента НЕ 39, т,е. к формированию строба сравнения через время 4Тср с момента поступления отрицательного фронта тактового сигнала.

Одновременно с этим появление сигнала логического "0" на выходе одного из элементов И-НЕ 33 и 34, а для рассматриваемого примера сигнал логического нуля присутствыполнено условие: (RS) С (3К) А = "1", (6) где R — единичный логический уровень сигнала на R-входе триггера;

S — единичный логический уровень сиг- 15 нала на S-входе триггера;

С вЂ” единичный уровень сигнала на Свходе триггера;

К вЂ” единичный уровень сигнала на Квходе триггера; 20 ! — единичный уровень сигнала на 1-входе т иггера;

- единичный уровень сигнала на выходе элемента ИЗ2, то первая ступень (элементы вспомогатель- 25 вует на выходе элемента И вЂ” НЕ 34, приведет к формированию единичного состояния на выходе элемента И-HE 36, что соответствует необходимому значению логического сигнала на выходе 50 (Q), т.е, режиму "Установка нуля". Через время 4Тср закончится переходный процесс установки в нулевое состояние сигнала на выходе элемента Y.——

НЕ 35. Таким образом, через время 4Тср с момента поступления на вход 45 триггера каждого разряда отрицательного фронта синхросигнала в основном триггере (элементы И вЂ” НЕ 35 и 36) заканчиваются переходные процессы и на первой и второй группах входов элемента 7ИИЛИ/7И вЂ” ИЛИ вЂ” НЕ 42 производится контроль состояний противоположных плеч вспомогательного и основного триггеров (сигнал в точке А с сигналом на выходе 50 и в точке А с сигналом на выходе 49). При правильном срабатывании основного триггера на прямом выходе элемента 7И—

ИЛИ/7И вЂ” ИЛИ вЂ” НЕ 42 присутствует сигнал логического нуля, в противном случае вырабатывается сигнал логической единицы, означающий отказ одного из элементов N-НЕ

35 и 36 основного триггера, В режиме установки триггера каждого разряда в "1" (табл.2, п.5) с приходом положительного фронта синхроимпульса на вход 45 (фиг.3а) производится запись единичного состояния во вспомогательный триггер и, на вермя действия синхроимпульса, основной триггер переводится в режим хранения предыдущего состояния, так как с выхода элемента НЕ 37 на входы элементов И вЂ” HE 33 и 34 поступает нулевой логический уровень сигнала, блокирующий возможное воздействие переходных процессов в логических элементах вспомогательного триггера на состояние основного триггера. Срабатывание логических элементов вспомогательного триггера производится следующим образом, При предыдущем нулевом состоянии tKтриггера на выходе элемента И вЂ” ИЛИ вЂ” НЕ

29 через время 2Тср будет сформирован нулевой логический уровень сигнала, а на выходе элемента И вЂ” ИЛИ вЂ” НЕ 30 — высокий логический уровень сигнала. В результате этого элемент И 32 закрыт нулевым уровнем сигнала с выхода элемента И вЂ” ИЛИ вЂ” НЕ 29, а элемент И 31 — открыт, т.е, через время

ЗТср, при правильном срабатывании элементов вспомогательного триггера, в точке А устанавливается высокий логический уровень сигнала, а в точке А — нулевой логический уровень сигнала.

Контроль правильности срабатывания логических элементов вспомогательного

1676098

18 триггера в этом режиме осуществляется следующим образом. Через такое же время

ЗТ,Р на выходе элемента И 38 формируется высокий логический уровень сигнала, который для пятой и шестой групп входов элемента 7И вЂ” ИЛИ/7И вЂ” ИЛИ вЂ” НЕ 42 является стробом сравнения. Если же в результате срабатывания основных элементов вспомогательного триггера будет выполнено условие: (RS) С (1К) А =- -1-, (7) где R — единичный сигнал на R-входе триггера;

S — единичное состояние сигнала íà Sвходе триггера;

С вЂ” единичный сигнал на С-входе триггера;

1 — единичный сигнал на 1-входе триггера;

К вЂ” нулевой сигнал на К- входе триггера;

А — единичный сигнал на выходе элемента И 31, то элементы вспомогательного триггера сработали правильно и на выходе элемента 7И вЂ” ИЛИ/7И вЂ” ИЛИ вЂ” НЕ 42 будет присутствовать сигнал логического "0", При неправильном срабатывании (отказе) какого-либо из основных логических элементов вспомогательного триггера равенство (7) нарушается и четвертая группа входов элемента 7И вЂ” ИЛИ/7И-ИЛИ вЂ” НЕ

42 пропускает на его прямой выход высокий логический уровень сигнала, что приводит к формированию устойчивого сигнала "Отказ" на выходе 52 триггера любого из разрядов, Функционирование и контроль правильности срабатывания основных логических элементов основного триггера в этом, режиме производится следующим образом. По окончании действия сигнала на входе 45 (фиг.3, V<) и при правильном срабатывании вспомогательного триггера элементом И вЂ” НЕ 33 формируется сигнал логического "0", который установит выходы элементов И 38 и И-НЕ 35 в соответствующие логические состояния, На выходе элемента И 38 будет сформирован сигнал логического "0", который приведет к формированию на выходе элемента HE 39 сигнала высокого логического уровня. Этот сигнал будет сформирован с задержкой на 4Tgp по отношению к моменту появления отрицательного фронта тактового импульса. На выходе элемента И-НЕ 35 также через время ЗТср сформируется сигнал логической единицы, который через время 4Тср приводит к формированию сигнала логического нуля на выходе элемента И-НЕ 36.

Таким образом, через время 4Т р на выхопредыдущем единичном состоян и появле55 ние положительного фронта синхроимпульса на входе 45 приводит к срабатыванию элемента И-ИЛИ вЂ” HE 30, на выходе которого через время 2Тср формируется сигнал нулевого логического уровня, Через время

50 дах 49 и 50 триггера будет сформированы соответственно высокий и низкий логические уровни сигналов, что будет соответствовать заданному режиму функционирования IK-триггера, т.е. режиму

"Установка "1"". Таким образом, через время 4Т Р с момента поступления на вход 45

IK-тоиггеоа отоицательного фронта тактового сигнала в основном триггере заканчиваются переходные процессы и на первой и второй группах входов элемента 7И—

ИЛИ/7И--ИЛИ вЂ” НЕ 42 по стробу сравнения с выхода элемента НЕ 39 производится контроль правильности срабатывания его логических элементов И вЂ” НЕ 35 и 36.

При правильном срабатывании на выходе (прямом) элемента 7И-ИЛИ/7И вЂ” ИЛИ вЂ” HE

42 вырабатывается сигнал логического "0", в