Последовательно-параллельный аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

Изобретение относится к устройствам автоматики, контрольно-измерительной и вычислительной техники и позволяет повысить быстродействие и надежность путем устранения чувствительности к перегрузкам . Это достигается тем, что в преобразователь , содержащий резистивный делитель 2 напряжений, блок 3 компараторов, блок 5 кодирующей логики, блок 6 коммутации, параллельный АЦП 8 младших разрядов, введены два компаратора 9 и 10, два элемента И 11 и 12, блок 4 элементов И, вычитателъ 7. 2 з.п.ф-лы, 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (5п5 Н 03 М 1/14

ГОСУДАРС: ВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

0 4

СЭ

О (21) 4718334/24 (22) 11.07.89 (46) 07.09.91. Бюл. М 33 (71) Научно-производственное обьединение

"Вента" (72) Р.3. Курыло (53) 681.325(088,8) (56) ElectronlcLetters, 1985, N- 6, р.235, fig.7.

Бахтияров Г.Д, Аналого-цифровые преобразователи. — M.: Сов.радио, 1980, с.198199, рис.7.23 (прототип), (54) ПОСЛЕДОВАТЕЛЬНО-ПАРАЛЛЕЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

„„Я2„„1676100 А1 (57) Изобретение относится к устройствам автоматики, контрольно-измерительной и вычислительной техники и позволяет повыси-,ь быстродействие и надежность путем устранения чувствительности к перегрузкам. Это достигается тем, что в преобразователь, содержащий резистивный делитель

2 напряжений, блок 3 компараторов, блок 5 кодирующей логики, блок 6 коммутации, параллельный АЦП 8 младших разрядов, введены два компаратора 9 и 10, два элемента

И 11 и 12, блок 4 элементов И, вычитатель 7.

2 з.п.ф-лы, 2 ил, !

1676100

Изобретение относится к устройствам автоматики, контрольно-измерительной и вычислительной техники, а именно к быстродействующим аналого-цифровым преобразователям. 5

Целью изобретения является повышение быстродействия и надежности путем устранения чувствительности к перегрузкам.

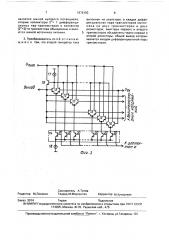

На фиг,1 представлена структурная схема последовательно-параллельного АЦП; 10 на фиг.2 — структурная схема блока коммутации, Преобразователь содержит параллельный аналого-цифровои преобразователь 1 (АЦП) старших разрядов, состоящий из ре- 15 зистивного делителя 2 напряжения, блока 3 компараторов, блока 4 элементов И и блока

5 кодирующей логики, блок 6 коммутации, вычитатель 7, параллельный АЦП 8 младших разрядов, компараторы 9 и 10, эле- 20 менты И 11 и 12, Блок коммутации (фиг.2) содержит 2"-1 дифференциальных 13 транзисторов, переключатель 14 тока, дИфференциальные пары 15 и 16 транзисторов, генераторы 17 и 18 25 токов, транзистор 19, переключатель 14 содержит транзисторы 20.

Генератор 17 может быть заменен резистором, включенным между шиной питания . и точкой соединения коллекторов транзи- 30 сторов первого плеча дифференциальных пар 13, 16 и 17, в этом случае эмиттеры транзисторов дифференциальных пар необходимо подключить к коллекторам транзисторов 20 через резисторы.

Последовательно-параллельный АЦП работает следующим образом.

Выходной аналоговый сигнал блоком 3 сравнивается с сеткой опорных напряже- 40 ний резистивного делителя 2, при этом на выходах блока 3 образуется термометрический код, на прямых выходах сработавших компараторов имеетс уровень логической

"1", а на прямых выходах остальных компараторов имеется уровень логического "0", Соответственно на инверсных выходах компараторов имеются уровни логических "0" и

"1". Термометрический код с выходов блока

3 подается на входы блока 4 таким образом, что на один логический элемент И подаются сигналы с прямого и инверсного выходов двух смежных компараторов. Злемент И образует на выходе уровень логической "1", когда логические уровни сигналов на его входах совпадают, либо уровень логического "0", когда логические уровни сигналов на его входах не совпадают, Таким образом, логическая "1" образуется только на выходе элемента И, соответствующего последнему сработавшему компаратору, на выходах остальных логических элементов имеется уровень логического "0", Данный унитарный цифровой код с выхода блока 4 подается на блок 5, где он преобразуется в позиционный двоичный код старших разрядов и на управляющие входы блока 6, открывая один из транзисторов 20 переключателя 14, остальные транзисторы переключателя 14 остаются закрытыми. Если входной сигнал имеет значение, ограниченное напряжениями источников опорных напряжений Uon) и Uon2, переключатель 14 тока включает одну из дифференциальных пар 13, а именно ту, которая подключена базой одного из транзисторов к опорному напряжению последнего сработавшего компаратора на резистивном делителе 2, открывая цепь для протекания токов генераторов 17 и 18 через данную дифференциальную пару транзисторов.

Величина тока генератора 17 меньше величины тока генератора 18, эти величины выбраны таким образом, что величины коллекторов первого и второго плечей дифференциальных пар 13 равны при одинаковых потенциалах без транзисторов. Дифференциальная пара 13 транзисторов вместе с транзистором 19 образует повторитель напряжения, который при одинаковых параметрах транзисторов обоих плеч дифференциальных пар точно повторяет на выходе входное напряжение, т,е. опорное напряжение конкретной точки резистивного делителя 2, В змиттерные цепи дифференциальных пар 13 транзисторов могут быть включены резисторы для балансировки дифференциальной пары. При изменении входного напряжения АЦП поочередно включаются (выключаются) все новые компараторы и на выходе блока 6 образуется ступенчатое напряжение, которое одновременно с входным сигналом поступает на вычитатель 7. Разностный сигнал с выхода вычитателя 7 поступает на параллельный

АЦП 8 младших разрядов, где он преобразуется в позиционный двоичный код младших разрядов АЦП, Если значение входного сигнала выходит за пределы, ограниченные значениями напряжений U«> и U»2, аналогично описанному выше срабатывают компараторы

9 или 10 и элементы 11 и 12. На выходе элемента 11 и 12 образуется уровень логической "1", при этом на выходах блока 4 образуются уровни логических "0", Напряжение логической "1" с выхода элементов

11 или 12, минуя блок 5, подается на вход блока 6, включая транзистор переключателя 14 тока, управляющий включением

1676100

35

45 ются выходной шиной старших разрядов ко- 50 да, аналого-цифровой преобразователь младших разрядов кода, выходы которого являются выходной шиной младших разрядов кода, отличающийся тем, что, с

55 дифференциальной пары 15 или 16 в зависимости от того, за предел которого из опорных напряжений значение входного сигнала. Дифференциальные пары 15 и 16 транзисторов отличаются от дифференциальных пар 13 лишь тем, что базы транзисторов вторых плеч дифференциальных пар

15 и 16 подключены не к резистивному делителю 2 опорных напряжений, как у пар 13, а к входу АЦП. Поэтому при включении диф- ференциальных пар 15 и 16 транзисторов, что происходит в случае ухода входного напряжения АЦП за пределы, установленные напряжениями 4л1и Upnz, на выходе блока появляется напряжение. равное входному напряжению. Передаточная характеристика блока 6 состоит из трех участков: линейного, где Ueblx = Uex при Овх < 0оп1; ступенчатого при Ооп1 Ов 0оп2 и линейного Ue x = Uex npu Uex > Uon Это обеспечивает максимальное дифференциальное напряжение на входе вычитателя 7, равное величине кванта напряжения АЦП 1 старших разрядов, и исключает перегрузку вычитателя. В случае замены генератора

17 резистором АЦП может быть достигнуто большее быстродействие за счет более короткого процесса установления напряжения на выходе блока 6. Однако, в данном случае не выполняется условие равенства коллекторных токов в транзисторах дифференциальных пар 13, 16 и 17, вследствие чего на выходе блока 6 образуется погрешность, для компенсации которой в эмиттерные цепи транзисторов дифференциальных пар вводятся резисторы и уменьшение по-! грешности обеспечивается подбором или подгонкой их номиналов.

Формула изобретения

1. Последовательно-параллельный аналого-цифровой преобразователь, содержащий резистивный делитель напряжения, первый вход которого является первой шиной опорного напряжения, а выходы соединены с соответствующими первыми входами блока компараторов и блока коммутации, вторые входы которых объединены и являются входной шиной, блок кодирующей логики, выходы которого явля целью повышения быстродействия и надежности путем устранения чувствительности к перегрузкам, в него введены два компаратора, блок элементов И, два элемента И и вычитатель, первый вход которого является

25 входной шиной, второй вход соединен с выходом блока коммутации, а выход — с входом аналого-цифрового преобразователя младших разрядов, третий и четвертый входы блока коммутации соединены соответственно с выходами первого и второго элементов

И, пятые входы объединены с соответствующими входами блока кодирующей логики и соединены с соответствующими выходами блока элементов И, первые входы которого соединены соответственно с первыми выходами блока компараторов, второй вход — с инверсным выходом первого компаратора, прямой выход которого соединен с первым входом первого элемента И, второй вход которого является шиной логической единицы, первый вход первого компаратора объединен с вторым входом резистивного делителя напряжения и является второй шиной опорного напряжения, второй вход объединен с первым входом второго компаратора и является входной шиной, второй вход второго компаратора обьединен с первым входом резистивного делителя напряжения, а прямой выход соединен с первым входом второго элемента И, второй вход которого соединен с вторым выходом блока компараторов.

2. Преобразователь по п.1, о т л и ч а юшийся тем, что блок коммутации выполнен на 2 "+1 дифференциальных парах транзисторов, где n — число старших разрядов преобразователя, 2"+2 транзисторах и двух генераторах тока, первый выход первого генератора тока является шиной нулевого потенциала, а второй выход соединен с эмиттерами 2" транзисторов, база первого транзистора является третьим входом блока. базы транзисторов с второго

П по 2 -й являются пятыми входами блока, база (2 "+1}-го транзистора является четвертым входом блока, коллекторы 2" транзисторов соединены соответственно с входами 2" дифференциальных пар транзисторов эмиттеры которых явля ются входом каждой дифференциальной базы транзисторов, первые базы первой и (2 "+1)-й дифференциальной пары транзисторов объединены и являются вторым входом блока, первые базы со второй по 2"-ю дифференциальных пар транзисторов являются соответственно первыми входами блока, вторые базы 2"+ 1 дифференциальных пар транзисторов объединены с змиттером (2"+ 2)-го транзистора и являются выходом блока, первые коллекторы 2 "+1 дифференциальных пар транзисторов обьединены с базой (2 "+2)-го транзистора и соединены с первым выходом второго генератора тока, второй выход которого

1676100

3. Преобразователь по п.2, о т л и ч а юшийся тем, что второй генератор тока

13

8ьиОд

ЮЛЮМЮН081 И

Составитель А,Титов

Техред М.Моргентал Корректор М, Кучерявая

Редактор M.Ëикович

Заказ 3014 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб„4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул,Гагарина, 101 является шиной нулевого потенциала, вторые коллекторы 2 "+ 1 дифференциальных пар транзисторов и коллектор (2"+2)-го транзистора объединены и являются шиной источника питания. выполнен на резисторе. а каждая дифференциальная пара транзисторов выполнена на двух транзисторах и двух резисторах, эмиттеры первого и второго

5 транзисторов объединены через первый и второй резисторы, общий вывод которых является входом дифференциальной пары транзисторов,