Устройство тактовой синхронизации

Иллюстрации

Показать всеРеферат

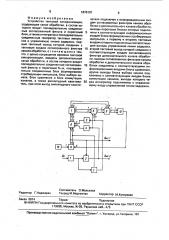

Изобретение относится к электросвязи. Цель изобретения - сокращение времени тактовой синхронизации. Устройство содержит амплитудный квантователь 1, каналы обработки, состоящие из согласованных фильтров 2 и 3 и пороговых блоков 4 и 5, а также блок 6 формирования стробирующих импульсов, блок 7 выбора канала, блок 8 сравнения, блок 9 коммутации каналов, интегратор 10, управляемую линию 11 задержки и генератор 12 тактовых импульсов. Аналоговый сигнал из системы связи преобразуется квантователем 1 в кодовые посылки. Каждая посылка представляет собой псевдослучайную последовательность (ПСП) длиной в N элементов. Из этих ПСП каналы обработки формируют сжатые сигналы, величина которых зависит от отношения сигнала к шуму в канале связи и от того, попадают ли тактовые импульсы на фронты или плоские части элементов входного сигнала. Цель достигается за счет обеспечения формирования заданной величины задержки тактовых импульсов. При этом минимальный шаг задержки в несколько раз меньше величины элемента ПСП. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК ((9) (1() (ss)s Н 04 1 7/02

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

I в

ОПИСАНИЕ ИЗОБРЕТЕНИЕ: -::- ..:;;- "

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4450284/09 (22) 27,06.88 (46) 07,09,91. Бюл, М 33. (72) Л.M.Ãoðþíoâà, Ю,С,Парижский, И.Н.Ти.това и А.Н.Шполянский (53) 621.394.662(088.8) (56) Авторское свидетельство СССР

М 1596473, кл. Н 04 L 7/02, 1988, (54) УСТРОЙСТВО ТАКТОВОЙ СИНХРОНИЗАЦИИ (57) Изобретение относится к электросвязи.

Цель изобретения — сокращение времени тактовой синхронизации. Устройство содержит амплитудный квантователь 1, каналы обработки, состоящие из согласованных фильтров 2 и 3 и пороговых блоков 4 и 5, а также блок 6 формирования стробирующих импульсов, блок 7 выбора канала, блок 8

Изобретение относится к технике электросвязи и может быть использовано для тактовой синхронизации в системах связи с фазовой манипуляцией или относительной фазовой манипуляцией и сжатием сигнала.

Целью изобретения является сокращение времени синхронизации, На чертеже приведена структурная схема устройства тактовой синхронизации.

Устройство. тактовой синхронизации содержит амплитудный квантователь (АК) 1, каналы обработки содержат соответственно согласованные фильтры (СФ) 2 и 3 и пороговые блоки 4 и 5, блок 6 формирования стробирующих импульсов, блок 7 выбора канала, блок 8 сравнения, блок 9 коммутации каналов, интегратор 10, управсравнения, блок 9 коммутации каналов, интегратор 10, управляемую линию 11 задержки и генератор 12 тактовых импульсов, Аналоговый сигнал из системы связи преобразуется квантователем 1 в кодовые посылки. Каждая посылка представляет собой псевдослучайную последовательность (ПСП) длиной в N элементов. Из этих

ПСП каналы обработки формируют сжатые сигналы, величина которых зависит от отношения сигнала к шуму в канале связи и от того, попадают ли тактовые импульсы на фронты или плоские части элементов входного сигнала. Цель достигается за счет обеспечения формирования заданной величины задержки тактовых импульсов. При этом минимальный шаг задержки в несколько раз меньше величины элемента ПСП. 1 ил. ляемую линию задержки (УЛ3) 11, генератор

12 тактовых импульсов.

Устройство тактовой синхронизации работает следующим образом, До подачи информационных слов на вход устройства из системы связи поступает аналоговый сигнал, который преобразуется амплитудным квантователем 1 в кодовые посылки. Каждая посылка представляет собой псевдослучайную последовательность (ПСП) длиной в N элементов.

Каждый элемент ПСП имеет одно из двух возможных значений "0" или "1" в течение времени, равного одному такту. Эти последовательности поступают на входы СФ 2 и

3. Работа СФ 2 и 3 управляется тактовыми импульсами, поступающими с выхода УЛЗ

1676107

11 и сдвинутыми относител1 но друг друга на полпериода тактовой частоты.

Сдвиги тактовых импульсов осуществляются с целью обеспечения минимальных потерь информации при приеме ПСП с нроизвольным начальным временным положением элементов.

На выходах СФ 2 и 3 формируются сжатые сигналы, величина которых зависит от отношения сигнала к шуму е канале связи и от того, попадают на тактовые импульсы на фронты или плоские части:иементов входного сигнала, Полярность сжатого сигнала на выходах

СФ 2 и 3 зависит от начальной фазы ехоцного сигнала и может быть как положительной, так и отрицательной. Сжатые сигналы сравниваются, соответственно, в пороговых блоках 4 и 5 с порогами, одинаковыми по величине и противоположными по знаку, Пороги выбираются таким образом, чтобы вероятность превышения порога лумом составляла величину порядка 0,1 — 0,2, что соответствует, например, величине порога

20 — 25 при максимальном сигнале на выходе фильтра, равном 127. H случае превышения сжатым сигналом порог" по величине на выходах пороговых блоков 4 и 5 вырабатываются сигналы логиче:кой . единицы превышения порога, которые поступают на информационные входы блока

6. На тактовые входы блока 6 с выхода УЛЗ

11 поступают последовательности тактовых импульсов.

Стробирующий импульс, совпадающий во времени с моментом превышения порога, может AQ5IBMTbcR только на одном иэ выходов блока 6. При этом на первом выходе стробирующий импульс появляется, если превышение порога произошло только в пороговом блоке 5, или в пороговых блоках 4 и 5, но в пороговом блоке 5 раньше, чем в пороговом блоке 4, На втором выхоце блока 6 стробирующий импульс появляется, если превышение порога произошло только в пороговом блоке 4 или в пороговом блоке 4 раньше, чем е пороговом блоке 5.

Стробирующий импульс с первого или второго выхода блока 6 поступает на соответствующий вход блока 7, где формируются сигналы управления для блока 9 (выходы

1 и 2) и сигналы записи для блока 8 (выходы

3 и 4 блока 7).

Логика работы блока 7 следующая. Если сформировался сигнал на первом входе блока 7, то на его первом выходе появляется сигнал логической единицы, на втором выходе — сигнал логического нуля, а на третьем и четвертом выходах формируют5

5Я ся импульсы, причем на третьем выходе раньше, чем импульс на четвертом выходе блока 7 на столько же, на сколько сжатый сигнал первого канала с СФ 2 опережает сжатый сигнал второго канала с СФ 3,Если сформировался сигнал на втором входе блока 7, то на его первом выходе появляется сигнал логического нуля, на втором выходе сигнал логической единицы, а на третьем выходе формируется импульс позже, чем импульс на четвертом выходе блока 7 на столько же, на сколько сжатый сигнал первого канала СФ 2 отстает от сжатого сигнала второго канала с СФ 3. Сжатые сигналы двух каналов, поступающие на третий и четвертый входы блока 8, записываются по сигналам записи, поступающим на первый и второй входы блока 8, и сравниваются по величине этим блоком, На первом выходе блока 8 появляется сигнал логической единицы, если сжатый сигнал первого канала с СФ 2 больше, чем сжатый сигнал второго канала с СФ 3. В противном случае появляется сигнал логической единицы на втором выходе блока 8. Сигналы с первого и второго выходов блока 8 поступают на информационные входы блока 9 и коммутируются на вход интегратора е зависимости от управляющих сигналов, поступающих на третий и четвертый входы блока 9, Правило коммутации е блоке 9 следующее, Импульс на первом выходе блока 9 появляетсяя в двух случаях: если сжатый сигнал первого канала на выходе СФ 2 появился раньше и амплитудное его значение меньше, чем у сжатого сигнала второго канала на выходе СФ 3, если сжатый сигнал второго канала появился раньше и амплитудное его значение меньше, чем у сжатого сигнала первого канала.

Импульс на втором выходе блока 9 появляется в двух противоположных случаях.

Сигналы первого и второго выходов блока

9 поступают на соответствующие входы интегратора 10. Если импульс появляется на первом входе интегратора 10, то интегратор увеличивает свое значение на 1, если импульс появляется на втором входе интегратора 10, то интегратор уменьшает свое значение на 1.

Сигнал, накопленный интегратором

10, поступает на управляющий вход УЛЗ

11, на информационный вход которой поступают импульсы с выхода генератора 12.

Величина задержки импульсов определяется значением сигнала на управляющем входе, причем минимальный шаг задержки в несколько раз меньше величины элемента ПСП, 1676107

Составитель О.Мелькова

Редактор Г.Наджарян Техред М.Моргентал Корректор M.Кучерявая

Заказ 3014 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул.Гагарина, 101

Формула изобретения

Устройство тактовой синхронизации, содержащее канал обработки, в состав которого входят последовательно соединенные согласованный фильтр и пороговый блок, а также интегратор и последовательно соединенные генератор тактовых импульсов и управляемую линию задержки, первый тактовый выход которой соединен с тактовым входом согласованного фильтра канала обработки, о т л и ч а ю щ е е с я тем, что, с целью сокращения времени тактовой синхронизации, введены дополнительный канал обработки, в состав которого входят последовательно соединенные согласованный фильтр и пороговый блок, последовательно соединенные блок формирования стробирующих импульсов, блок выбора канала, блок сравнения и блок коммутации каналов, а также амплитудный квантователь, при атом выход амплитудного квантователя подключен к информационным входам согласованных фильтров канала обработки и дополнительного канала обработки, выходы пороговых блоков которых подклю5 чены к соответствующим информационным входам блока формирования стробирующих импульсов, к первому и второму тактовым входам которого подключены соответствующие выходы управляемой линии задержки, 10 второй тактовый выход которой соединен с соответствующим входом согласованного фильтра дополнительного канала обработки, выходы согласованных фильтров канала обработки и дополнительного канала обра15 ботки соединены с соответствующими информационными входами блока сравнения, другие выходы блока выбора канала подключены к соответствующим входам блока коммутации каналов, выходы которого че20 рез интегратор подключены к управляющему входу управляемой линии задержки.