Управляемый делитель частоты с дробным коэффициентом деления

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники и в синтезаторах частоты Цель изобретения - повышение быстродействия при одновременном повышении надежности работы - обеспечивается путем введения в устройство ЗК-триггера 4, инвертора 9, элемента ИЛИ-НЕ 10, D-триггера 11 и образования новых функциональных связей. Кроме того, делитель частоты содержит счетчик 1 импульсов , элемент И 3, накапливающий сумматор 2, шины 7,5,6 и 8 входную, первую кодовую, вторую кодовую и выходную соответственно , 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„5U „„1677870А1 (я>л Н 03 К 23/66

ГОСУДАРСТВЕННЫ И КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ,. :

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

4 (21) 4703923/21 (22) 12.06,89 (46) 15.09,91. Бюл, hL 34 (72) В,Г.Аристов и В.С,Семенов (53) 621.374.4(088.8) (56) Авторское свидетельство СССР

М 1298908, кл. Н 03 К 23/66, 14.08.85.

Авторское свидетельство СССР

N 656216, кл. Н 03 К 23/68, 04.06.76. (54) УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ С

ДРОБНЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ (57) Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники и в синтезаторах частоты. Цель изобретения повышение быстродействия при одновременном повышении надежности работы— обеспечивается путем введения в устройство 3К-триггера 4, инвертора 9, элемента

ИЛИ вЂ” НЕ 10, D-триггера 11 и образования новых функциональных связей. Кроме того, делитель частоты содержит счетчик 1 импульсов, элемент И 3, накапливающий сумматор 2, шины 7,5,6 и 8 входную, первую кодовую, вторую кодовую и выходную соответственно, 2 ил.

1677870

Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники и синтезаторах частоты.

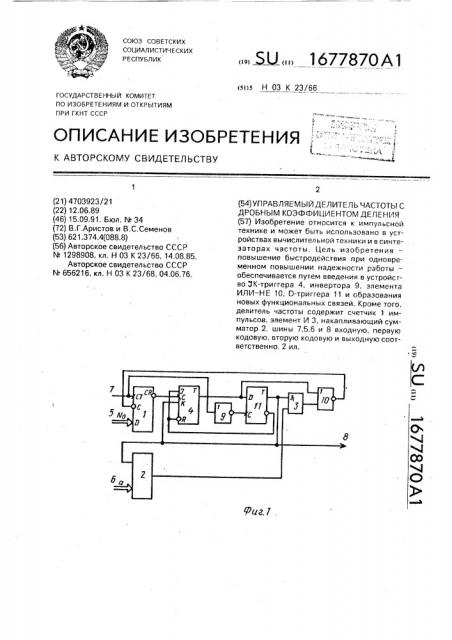

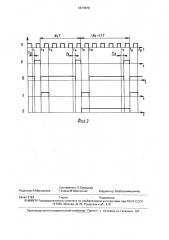

Цель изобретения — повышение быстродействия при одновременном повышении надежности работы, На фиг,1 приведена электрическая структурная схема делителя; на фиг.2 — временныее диаграммы, поясняющие его работу (2а — временная диаграмма частоты входного сигнала, поступающего на вход 7 делителя; 2б —.временная диаграмма на выходе

J К-триггера 4; 2в — то же, на С-входе записи параллельного кода счетчика 1; 2г — то же, прямого выхода D-триггера 11; 2д — то же, на выходе накапливающего сумматора 2).

Управляемый делитель частоты с дробным коэффициентом деления содержит счетчик 1 импульсов, накапливающий сумматор 2, выход переполнения которого соединен с первым входом элемента И 3, JK-триггер 4, первую и вторую кодовые шины 5 и 6, входную шину 7, выходную шину 8, инвертор 9, элемент ИЛИ вЂ” НЕ 10, D-триггер

11; счетный вход счетчика 1 импульсов соединен с входной шиной 7 и входом инвертора 9, выход которого соединен с С-входом

D-триггера 11, информационные входы счетчика 1: импульсов соединены с первой кодовой шиной 5, вход разрешения записи — с выходом элемента ИЛИ вЂ” НЕ 10, первый вход которого соединен с прямым выходом

J К-триггера 4 и D-входом D-триггера 11, инверсный выход которого соединен cd-входом и R-входом JK-триггера 4, С -вход которого соединен с выходом переноса счетчика 1 импульсов, прямой выход 0-триггера 11 соединен с вторым входом элемента

И 3; К-входом JK-триггера 4, выходной шиной 8 и тактовым входом накапливающего сумматора 2, информационные входы кото. рого соединены с второй кодовой шиной 6; выход элемента И 3 соединен с вторым входом элемента ИЛИ вЂ” НЕ 10.

Делитель работает следующим образом, Под действием импульсов (фиг,2а), поступающих по входной шине 7 на счетный вход СТ счетчика 1, осуществляется обычный их пересчет в режиме сложения, После пересчета N импульсов счетчик 1 устанавливается в единичное состояние, и в момент времени t< Hà его выходе CR переноса появляется нулевой уровень, который воздействует на С-вход синхронизации JK-триггера

4, устанавливая его выход в единичное состояние (фиг.26), Этот сигнал поступает на элемент ИЛИ вЂ” НЕ 10, с выхода которого воздействует в виде нулевого уровня (фиг.2в) на

С-вход записи параллельного кода счетчика

1. Параллельный код, равный коэффициенту пересчета К, поступает на 0-входы счетчика

1 по кодовой шине 5. Двоичный код коэффициента пересчета К, соответствующий устанавливаемому коэффициенту деления целой части No, определяется следующим выражением:

К=2 -No, где m — число разрядов счетчика, На фиг.2 приведены временные диаграммы деления частоты при No = 5, После окончания следующего импульса входного сигнала в момент времени t2 осуществляется установка прямого выхода Dтриггера 11 в "1" (фиг.2г), а инверсного — в

"0". Нулевой уровень инверсного выхода Отриггера 11 воздействует на инверсный Rвход и J-вход JK-триггера 4, его выход устанавливается в "0". Одновременно прекращается запись параллельного кода в счетчик 1 и с этого момента вновь осуществляется пересчет входных импульсов, поступающих на счетный вход СТ счетчика 1, Единичный уровень прямого выхода Dтриггера 11 с момента времени t2 поступает на выходную шину 8 и тактовый вход накапливающего сумматора 2, имеющего емкость

М. Содержимое накапливающего сумматора 2 увеличивается с каждым тактом на величину а поступающего по кодовой шине 6 установки дробной части коэффициента деления.

После окончания следующего импульса входного сигнала в момент времени tz выключается D-триггер 11 (фиг.2г), т.е. на его прямом выходе появляется нулевой, а на инверсном — единичный уровень, Одновременно с выключением D-триггера 11 прекращается формирование импульса выходного сигнала. Путем пересчета импульсов на интервале (A — t5) осуществляется деление входной части на целую часть коэффициента деления, равного значению двоичного кода No, поступающего по кодовой шине 5 на 0-входы счетчика 1. Длительность интервала (t2, t5) равна NoT, где Т вЂ” период входной частоты.

Если очередное значение о), записываемое в накапливающий сумматор 2, равно или превышает емкость М сумматороа, он переполняется и коэффициент деления устройства становится равным N>+1 на время одного цикла деления.

Так, например, после пересчета осуществляется последовательное взведение ЗКтриггера 4 в момент времени t4, затем

Р-триггера 11 в момент времени сэ, единичный уровень которого, воздействуя на так1677870 товый вход накапливающего сумматора 2, вызывает его переполнение и появление единичного уровня на его выходе (фиг,2д), При этом в результате совпадения единичных уровней с прямого выхода 0-триггера 5

11 и с выхода накапливающего сумматора 2 на интервале (т5дв) происходит увеличение длительности отрицательного импульса на

С-входе записи параллельного кода счетчика 1 (фиг.2в) на время, равное периоду вход- 10 ной частоты. Коэффициент деления на интервале (ts,tâ) становится равным No+1.

Длительность интервала (ts,te) равна (Но+1)» х Т, После пересчета No+1 импульсов вновь осуществляется последовательное возведе- 15 ние в момент времени тт JK-триггера 4, а в момент времени тв -0-триггера 11, единичный уровень которого, воздействуя на тактовый вход накапливающего сумматора 2, вызывает занесение в накапливающий сум- 20 матор 2 значения 6l = q> + а< M. В этом случае число 6l, записываемое в накапливающий сумматор 2, не вызывает его переполнения и на его выходе устанавливается нулевой уровень (фиг.2д). С приходом следу- 25 ющего импульса входного сигнала в момент времени tg происходит выключение D-триггера 11 (фиг.2г), т.е. на его прямом выходе появляется нулевой, а на инверсном — единичный уровень. 30

B момент tg переполнения накапливающего сумматора 2 (фиг.2д) фактически записываемое в него число q1= Й -М, т.е. оно меньше предыдущего значения, равного б -а, нэ величину M — а. Дальнейшее измене- 35 ние кода в накапливающем сумматоре 2 происходит начиная со значения рь

Так как из М циклов деления а раз устанавливается коэффициент No+1 и (М вЂ” а) раз — коэффициент No, средний коэффициент 40 деления равен

No+1 .a+No M-a „+ а

Ф

+М

Если M = 2", где л — целое число, равное количеству разрядов накапливающего сум- 45 матора 2, то N представляет собой двоичную дробь, Предлагаемый делитель, обладающий повышенными быстродействием и стабильностью работы, может быть построен на низкочастотных элементах, так как время задержки тз импульса переноса на выходе

CR счетчика 1, а следовательно, и срабатывание J К-триггера 11 может достигать более половины периода входной частоты (фиг.2б) без нарушения работы делителя, Дробность в предлагаемом делителе достигается путем коррекции выходной частоты с помощью дополнительного воздействия 0-триггера 11 и накапливающего сумматора 2 через элементы И 3 и ИЛИ вЂ” НЕ

10 на С-вход записи параллельного кода счетчика 1, Эти особенности предлагаемого делителя обеспечивают значительное повышение быстродействия и стабильности его работы.

Формула изобретения

Управляемый делитель частоты с дробным коэффициентом деления, содержащий счетчик импульсов, накапливающий сумматор, выход переполнения которого соединен с первым входом элемента И, первый триггер, первую и вторую кодовые шины, входную и выходную шины, отличающийся тем, что, с целью повышения быстродействия при одновременном повышении надежности работы, в качестве первого триггера используется.lK-триггер и введены инвертор, элемент ИЛИ вЂ” НЕ, второй триггер, в качестве которого используется D-триггер, причем счетный вход счетчика импульсов соединен с входной шиной и входом инвертора, выход которого соединен с С-входом второго триггера, информационные входы счетчика импульсов соединены .с первой кодовой шиной, вход разрешения записи — с выходом элемента ИЛИ вЂ” НЕ, первый вход которого соединен с прямым выходом первого триггера и 0-входом второго триггера, инверсный выход которого соединен с J-входом и R-входом первого триггера, С-вход которого соединен с выходом переноса счетчика импульсов, прямой выход второго триггера соединен с вторым входом элемента И, К-входом первого триггера, выходной шиной и тактовым входом накапливающего сумматора, информационные входы которого соединены со второй кодовой шиной, а выход элемента И соединен с вторым входом элемента ИЛИ-НЕ.

1677870

Составитель Л, Клевцова

Техред М.Моргентал Корректор М.Максимишинец

Редактор А.Маковская

Производственно-издательский комбинат Патент", г. Ужгород, ул.Гагарина, 101

Заказ 3123 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5