Устройство для вывода информации

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике Цель изобретения - повышение быстродействия устройства за счет уменьшения в нем времени прохождения сигнала считывания . Для этого в устройство, содержащее регистры 1, 2. триггеры 3, 6, элемент 4 И и элемент задержки 5, введены элемент И 7 и элемент ИЛИ 8 Устройство обеспечивает прием входной информации и выдачу ее на выход в зависимости от тактового сигнала и сигнала считывания 1 ил.

СО1ОЗ CORE ТСКИХ

COI IVIA11ИС 1 И II СКИХ

РE С.I!УБ11ИК (sI)s G 06 F 3/00

ГОСУДАРСТБЕН11ЫИ КОМИТЕТ

I1o иэОБРГтениям и ОткРытиям

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4730494/24 (22) 18.08.89 (46) 23.09.91. Бюл. № 35 (72) С.Г.Диденко (53) 681.327 (088.8) (56) Авторское свидетельство СССР

¹ 1451672, кл, 6 06 Г 3/00, 1987.

Авторское свидетельство СССР

¹ 11224411222211,, кКл, G 06 F 3/00, 1984.

Авторское свидетельство СССР № 651336, кл. G 06 F 3/02, 1977.

„„5U ÄÄ 1679480 А1 (54) УСТРОЙСТВО ДЛЯ ВЫВОДА ИНФОРМАЦИИ (57) Изобретение относится к вычислительной технике. Цель изобретения — повышение быстродействия устройства за счет уменьшения в нем времени прохождения сигнала считывания. Для этого в устройство, содержащее регистры 1, 2, триггеры 3, 6, элемент 4 И и элемент задержки 5, введены элемент И 7 и элемент LlflVi 8. Устройство обеспечивает прием входной информации и выдачу ее на выход в зависимости от тактового сигнала и сигнала считывания. 1 ил, 1679480

Изобретение относится к вычислительной технике и предназначено для вывода информации с запоминающих устройств.

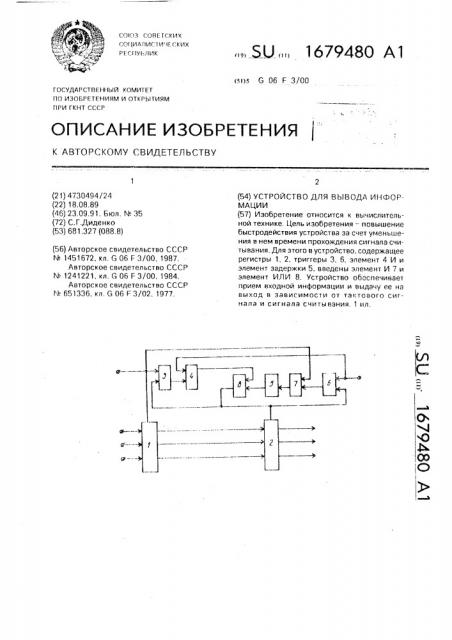

Целью изобретения является повышение быстродействия устройства, На чертеже приведена схема предлагаемого устройства.

Устройство содержит первый 1 и второй

2 регистры, первый триггер 3, первый элемент И 4, элемент 5 задержки, второй триггер б, второй элемент И 7 и элемент ИЛИ 8, Устройство работает следующим образом, П редполжим, что в исходном состоянии регистры 1 и 2 и триггеры 3 и б находятся в нулевом состоянии. Во всех точках схемы присутствуют низкие уровни напряжения.

Сигналы информации поступают на информационные входы регистра 1, Одновременно тактовый сигнал поступает на вход записи регистра 1, на первый вход триггера

3 и на первый вход элемента И 7, При этом информация записывается в регистр 1, а триггер 3 устанавливается в единичное состояние и высокий уровень напряжения с его выхода поступает на второй вход элемента И 4, На выход элемента И 7 тактовый сигнал не проходит, так как на втором входе элемента И 7 присутствует низкий уровень напряжения, поступающий с выхода триггера 6, Таким образом, устройство перешло в состояние ожидания сигнала считывания.

Сигнал считывания поступает на первый вход элемента И 4, который пропускает его на свой выход, и на первый вход триггера б, устанавливая его в единичное состояние, С выхода элемента И 4 импульс записи через элемент ИЛИ 8 поступает на вход записи регистра 2 и на вторые входы триггеров 3 и

6. В результате информация из регистра 1 переписывается в регистр 2, поступая на выходы устройства, а триггеры 3 и 6 устанавливаются в исходное состояние — нулевое, Таким образом, время прохождения сигнала считывания от входа устройства до входа записи регистра 2 равно суммарному времени задержки элементов И 4 и ИЛИ 8, В устройстве возможен также режим работы, при котором импульс считывания поступает на вход устройства ранее, чем тактовый сигнал от ЗУ, В этом случае им15

50 пульс считывания поступает на первый вход элемента И 4 и первый вход триггера б, устанавливая его в единичное состояние. На выход элемента И 4 импульс считывания не проходит, так как на втором входе элемента

И 4 присутствует низкий уровень напряжения, поступающий с выхода триггера 3, С приходом от ЭУ тактового сигнала, поступающего на вход записи регистра 1, на первый вход триггера 3 и на первый вход элемента

И 7, информация от ЗУ записывается s регистр 1, триггер 3 устанавливается в единичное состояние, а тактовый импульс через элемент И 7, элемент задержки и элемент

ИЛИ 8 поступает на вход записи регистра 2 и на вторые входы триггеров 3 и 6. На информационных входах регистра 2 к этому моменту (за счет элемента задержки) установилась информация, записанная в регистр 1.

Информация из регистра 1 переписывается в регистр 2 и поступает на выходы устройства, а триггеры 3 и б устанавливаются в исходное нулевое состояние.

Формула изобретения

Устройство для вывода информации, содержащее первый и второй регистры, первый и второй триггеры, первый элемент И, элемент задержки, информационные входы первого регистра являются информационными входами устройства, выходы первого регистра соединены с информационными входами второго регистра, выходы которого являются выходами устройства, первый вход первого триггера является тактовым входом устройства, о т л и ч а ю щ е е с я тем. что, с целью повышения быстродействия, в устройство введены второй элемент И, элемент ИЛИ, причем первый вход второго элемента И соединен с входом записи первого регистра и тактовым входом устройства, первый вход второго триггера — с первым входом первого элемента И и является входом считывания устройства, выход первого триггера подключен к второму входу первого элемента И, выход которого соединен с первым входом элемента ИЛИ, выход которого соединен с вторыми входами первого и второго триггеров и входом записи второго регистра, выход второго триггера подключен к второму входу второго элемента И, выход которого через элемент задержки соединен с вторым входом элемента ИЛИ.