Устройство контроля интерфейса

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и предназначено для контроля интерфейса ЭВМ. Цель изобретения -повышение достоверности передачи и расширение диагностических возможностей устройства за счет обеспечения записи и считывания эталонной информации из устройства . Последнее содержит три буферных усилителя, два регистра, три элемента ИЛИ, элемент И, блок дешифрации, D-триггер. 6 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)з G 06 F 11/00, 13/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4634052/24 (22) 09,01.89 (46) 23.09.91. Бюл, ¹ 35 (72) В.В. Меркуль, А.В, Олейник и Л.В, Пронько (53) 681.3(088.8) (56) Повторитель сигналов канала. Средства расширения вычислительных комплексов.—

Микропроцессорные средства и системы, 1985, N 2.

Патент ФРГ N 2758023, кл. G 06 F 13/00, опублик. 1980.

Изобретение относится к вычислительной технике и предназначено для контроля интерфейса ЭВМ, Целью изобретения является повышение достоверности передачи и расширение диагностических возможностей устройства.

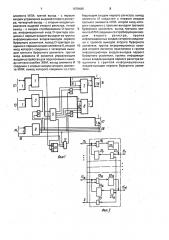

На фиг, 1 изображена блок-схема устройства контроля интерфейса; на фиг. 2— первый буферный усилитель; на фиг. 3— первый регистр; на фиг. 4 — блок дешифрации; на фиг. 5 — второй регистр; на фиг, 6— алгоритм программного диагностирования расширенного интерфейса.

Устройство контроля расширенного интерфейса (фиг. 1) содержит первый буферный усилитель 1, первый регистр 2. второй буферный усилитель 3, два элемента ИЛИ 4 и 5, блок 6 дешифрации, элемент ИЛИ 7, второй регистр 8, третий буферный усилитель 9, 0-триггер 10 режима, элемент И 11, Кроме того, на схеме показаны; первая группа информационных входов-выходов устройства для подключения к группе информационных входов-выходов ЭВМ 12, группа адресных входов устройства для подключения к адресным выходам ЭВМ 13.

„„ Ы„„1679486 Al (54) УСТРОЙСТВО КОНТРОЛЯ ИНТЕРФЕЙСА (57) Изобретение относится к вычислительной технике и предназначено для контроля интерфейса Э В М. Цел ь изобретения — повышение достоверности передачи и расширение диагностических возможностей устройства за счет обеспечения записи и считывания эталонной информации из устройства. Последнее содержит три буферных усилителя, два регистра, три элемента ИЛИ, элемент И, блок дешифрации, О-триггер. 6 ил, группа управляющих входов устройства для подключения к группе управляющих выхо- у дов ЭВМ 14, управляющий вход 15 устройства для подключения к сигналу, вторая группэ информационных входов-выходов устройства для подключения к группе информационных входов-выходов 16 удаленного устройства, группа адресных выходов

17 устройства для подключения к группе 0; адресных входов удаленного устройства, 1 группа управляющих выходов 18 устройства для подключения к группе управляющих входов удаленного устройства.

Первый буферный усилитель (фиг. 2) содержит 16 элементов и 191 — 191в. 16 усилителей 201 — 2016, 16 усилителей 211-2116, 16 элементов И 22 — 22ie, элемент HE 23.

Первый регистр (фиг, 3) содержит 16 D- в триггеров 241-241б, и 16 элементов И 251, 2516

Блок дешифрации (фиг. 4) содержит дешифратор.26 и 5 элементов И 27-31.

Второй регистр (фиг, 5) содержит 16 0триггеров 321-3216, 16 элементов И3313316, 8 D-триггеров 341-34в, 8 элементов И

351-35в.

1679486

20

30

Устройство контроля интерфейса работает следующим образом.

Сигналы первой группы входов 12, второй группы входов 13 и третьей группы входов 14, являющиеся соответственно линиями данных, адреса и управления, передаются соответственно через буферные усилители 1, 3 и 9, причем передача через усилитель 1 осуществляется в двух направлениях, а передача через усилители 3 и 9— в одном направлении, Управление передачей осуществляется сигналом с выхода элемента ИЛИ 5, объединяющего на первых и вторых входах сооТветственно сигналы управления с 4-ro и 1-го выходов усилителя 9, являющиеся соответственно сигналами чтения из памяти и регистров. Если активен один из названных сигналов (высокий), что означает чтение данных, то данные передаются с группы выходов 16 на группы входов 12; если сигналы неактивны (низкий), что означает запись данных, то передача данных производится с группы входов 12 на группу выходов 16, В регистр 2 записывается и считывается

16 разрядов эталонных данных. Выходы регистра объединены с первой группой выходов 16> 1616 и открываются только при чтении регистра 2.

В регистр8записывается исчитывается

24-разрядный эталонный адрес, причем регистр состоит из двух частей: 16-разрядной и 8-разрядной, в которые параллельно записываются соответственно старшая и младшая часть 24-разрядного адреса регистра.

16 выходов первой части и 8 выходов второй части регистра 8 объединены с первой группой выходов 16 и открываются только при чтении старшей и младшей частей адреса, которые считываются последовательно, Чтение регистра 2 и регистра 8 (отдельно из первой и второй частей) осуществляется сигналами из блока 6 дешифрации, которые формируются по сигналам адреса из усилителя и командам чтения из усилителя 9.

Сигнал с первого выхода блока 6 дешифрации считывает регистр 2, с третьего— первую часть 8, с четвертого — вторую часть регистра 8.

Запись в регистр 2 также осуществляется по сигналу дешифрации адресов соотве гствующих регистров и сигналу команды в блоке 6 дешифрации или по выходному сигналу элемента И 11. . Элемент И 11, а также элементы ИЛИ 4 и 7 обеспечивают диагностический поиск адреса сбойной ячейки памяти. Режим поиска задается программной установкой Dтриггера 10 в "1", На третий вход элемента

И 11 заведен сигнал с четвертого входа устройства. который является сигналом ошибки при считывании из памяти в блоке расширения.

Анализ ошибки производится считыванием сбойного адреса и данных из регистров 8 и 2 с помощью блока 6 дешифрации.

Первый буферный усилитель 1 предназначен для передачи двунаправленных сигналов данных и работает следующим образом.

Через элементы И 19> — 191в и усилители

201-20ю передаются сигналы от первой группы входов 121-12ы к первой группе выходов 161 — 16ы, Через элементы И 221 — 221в и усилители 21 — 21и передаются сигналы от первой группы выходов 16>-16>е к первой группе входов 121-12>g.

На первые входы элементов И 19 заведены соответствующие сигналы первой группы входов 12, с которыми объединены выходы соответствующих усилителей 21. На второй вход элементов И 19 заведен сигнал с выхода элемента ИЛИ 5, управляющий направлением передачи двунаправленных сигналов.

Если выход элемента 5 активен.(высокий), что означает команду чтения, то сигналы передаются через усилители 20 с первой группы выходов 16 на первую группу входов

12, При этом сигнал с выхода элементов НЕ

23 закрывает выходы элементов И 22 и запрещает передачу в противоположном направлении, Если выход элемента 5 неактивен (низкий), что означает команду записи, то сигналы передаются через усилители 21 с первой группы входов 12 на первую группу выходов.

16. При этом сигнал с выхода элементов НЕ

23 закрывает выходы элементов И 19 и запрещает передачу в противоположном направлении.

Первый регистр 2 предназначен для приема, хранения и последующего считывания эталонных данных. Работает регистр 2 следующим образом.

На D-входы триггеров 24> — 241в подаются данные с выходов буферного усилителя

1> — 1и, На синхровходы триггеров 24 подан сигнал с выхода элемента ИЛИ 4, который управляет записью в регистр 2. Данные считываются из регистра 2 по сигналу с первого выхода блока 6 дешифрации. Если этот сигнал активен (высокий), то элементы И 251-

25и закрыты и регистр 2 может или записывать, или хранить информацию.

Блок 6 дешифрации предназначен для выработки сигналов записи или чтения в первый и во второй регистры. На К входах дешифратора 26 подано К линий адресов с

1679486 <

25

40

55 выхода второго буферного усилителя 3, по которым определяется зона адресации устройства контроля, в которую входят первый регистр 2, второй регистр 8 (отдельно первая и вторая части) и триггер 10 режима.

Первый выход дешифратора 26 подается на первый вход элементов И 29 и 28 и определяет выбор первого регистра 2. На второй вход элемента И 27 подается команда чтения регистров — сигнал с первого выхода усилителя 9, который является командой чтения регистров, а на второй вход элемента И 28 подается сигнал второго выхода усилителя 9, который является сигналом записи в регистры.

Таким образом на выходе элементов И

27 и 28 вырабатывается соответственно сигнал чтения и записи для регистра 2. На первый вход элемента И 29 заведен сигнал с второго выхода дешифратора 26, Если этот сигнал активен (высокий), это чтение из второго регистра 8, первой его части, На первый вход элемента И 30 заведен сигнал с третьего выхода дешифратора 26.

Если он активен и активен сигнал чтения с выхода усилителя 9, то производится считывание информации с второй части регистра

8. На первый вход элемента И 31 подается сигнал с четвертого выхода дешифратора

26, а на второй его вход — сигнал записи с второго выхода усилителя 9, Если оба сигнала активны (высокие), тогда на вход триггера

10 подается строб, по которому производится запись информации с первой линии данных.

Второй регйстр 8 служит для приема, хранения и считывания эталонного адреса и. состоит из двух частей: первая часть, включающая 16 триггеров 32> — 32и и 16 элементов И 33 — 33ы, предназначена для запоминания 16 младших разрядов 24-разрядного адреса, вторая часть, включающая

8 0-триггеров 311-31в и 8 элементов И 35 358 äëÿ запоминания старших 8 адресов адреса. Запись адреса происходит параллельно в обе части второго регистра по сигналу записи с выхода элемента ИЛИ

7, который соединен с синхровходами 0триггеров 321-321в и триггеров 341-34а.

Считывание первой и второй частей регистров производится последовательно, соответственно сигналами с третьего и четвертого выходов блока 6; сигнал с третьего выхода разрешает передачу содержимого триггеров 32> — 32м через элементы И

33>-3316 на выходы регистра 8, Сигнал с четвертого выхода разрешает передачу содержимого триггеров 34 — 34в через элементы И 35 — 35в на выходы регистра 8. Выходы второго регистра 8 соединены с соответствующими линиями первой группы выходов

6 -16и. Когда нет сигнала чтения, выходы регистров 8> — 8 в неактивны по отношению к первой группе выходов, Формула изобретения

Устройство контроля интерфейса, содержащее первый, второй и третий буферные усилители, первый элемент ИЛИ, причем первая группа входов-выходов первого буферного усилителя подключена к . первой группе информационных входов-выходов устройства для подключения к информационным входам-выходам ЭВМ, вторая групп входов-выходов первого буферного усилителя является второй группой информационных входов-выходов устройства для подключения к информационным входамвыходам внешнего устройства, выход первого элемента ИЛИ подключен к входу управления первого буферного усилителя, группа входов второго буферного усилителя является группой адресных входов устройства для подключения к адресным выходам

ЭВМ; группа выходов второго буферного усилителя является группой адресных выходов устройства для подключения к- адресным входам внешнего устройства, группа входов третьего буферного усилителя являются группой управляющих входов устройства для подключения к управляющим входам 3ВМ, первый выход третьего буферного усилителя соединен с первым входом первого элемента ИЛИ и является первым управляющим выходом устройства для подключения к первому управляющему входу внешнего устройства, второй и третий выходы третьего буферного усилителя являются управляющими выходами устройства для подключения к второму и третьемууправляющим входам внешнего устройства, четвертый выход третьего буферного усилителя соединен с вторым входом первого элемента ИЛИ и является четвертым управляющим выходом устройства для подключения к четвертому управляющему входу внешнего устройства, отл и ч а ю ще ес я тем, что, с целью повышения достоверности передачи и расширения диагностических возможностей устройства, в него введены два элемента ИЛИ, первый и второй регистры, элемент

И. О-триггер, блок дешифрации, причем первый и второй выходы третьего буферного усилителя соединены соответственно с первым и вторым разрешающими входами блока дешифрации, группа информационных входов которого соединена с группой выходов второго буферного усилителя, первый выход блока дешифрации соединен с входом управления выдачей первого регистра, второй выход-с первым входом второго

1679486 элемента ИЛИ, третий выход — с первым входом управления выдачей второго регистра, четвертый выход — с вторым входом управления выдачей второго регистра, пятый выход — с входом стробирования D-триггера, информационный вход D-триггера соединен с первым входом-выходом из группы информационных входов-выходов первого буферного усилителя, выход 0-триггера соединен с первым входом элемента И, второй вход которого соединен с четвертым выходом третьего буферного усилителя, третий вход элемента И является управляющим входом устройства для подключения к выходу сигнала ошибки ЭВМ, выход элемента И соединен с вторым входом второго элемента ИЛИ, выход которого соединен со стро-. бирующим входом первого регистра, выход элемента И соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен с третьим выходом третьего

5 буферного усилителя, выход третьего элемента ИЛИ соединен со стробирующим входом второго регистра, группа информационных входов которого соединена с группой выходов второго буферного

10 усилителя, группа информационных выходов второго регистра подключена к группе информационных входов-выходов первого буферного усилителя, группы информационных входов-выходов первого регистра со15 единены с группой информационных входов-,выходов первого буферного усилителя, 1679486

251

1679486

Составитель В. Грошев

Редактор А. Шандор Техред M.Ìîðãåíòàë Корректор Т. Палий

Заказ 3215 Тираж 392 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб„4/5

Производственно-издательский комбинат "Патент", г, Ужгород, yn,Гагарина, 101