Параметрический источник опорного напряжения для оперативного запоминающего устройства

Иллюстрации

Показать всеРеферат

Изобретение относится к электронике и вычислительной технике и предназначено для использования в запоминающих устройствах на биполярных транзисторах. Целью изобретения является повышение надежности источника. Для этого в источник введены четвертый согласующий транзистор 15, четвертый резистор 8 смещения, второй диод 9 с соответствующими связями. Кроме того, источник содержит стабилизирующий конденсатор 19, шунтирующий резистор 8 и ослабляющий коэффициент усиления по обратным связям на высоких частотах. Это необходимо для предотвращения возникновения автоколебаний, возможность которого обусловлена наличием двух цепей отрицательной обратной связи: между коллектором и базой транзистора 15 через эмиттерный рп-переход транзистора 10, между коллектором транзистора 15 и базой транзистора 13 через цепь из элементов 7, 6, 4,5 и 14 . 1 з.п. ф-лы, 2 ил. п

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4746741/24 (22) 04.10.89 (46) 23.09.91. Бюл. М 35 (71),Научно-исследовательский институт молекулярной электроники (72) С.М.Игнатьев, В.Ф.Кошманов, В.М.Михайлов, О.А.Мызгин и В.Я.Протасов (53) 681.327.6 (088.8) (56) Патент США Ф 4099070, кл. 6 11 С 7/00, опубл. 1976.

Авторское свидетельство СССР

hh 1244718, кл, G 11 С 7/00, 1984. (54) ПАРАМЕТРИЧЕСКИЙ ИСТОЧНИК

ОПОРНОГО НАПРЯЖЕНИЯ ДЛЯ ОПЕРАТИВНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА (57) Изобретение относится к электронике и вычислительной технике и предназначено для использования в запоминающих уст„„SU „„1679548 Al оойствах на биполярных транзисторах.

Целью изобретения является повышение надежности источника. Для этого в источник введены четвертый согласующий транзистор 15, четвертый резистор 8 смещения, второй диод 9 с соответствующими связями.

Кроме того, источник содержит стабилизирующий конденсатор 19, шунтирующий резистор 8 и ослабляющий коэффициент усиления по обратным связям на высоких частотах. Это необходимо для предотвращения возникновения автоколебаний, воэможность которого обусловлена наличием двух цепей отрицательной обратной связи: между коллектором и базой транзистора 15 через эмиттерный р-и-переход транзистора

10, между коллектором транзистора 15 и базой транзистора 13 через цепь из элементов 7, 6, 4, 5 и 14 . 1 э.п, ф-лы, 2 ил.

1679548

25

35

55

Изобретение относится к электронике и вычислительной технике и предназначено для использования в запоминающих устройствах на биполярных транзисторах, Целью изобретения является повышение надежности параметрического источника опорного напряжения.

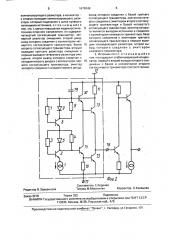

На фиг.1 представлена электрическая схема источника: на фиг.2 — схема его использования в формирователе уровня считывания оперативного запоминающего устройства (ОЗУ).

Источник опорного напряжения для

ОЗУ содержит генератор 1 тока, нагрузочный транзистор 2, первый 3 и второй 4 резисторы смещения, первый диод 5, первый согласующий транзистор 6, третий 7и четвертый 8 резисторы смещения, второй диод

9, второй согласующий транзистор 10, компенсирующий резистор 11, шину 12 нулевого потенциала, ключевой транзистор 13, третий 14 и четвертый 15 согласующие транзисторы, токозадающий резистор 16, шину

17 питания, выход 18, стабилизирующий конденсатор 19.

Элементы 2-9 составляют два эквивалента ячеек памяти ОЗУ, выбранных для считывания информации. Генератор 1 тока идентичен генератору тока считывания

ОЗУ. Ток генератора 1 протекает в транзисторе 2 и создает на резисторе 4 и диоде 5 падение напряжения, которое равно падению напряжения, формирующему низкий логический уровень в выбранной ячейке памяти. Для достижения более высокой степени эквивалентности режимов работы транзистора 2 и соответствующего транзистора ячейки памяти к базе транзистора 2 подключен резистор 3, формирующий смещение базового напряжения эа счет базового тока. Ток источника также протекает в транзисторе 6, Базовый ток транзистора 6 эквивалентен базовому току открытого транзистора выбранной ячейки памяти

ОЗУ. Адекватность режима работы транзистора 6 обеспечивается наличием в его коллекторной нагрузке резистора 8 и диода 9, идентичных нагрузоч HblM элементам ячейки памяти.ОЗУ. Протекая в резисторе 7, ток генератора 1 создает падение напряжения, соответствующее смещению напряжения высокого логического уровня в выбранной ячейке памяти. Одной из функций транзисторов 13 и 14 является фиксация напряжения в узле коллектора транзистора 2. Таким образом, напряжение в узле базы транзистора 10 равно сумме напряжения питания и падений напряжений на резисторах 4 и 7 и эмиттерных переходах транзисторов 6, 13 и 14.

Базовый потенциал транзистора 10 через последовательно включенные эмиттерные повторители на транзисторах 10 и 15 с соответствующим смещением поступает на выход 18. Если пренебречь базовым током транзистора 15, током выхода 18 и отклонением от единицы коэффициентов передачи эмиттерного тока транзисторов 13 и 14, эмиттерные токи у транзисторов 13 и 15 и у транзисторов 10 и 14 можно считать соответственно равными, В. данных условиях, если транзисторы 13,15 и 10, 14 имеют одинаковое конструктивное исполнение, с минимальной погрешностью будет справедливо равенство напряжений на эмиттерных переходах транзисторов 13 и 15 и транзисторов

10 и 14 соответственно.

С учетом этого значение выходного напряжения источника будет равно сумме напряжения питания и падений напряжения на резисторах 4 и 7 и эмиттерном переходе транзистора 6, Резистор 11 предназначен для формирования напряжения отрицательной обратной связи, компенсирующей изменение напряжения питания на шине 17. Конденсатор 19, шунтирующий резистор 8, ослабляет коэффициент усиления по обратным связям на высоких частотах. Это необходимо для предотвращения возникновения автоколебаний, воэможность которого обусловлена наличием двух цепей отрицательной обратной связи: между коллектором и базой транзистора 15 через эмиттерный р-и-переход транзистора 10 и между коллектором транзистора 15 и базой транзистора 13 через цепь из элементов 7,6,4,5 и 14.

Формула изобретения

1. Параметрический источник опорного напряжения для оперативного запоминающего устройства, содержащий генератор то. ка, нагрузочный транзистор, первый диод, три резистора смещения, три согласующих транзистора, компенсирующий резистор, токозадающий резистор, ключевой транзистор, эмиттер которого подключен к шине питания источника и соединен с первым выводом генератора тока, второй вывод которога соединен с эмиттером нагрузочного транзистора, база которого соединена с первым выводом первого резистора смещения, второй вывод которого соединен с ано.дом первого диода и первым выводом второго резистора смещения, второй вывод которого соединен с катодом первого диода и коллектором нагрузочного транзистора, первый вывод третьего резистора смещения соединен с базой первого согласующего. транзистора, база второго согласующего транзистора соединена с первым выводом

1679548

7.

Составитель С. Королев

Техред M.Mîðãåíòàë

Корректор О.Кравцова

Редактор В.Зарванская

Заказ 3218 Тираж 322 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35. Раушская наб., 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул.Гагарина, 101 компенсирующего резистора, а коллектор— с вторым выводом компенсирующего резистора, который подключен к шине нулевого потенциала источника, отличающийся тем, что, с целью повышения надежности источника опорного напряжения, он содержит четвертый согласующий транзистор, четвертый резистор смещения, второй диод, анод которого соединен с коллектором четвертого согласующего транзистора, базой второго согласующего транзистора, вторым выводом третьего резистора смещения и первым выводом четвертого резистора смещения, второй вывод которого соединен с катодом второго диода и с коллектором первого согласующего транзистора, змиттер которого соединен с анодом первого диода, катод которого соединен с базой третьего согласующего транзистора, коллектор которого соединен с эмиттером второго согласующего транзистора и базой четвертого

5 согласующего транзистора, эмиттер которого является выходом источника и соединен с коллектором ключевого транзистора, база которого соединена с эмиттером третьего согласующего транзистора и первым выво10 дом токозадающего резистора, второй вывод которого соединен с эмиттером ключевого транзистора.

2. Источник по п.1, отл и ча ю щий с я тем, что содержит стабилизирующий конден15 сатор, первый и второй выводы которого соединены с базой и коллектором второго согласующего транзистора соответственно,