Устройство для измерения параметров сигнала считывания из накопителя на цилиндрических магнитных доменах

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для определения параметров считанного сигнала в запоминающих устройствах на цилиндрических магнитных доменах (ЦМД). Цель изобретения - повышение точности определения значений параметров считанного сигнала . Устройство содержит генератор 1, счетчик 2 параметра, формирователь 3 управляющих импульсов, управляемый усилитель 4, блок 5 обработки данных и вычислительный блок 6 Использование устройства для измерения параметров сигнала считывания позволяет позволяет повыситьопределения фазы и порога на основе статистической обработки данных измерений. 2 з.п. ф-лы, 3 ил.

COIO3 СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

I (51)5 G 11 С 11/14

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

l !

Ф

Ьм

Ф (21) 4737891/24 (22) 22.06.89 (46) 23.09,91, Бюл. М 35 (71) Институтэлектроники и вычислительной о техники AH ЛатвССР (72) И.М,Блюменау и Ю.П,Кашс (53) 681.327,6 (088.8) (56) The Bell System Technical JoUãnà! 1981, ч 60, М 4, р. 485 — 500, fig 4.

Запоминающие устройства и системы памяти на цилиндрических магнитных доменах. — Сб. научных трудов. M.: ИНЭУМ, 1986, с. 60-71, рис.1. (54) УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ПАРАМЕТРОВ СИГНАЛА СЧИТЫВАНИЯ ИЗ

НАКОПИТЕЛЯ НА ЦИЛИНДРИЧЕСКИХ

МАГНИТНЫХ ДОМЕНАХ

„„SU ÄÄ 1679550 А1 (57) Изобретение относится к вычислительной технике и может быть использовано для

on редел ения параметров счита нного сигнала в запоминающих устройствах на цилиндрических магнитных доменах (ЦМД). Цель изобретения — повышение точности on ределения значений параметров считанного сигнала. Устройство содержит генератор 1, счетчик 2 параметра, формирователь 3 управляющих импульсов, управляемый усилитель 4, блок 5 обработки данных и вычислительный блок 6, Использование устройства для измерения параметров сигнала считывания позволяет позволяет повыситьопределения фазы и порога на основе статистической обработки данных измерений.

2 з.п. ф-лы, 3 ил, 1679550

Изобретение относится к вычислител,;ной технике и может быть использовано для определения параметров считанного сигнала в запоминающих устройствах на цилиндрических ма гн итн ых доменах (ЦМД), Цель изобретения — повышение точности определения значений параметров считанного сигнала.

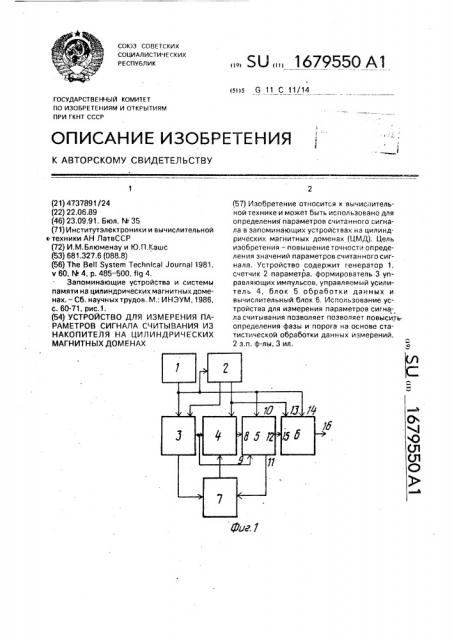

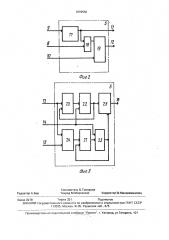

HB фиг,1 прив8дена структурная схема устройства дпя измерения параметров сигнала считывания накопителя на ЦМД; на фиг.2 — структурная схема блока обработки данных; на фиг,й — структурная схема вычислительного блока.

УсТроМсТВо для изм8рения параметров . сигнала счлтывания накопителя Hà ЦМД содержит генератор 1, счетчлк 2 параметра, формлрователь 3 управля ощих импульсов, управляемый усилитель 4, опок 5 Обработки данных в вычислительный блок 6, накопитель 7 на ЦМД, вход 8 данных, тактовый вход 9, вход 10 сброса, выход 11 данных и группа кодовых выходов 12 блока обработки данных, группу входов 13 параметра, тактовый вход 14, группу входов 15 аргумента и выходы 16 вычислительного блока.

Блок обработки данных (см. фиг.2) содержит кольцевой регистр 17, узел 18 сравнения и счетчик 19,.

Вычислительный блок (см, фиг.3) состоMT из первого M BTopo о c!/VIMPTopoB 20, 21, первого и второго регистров 22, 23, умножителя 24 и делителя 25, Устройство работает следующим образом.

Генератор 1 вырабатывает импульсы, период которых равен длительностл страничной операцил (чтения / записи страницы) накопителя, Формир",âàòåëü и управляющих импульсов по каждому импульсу от генератора 1, соответствующему началу cTpaHMIJы, формирует набор сигналов, который Определяетс,-: сигналом пере-, носа счетчика 2 параметра, задающим режим работы — чтение либо запись данных в накопитель 7, С первого выхода формирователя 3 управпяющлх импульсOв данныс сигналы поступают на вход управления накопителя 7 и управляют его работой. В режиме записи формируются сип- злы вывода, генерации и ввода, а в режиме чтения— си-налы репликации и счлтывания, l(oHI

40 тому первый импульс генератора 1 обеспечивает формирование управляющей последовательности импульсов для записи одной страницы в накопи ель 7. При этом в процессе выполнения операции блок 5обработки данных формирует блок данных, имеющий заданное соотношение "1" и "0", который в виде последовательности импульсов генерации с выхода данных блока 5

Обработки данных заносится в накопитель

7, Например, для равного количества этих оазрядов блок paníü|õ может состоять из шестнадцатиричных байтов 33Н либо ОН.

Г1оследующие такты генератора 1 соответствуют работе формирователя 3 управляющих импульсов и накопителя 7 в режиме чтения записанной страницы, когда управляемый усилитель 4 с у етом значения параметра на группе кодовых выходов счетчика

2 параметра / порога или фазы считывания/ преобразует выходной сигнал накопителя 7 в цифровую последовательность, поступающую на вход 8 данных блока 5 обработки данных. При этом для каждого очередного такта счлтывания счетчик 2 параметра выдает последовательные значения параметра управляемому усилителю 4 и вычислительному блоку 6. поступающие на их группы входов параметра, а формирователь 3 управляющих импульсов управляет работой накопителя 7 и сигналом на втором выходе осуществляет побитную синхронизацию данных управляемого усилителя 4 и блока 5

Обраоотки данных. Последний Осуществля ет побитное сравнение последовательности данных с выхода управляемого усилителя 4 с Образцом, формируемым данным блоком, и подсчитывает количество правильно считаиных разрядов в странице. Число правильно считанных разрядов с группы катодных выходов блока 5 обработки данных поступает на руппу входов аргумента вычлспитепьного блока 6. На основании значений параметра и соответствующего ему количества правильно считанных разрядов значения кода на группе входов аргумента в вычислительном блоке 6 с частотой генерзтсра 1 производлтся математическая

Обработка, в частности вычисление среднего значения функцли числа правильно считанных разрядов от параметра

По завершении перебора всех значений параметров считывания и процесса вычислений на выходах 16 устройства формируется искомое значение оптимального параметра (порога/фазы) с итывания.

Блок 5 обработки данных работает след:,, юьцим образом.

На выходе кол ьцевого регистра 17 вырабати за ется последовател ь ность бит, я ел я ю1679550 щаяся исходной для записи в накопитель 7 в образцовой для сравнения узлом 18 сравнения с данными, считанными с выхода 8 управляемого усилителя 4. В начале каждого цикла чтения счетчик 19 сбрасывается сигналом с выхода генератора 1, а в конце цикла чтения на его выходах присутствует код, соответствующий количеству совпадающих бит, являющемуся аргументом для вычислительного блока 6.

Вычислительный блок 6 работает следующим образом. В исходном состоянии регистры 22 и 23 очищены, т,е. установлены в начальное(нулевое) состояние. По завершении каждого цикла считывания на выходах сумматоров 20 и 21 формируются соответственно сумма числа совпадающих бит (аргумента) и сумма произведений последних на текущее значение параметра, которые фиксируются соответственно в регистрах 22 и

23. После завершения сканирования всего диапазона изменения параметра/фазы либо порога/ на выходах делителя 25 будет сформировано значение оптимального порога (фазы). На основании формул математической статистики.

Таким образом, использование устройства для измерения параметров сигнала считывания позволяет повысить точность определения фазы и порога на основе статистической обработки данных измерений.

Формула изобретения

1. Уст 1ойство для измерения параметров сигнала считывания из накопителя на цилиндрических магнитных доменах, содержащее генератор и формирователь управляющих импульсов, первый выход которого является управляющим выходом устройства, вход запуска формирователя управляющих импульсов подключен к выходу генератора, о т л и ч а ю щ е е с я тем, что, с целью повышения точности определения значений параметров считанного сигнала, в него введены счетчик параметра, управляемый усилитель, блок обработки данных и вычислительный блок, причем тактовый вход вычислительного блока, вход сброса блока обработки данных и счетный вход счетчика параметра подключены к выходу генератора, группа кодовых выходов счетчика параметра соединена с группами входов параметра вычислительного блока и управляемого усилителя, тактовый вход которого подключен к второму выходу формирователя управляющих импульсов, с дам первого регистра, э выходы второго

55 сумматора — к разрядным входам второго регистра.

50 которым соединен также тактовый вход блока обработки данных, выходданных которого является выходом данных устройства, группа кодовых выходов блока обработки данных подключена к группе входов аргумента вычислительного блока, выходы которого являются выходами параметра устройства, выход переноса счетчика параметра соединен с входом задания режима формирователя управляющих импульсов, ичформационный вход управляемого усилителя является входом данных устройства, а выход управляемого усилителя подключен к входу данных блока обработки данных.

2.Устройство по п,1, отл ича ющеес я тем, что блок обработки данных содержит кольцевой регистр, узел сравнения и счетчик, выходы которого являются группой одовых выходов блока обработки данных, а вход начальной установки счетчика подключен к входу сброса блока обработки данных, первый вход узла сравнения соединен с входом данных блока обработки, выход узла сравнения подключен к счетному входу счетчика, а второй вход узла сравнения соединен с выходом кольцевого регистра, вход синхронизации которого является тактовым входом блока обработки данных, а выход кольцевого регистра — выходом данных блока обработки данных.

3. Устройство по п.1, о т л и ч а ю щ е ес я тем, что вычислительный блок содержит первый и второй сумматоры, первый и второй регистры, умножитель и делитель, выходы которого являются выходами параметра устройства, входы первых групп первого сумматора и умножителя соединены с группой входов параметра вычислительного блока, входы второй группы умножителя являются группой входов аргумента вычислительного блока, выходы первого регистра соединены с входами второй группы первого сумматора и входами первой группы делителя, входы второй группы которого подключены к выходам второго регистра, с которым соединены также входы первой группы второго сумматора, входы второй группы которого подключены к выходам умножителя, тактовые входы первого и второго регистров соединены с тактовым входом вычислительного блока, выходы первого сумматора подключены к разрядным вхо1679550

Составитель В.Топорков

Техред М.Моргентал Корректор М,Максимишинец

Редактор А. Бер

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

Заказ 3218 Тираж 321 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5