Многоканальная цифровая телеметрическая система

Иллюстрации

Показать всеРеферат

Изобретение относится к технике передачи данных. Цель изобретения - повышение точности приема, Многоканальная цифровая телеметрическая система содержит передающий полукомплект 1, состоящий из датчика 2 и передатчика 3, канал 4 связи, приемный полукомплект 5, состоящий из формирователя 6 импульсов, регистра 7 сдвига, блока 8 синхронизации, счетчика 9, блока 10 выделения маркерного сигнала, генератора 11 импульсов, второго распределителя 12, первого распределителя 13, первого и второго элементов И 14 и 15, блока 16 обнаружения ошибки, первого и второго блоков 18 и 19 памяти, первого и второго вычитателей 21 и 22, блоков 24 воспроизведения . Цель достигается введением элемента НЕ 17, третьего блока 20 памяти и элемента ИЛИ 23. 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (kl) ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ б(. 2. 7

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) 1053127 (21) 4751937/09 (22) 20.10.89 (46) 30.09.91. Бюл, М 36 (71) Московский институт инженеров гражданской авиации (72) С,Ж.Кишенский, Н.С.Вдовиченко, А,Л.Кузьмин и О.Ю.Христенко (53) 621.398 (088.8) (56) Авторское свидетельство СССР

К 1053127, кл, G 08 С 15/06, 1982, (54) МНОГОКАНАЛЬНАЯ ЦИФРОВАЯ ТЕЛЕМЕТРИЧЕСКАЯ СИСТЕМА (57) Изобретение относится к технике передачи данных, Цель изобретения — повышение точности приема, Многоканальная (I (si)s G 08 С 15/06, Н 04 1 27/00 цифровая телеметрическая система содержит передающий полукомплект 1, состоящий из датчика 2 и передатчика 3, канал 4 связи, приемный полукомплект 5, состоящий из формирователя 6 импульсов, регистра 7 сдвига, блока 8 синхронизации, счетчика 9, блока 10 выделения маркерного сигнала, генератора 11 импульсов, второго распределителя 12, первого распределителя 13. первого и второго элементов И 14 и

15, блока 16 обнаружения ошибки, первого и второго блоков 18 и 19 памяти, первого и второго вычитателей 21 и 22, блоков 24 âîñпроизведения. Цель достигается введением элемента Н Е 17, третьего блока 20 памяти и элемента ИЛИ 23, 3 ил.

1681317

55

Изобретение относится к технике передачи данных и дискретной информации и может быть использовано для информационного обеспечения систем передачи данных, сетей связи и автоматизированных систем управления, Цель изобретения — повышение точности приема.

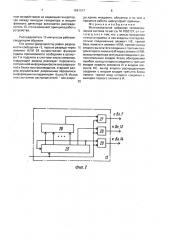

На фиг,1 изображена структурная электрическая схема многоканальной цифровой телеметрической системы; на фиг.2 — схема первого распределителя; на фиг,З вЂ” схема первого вычитателя.

Многоканальная цифровая телеметрическая система содержит передающий полукомплект 1, состоящий из датчика 2 и передатчика 3, канал 4 связи, приемный полукомплект 5, состоящий из формирователя 6 импульсов, регистра 7 сдвига, блока

8 синхронизации, счетчика 9, блока 10 выделения маркерного сигнала, генератора 11 импульсов, второго распределителя 12, первого распределителя 13, первого и второго элементов И 14 и 15, блока 16 обнаружения ошибки, элемента НЕ 17, первого, второго и третьего блоков 18-20 памяти, первого и второго вычитателей 21 и 22, элемента ИЛИ

23 и блоков 24 воспроизведения.

Распределитель 13 состоит из кольцевого регистра 25, элемента ИЛИ 25 и элементов И 27-29.

Вычитатель 21 состоит из сумматоров

30 по модулю два, сумматора 31, сумматоров 32 по модулю два и сумматора ЗЗ.

Многоканальная цифровая телеметрическая система работает следующим образом, Алгоритм функционирования предлагаемой системы заключается в следующем.

При обнаружении ошибки в принятом значении данного (некоторого) параметра это значение не фиксируется и в дальнейшем (при следующей передаче значения этого параметра) не используется проверка апер туры, так как нет достоверного предыдущего сообщения.

B передающем полукомплекте 1 передатчик 3 производит опрос датчиков 2 и формирует сообщение, представляющее собой последовательную кодо-импульсную посылку информационных и контрольных кодовых сигналов. Контрольные кодовые символы вводятся для проверки лишь определенного числа младших разрядов информационных кодовых символов. Сообщения поступают в канал связи циклически, в определенной заранее заданной последовательности. Циклы передачи отделяются друг от друга маркерным сигналом, 15

Приемный полукомплект 5, принимая кодовые посылки из канала 4 связи, преобразует последовательный код в параллельный и выдает его в соответствующие блоки

24 воспроизведения. В случае обнаружения искаженных кодовых посылок выдача принятой информации в блоки 24 воспроизведения запрещается, Сигналы из канала 4 связи поступают на формиоователь 6 импульсов. Блок 8 инерционной синхронизации сравнивает фазу выходных импульсов формирователя 6 с фазой импульсов на выходе распределителя 13, Блоком 8 осуществляются коррекции . частоты и фазы импульсов генератора 11 (т,е. блок 8 синхронизации работает как обычный синхронизирующий узел с непосредственным воздействием на задающий генератор). Регистр 7 сдвига выполняет функции преобразования последовательного кода в параллельный и запоминания информации, принятой в одной кодовой посылке (сообщении о значении некоторого параметра). На информационный вход регистра 7 поступает последовательный код кодового сообщения от формирователя б, Сдвиг осуществляется импульсами, поступающими с выхода распределителя 13 (конкретно, с выхода элемента И 27). При поступлении на вход приемника последнего символа очередного сообщения (все сообщения имеют фиксированную длину, а емкость регистра на два разряда больше, чем эта длина сообщения) на выходах регистра 7 имеется параллельный код, соответству1ощий этому сообщению. Одновременно на выходе счетчика 9 (его емкость равна разрядности сообщения) появляется одиночный импульс, поступающий на элементы И 14 и 15.

В вычитателе 21 определяется абсолютная величина разности между предыдущим значением параметра, записанным в блоке

18, и новым значением этого же параметра, Вычитатель 21 работает следующим образом (на фиг,З приведен в качестве примера вычитатель, определяющий модуль разности трехразрядных двоичных чисел). Вычитание заменяется (как это обычно делается в ЭВМ) сложением чисел в дополнительном коде, причем новое значение параметра используется в качестве уменьшаемого, а старое — в качестве вычитаемого, На сумматорах 30 формируется дополнительный код отрицательного вычитаемого (с единицей в знаковом — старшем, в данном случае четвертом — разряде и с добавлением единицы в младший разряд путем присоединения входного переноса PO к единичному потенциалу), После суммирования на сумматорах

32 и 33 производится преобразование сум1681317

20 сигнал по апертуре может поступить на эле-40 и

50 мы в прямой код — если старший (знаковый) разряд — нулевой, то результат без изменений выводится на выход блока, а если единичный, то производится обычное преобразование — инверсия на сумматорах 32 и прибавление единицы в младший разряд сигналом на PO сумматора 33 (в сумматорах

31 и 33 первое слагаемое — разряды А, второе — разряды В, входной перенос — PO, выходной перенос (не используется) — P3, результат (сумма) — разряды S), Выборка элементов памяти в блоке 18. соответствующих этому параметру, осуществляется адресным сигналом, поступающим от распределителя 10 каналов.

Полученная на выходе вычитателя 21 разность вычитается в вычитателе 22 из соответствующего значения апертуры для этого параметра, записанного в блоке 19 — постоянном запоминающем устройстве, в то время как первый 18 и третий 20 блоки памяти реализуются как оперативное запоминающее устройство, и выбранного с помощью адресного сигнала, поступающего от распределителя 12 на его адресный вход. Если результат вычитания — число положительное, то на вход элемента ИЛИ 23 поступает положительный разрешающий потенциал, Из блока 20 считывается результат обнаружения ошибки при предыдущей передаче данного параметра, Если при предыдущей передаче данного параметра была обнаружена ошибка, то в соответствующую ячейку блока 20 была записана (через элемент НЕ) единица и выдача в настоящий момент времени ее на второй вход элемента ИЛИ 23 исключает запрет по возможному несовпадению с текущей апертурой.

Таким образом, запрещающий нулевой мент И 15 лишь в том случае, когда разность вычитателя 22 меньше нуля и в предыдущем приеме данного параметра не было зафиксировано ошибки.

Вычитатель 22 может быть выполнен в виде стандартного устройства сравнения, с которого снимается разрешающий единичный сигнал с выхода "Больше", когда вычитается из значения апертуры с блока 19 значение текущей разности, сформированное в вычитателе 21.

Блок 16 обнаружения ошибки в кодовой посылке осуществляет проверку на достоверность определенного числа младших (по выбору пользователя) разрядов кода сообщения путем анализа проверенных разрядов, поступивших из канала 4 связи и записанных в регистре 7. Этот блок формирует запрещающий нулевой потенциал при обнаружении ошибок, а при отсутствии

35 ошибок — разрешающий единичный потенциал, который поступает на вход элемента

И 15, давая разрешение на прохождение записывающего импульса с выхода распределителя 13 в блоки 24 воспроизведения.

При этом код информации по данному параметру с регистра 7 переписывается в соответствующий блок воспроизведения.

Перезапись нового значения параметра в блок 18 осуществляется по сигналу с третьего выхода распределителя 13 на элемент И

14 по разрешающим сигналам со счетчика 9 и блока 16 (В том случае, если ошибки не

1 обнаружено. Если же ошибка обнаружена, то записи неверного значения дзннбгс параметра в блок 18 не происходит), Сигнал с выхода элемента И 14 поступаетт на вход записи блока 18.

Одновременно в блок 20 по этому же адресу(заданного параметра) записывается результат обнаружения ошибки через эле мент НЕ ("0" — ошибка не обнаружена, "1"— обнаружена) для дальнейшего анализа данного параметра. Это целесообразно, так как при длительных перерывах (несколько подряд ошибочных сообщений по данному па-раметру) значение апертуры становится недействительным и мОжет некорректно отменить очередное воспроизведение данного параметра.

Переключение распределителя 12 ilp0исходит по заднему фронту импульса с выхода счетчика 9. Обнаружив маркерный сигнал, блок 10 вырабатывает импульс, который, поступая на установочные входы счетчика 9 и распределителя 12, устанавливает их в исходное состояние.

Блок обнаружения ошибок представляет собой декодер произвольн" избранного для передачи кода (циклического, итеративного, кода Хемминга и пр.), выполненный по стандартной схеме. Например, при использовании кода с проверкой на нечетность данный блок представляет собой совокупность сумматоров по модулю два, на которые поданы младшие разряды информационной посылки и проверочный разряд, При обнаружении ошибки (четное число единиц в сумме по модулю два) на выходе последнего сумматора (все сумматоры по модулю два данного декодера соединяются пирамидальным образом последовательно) будет "0", что и требуется.

Совместно с регистром 7 блок 16(в данном случае дешифратор) легко образуют декодер, например, кода Хемминга в режиме обнаружения ошибок.

Блок 8 синхронизации может быть выполнен по принципу обычного устройства тактовой синхронизации с непосредствен1681317 ным воздействием на задающий генератор, где между выходом генератора и входом фазового детектора включается распределитель 13, что не изменяет принципа работы устройства, 5

Распределитель 13 импульсов работает следующим образом.

Его длина (разрядность) равна разрядности сообщения+2, первые разряды через 10 элемент ИЛИ 26 осуществляют функции сдвига принимаемого сообщения в регистре 7 и подсчета в счетчике числа символов, следующий разряд реализует перезапись полученной информации(если она разреше- 15 на) в блоки воспроизведения, старший разряд осуществляет разрешение перезаписи информации по параметрам блока,18. Исходное состояние распределителя — все разря20 ды,кроме младшего, обнулены и по ним в процессе работы циркулируют единицы.

Формула изобретения

Многоканальная цифровая телеметрическая система поавт.св. М 1053127, от л ич а ю щ а я с я тем, что, с целью повышения точности приема, в нее введены последовательно соединенные элемент НЕ, третий блок памяти и элемент ИЛИ, причем выход второго вычитателя соединен с третьим входом второго элемента И через элемент ИЛИ, выход генератора импульсов соединен с дополнительным входом блока обнаружения ошибки, выход которого соединен с третьим входом первого элемента И и входом элемента НЕ, выход второго распределителя соединен с вторым входом третьего блока памяти, третий вход которого соединен с выходом первого элемента И.

Составитель Н.Лазарева

Техред М.Моргентал Корректор M.Максимишинец

Редактор Я.Лежнина

Производственно-издательский комбинат "Патент", г. Ужгород, ул, Гагарина, 101

Заказ 3313 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5