Интегрирующий аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой электроизмерительной технике и предназначено для аналого-цифрового преобразования с двухтактным интегрированием раз нополярных напряжений Цель повышение точности преобразования и быстродействия АЦП содержит коммутатор интегратор, компаратор, ключ, накопительный элемент, выполненный в виде конденсатора , повторитель, два делителя опорного напряжения, блок управления Введение дополнительного ключа позволяет избежать попадания выбросов напряжения с вы хода компаратора на конденсатор, что вызывает погрешность корректирующего напряжения и препятствует уменьшению времени коррекции и цикла преобразования , тем самым повышая нз порядок быстродействие 2 з п.ф-лы. 4 ил

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

rs<>s Н 03 M 1/52

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР!

1 ! 1

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4396063/24 (22) 21,03.88 (46) 30,09.91. Бюл. ¹ 36 (71) Львовский политехнический институт им, Ленинского комсомола (72) И.M.Âèøåí÷óê, Н.Г.Гитшов, О.О,Каганов, А,П.Конопкин, P.Â.Курдыдык, В.Ф.Ткаченко, А,И.Халоша и 3.M.×åõîâñêèé (53) 681,325 (088.8) (56) Патент Англии

¹ 1390064, кл. G 4 Н, опублик. 1975, Авторское свидетельство СССР

¹ 998822119922,, кКл, Н 03 М 1/52, 1981. (54) ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ (57) Изобретение относится к цифровой электроизмерительной технике и предназИзобретение относится к цифровой электроизмерительной технике и предназначено для аналого-цифрового преобразования с двухтактным интегрированием разнополярных напряжений с одним источником опорного напряжения и с запоминающей обратной связью для компенсации дрейфа усилителей устройства.

Цель изобретения — повышение точности преобразования и быстродействия.

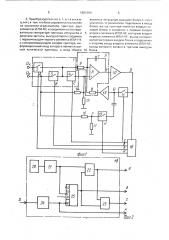

На фиг. 1 представлена структурная схема АЦП; на фиг. 2 — схема устройства управления; на фиг. 3 — временная диаграмма устройства управления; на фиг, 4 — временная диаграмма работы устройства.

Устройство содержит коммутатор 1, состоящий из ключей 2 — 4, интегратор 5, включающий операционный усилитель б и,. Ю „„1681384 А1 начено для аналого-цифрового преобразования с двухтактным интегрированием разнополярных напряжений. Цель повышение точности преобразования и быстродействия. АЦП содержит коммутатор, интегратор, компаратор, ключ, накопительный элемент, выполненный в виде конденсатора, повторитель, два делителя опорного напряжения, блок управления. Введение дополнительного ключа позволяет избежать попадания выбросов напряжения с выхода компаратора на конденсатор, что вызывает погрешность корректирующего напряжения и препятствует уменьшению времени коррекции и цикла преобразования, тем самым повышая на порядок быстродействие. 2 з.п.ф-лы, 4 ил. конденсатор 7, резисторы 8, 9, компаратор

10, ключ11, накопительный элемент, выполненный на конденсаторе 12, повторитель

13, резисторы 14 и 15, образующие первый делитель опорного напряжения, резисторы

16 и 17, образующие второй делитель опорного напряжения, блок 18 управления и ключ 19.

Блок 18 управления содержит генератор 20 тактовых импульсов, делитель 21 частоты, элементы ИЛИ-НЕ 22 и 23 и усилитель-ограничитель 24, триггер 25.

Аналого-цифровой преобразователь работает следующим образом.

Цикл работы — фиксированный и состоит(фиг. 4) из интервалов интегрирования Т1, преобразования Т2 и коррекции ТЗ.

168138 4

В течение интервала ин гегрирования Т сигналом блока 18управления(фиг. 4б) ключ

2 замыкается, ключи 3, 4 и 11 (фиг. 4в, г) разомкнуты, ключ 19 (фиг. 4ж) замкнут.

Поскольку неинвертирующий вход операционного усилителя 6 интегратора находится под напряжением смещения Ucw, снимаемым с делителей 14 и 15, происходит интегрирование разности входного напряжения Ux и напряжения Uc (фиг, 4з), После окончания интервала Т1 сигналом А блока

18 (фиг. 4б) ключ 2 размыкается, а ключ 3 замыкается (фиг, 4в), подключая к входу интегратора опорное напряжение Uo В течение интервала Т2 происходит интегрирование разности напряжений Uo u

Uc, напряжение на выходе интегратора 6 стремится к нулю (фиг, 4з), по достижении которого срабатывает компаратор 10, Сигналами В и Н блока 18 (фиг. 4в, ж) ключи 3 и 19 размыкаются, а сигналом С (фиг. 4г) ключи 3 и 11 (фиг. 4) замыкаются. Длительность импульса управления Н ключом 19 (фиг. 4ж) равна времени переходного процесса при замыкании обратной связи, после окончания импульса Н (фиг. 4) ключ 19 замыкается, включая конденсатор 12 в цепь кор ректирующей обратной связи, До начала следующего цикла измерения на конденсаторе 12 происходит запоминание напряжения дрейфа усилителя 6. компаратора 10 и повторителя 13 и разности напряжения Uc>< и напряжения в точке F. Длительность интервала Т2 однозначно определяет величину и полярность измеряемого напряжения.

Выходное напряжение интегратора в интервале Т1 равно — 1.!.

Он 1

Йи Си в интервале Т2

Т2

0н2

R Cè где Rt и С вЂ” интегрирующие резистор и конденсатор (резистор 9 и конденсатор 7).

Так как U» + U

„. Uc T1 Ux T1

Uo — Uca Uo — Ucv

При Ох = О получаем T2 = Т1 (при К =.

=- 2). Т2 =- 5T1 (при К = 3), UcM

В отличие от прототипа, запоминающий конденсатор не включается во время переходного процесса в цепь корректирующей обратной связи, поэтому выбросы напряжения с выхода усилителя-компаратора, вызывающие погрешность корректирующего напряжения, на конденсатор не попадают и

ЛО практически равно нулю. Тем самым устраняюгся нелинейность, свойственная

55 к инвертирующему входу операционного усилителя, который через конденсатор подключен к выходу операционного усилителя, который является выходом блока, а неинвертирующий вход является первым входом блока, 10

50 схеме прототипа, и причина, препятствующая уменьшению времени коррекции и цикла преобразования, что дает возможность повысить почти на порядок быстродействие

АЦП, Блок управления формирует с помощью генератора 20 тактовых импульсов, делителя 21 частоты, триггера 25 и элементов ИЛИ

22, 23 три временных интервала А, В, С коммутации соответствующих ключей. Усилитель-органичитель 24 формирует сигнал от компаратора для управления ключом 19

Формула изобретения

1, Интегрирующий аналого-цифровой преобразователь, содержащий коммутатор, первый информационный вход которого является входной шиной, второй информационный вход — шиной опорного напряжения, третий информационный вход объединен с первым входом интегратора и подключен к выходу первого делителя опорного напряжения, входы которого соединены соответственно с шиной опорного напряжения и общей шиной, а выход коммутатора подключен к второму входу интегратора, выход которого через компаратор соединен с входом блока управления и информационным входом первого ключа, выход которого соединен с первым выводом накопительного элемента, выполненного на конденсаторе, и через повторитель соединен с третьим входом интегратора, второй делитель опорного напряжения. входы которого соединены соответственно с шиной опорного напряжения и общей шиной, а первый, второй и третий выходы блока управления подключены соответственно к первому, второму и третьему управляющим входам коммутатора, третий выход блока управления соединен с управляющим входом первого ключа, отличающийся тем, что, с целью повышения точности преобразования и быстродействия, в него введен второй ключ, информационный вход которого соединен с выходом второго делителя опорного напряжения, выход подключен к второму выводу конденсатора, а управляющий вход — к четвертому выходу блока управления, 2, Преобразователь по и. 1, о т л и ч а юшийся тем, что интегратор выполнен на операционном усилителе, конденсаторе и двух резисторах, первые выводы которых являются соответственно вторым и третьим входами блока, вторые выводы подключены же1ЗЧ

3. Преобразователь по и. 1, о т л и ч а юшийся тем, что блок управления выполнен на усилителе-ограничителе, триггере, двух элементах ИЛИ-НЕ и соединенных последовательно генераторе тактовых импульсов и делителе частоты, выход которого соединен с первым входом первого элемента ИЛИ-HE и синхронизирующим входом триггера, информационный вход которого является шиной логической единицы, а вход сброса является четвертным выходом блока и череэ усилитель-ограничитель подключен к входу блока, вы. .од риггерз является вторым выходом блока и соединен с первым входом

5 второго элемента ИЛИ-НГ и вторым входом первого элемента ИЛИ-НЕ. выход ксторого является первым входом блока и подключен к второму входу второго элемента ИЛИ-НЕ, выход которого является третьим выходом

10 блока.

1681384

&иод делал.

7f

ai е/ (. и/ н

Ф((/

Составитель В, Махнанов

Редактор А. Маковская Техред M.Моргентал Корректор М. Максимишинец, Заказ 3316 Тираж 443 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101