Классификатор логического вектора

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в системах обработки логической информации , например, в устройствах распознавания , Цель изобретения - расширение функциональных возможностей за счет произвольного выбора числа классов от 1 до N (N - размерность входного вектора) и количества единичных бит в каждом классе от 1 до т-1 (т - разрядность настроечных входов группы). Классификатор содержит треугольную матрицу процессорных модулей. Цель изобретения достигается за счет возможности перенастройки процессорных модулей . 2 ил.

СОЮЗ СОВЕТСКИ., СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)з 6 06 F 7/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

K АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4721267/24 (22) 20.07,89 (46) 07.10.91. Бюл. N 37 (71) Московский институт радиотехники, электроники и автоматики (72) А. С. Бессонов, Н. Н. Евтихиев, В. Ф.

Папуловский, В. Н. Сведе-Швец и В. Д. Соболев (53) 681.3(088.8) (56) Авторское свидетельство СССР

М 664169, кл. G 06 F 7/00, 1977.

Фет Я. И. Специализированные однородные структуры. Синтез схем на основе цифровых компрессоров, — Препринт М 27, Новосибирск; Институт математики СО AH

СССР, 1982.

Изобретение относится к цифровой вычислительной технике и может быть использовано для обработки логической информации, например в системах распознавания.

Цель изобретения — расширение функциональныхых воэможностей классификатора за счет произвольного выбора числа классов от 1 до N (М вЂ” размерность входного вектора) и количества единичных бит в каждом классе от 1 до m— - 1 (m — разрядность настроечных входов группы).

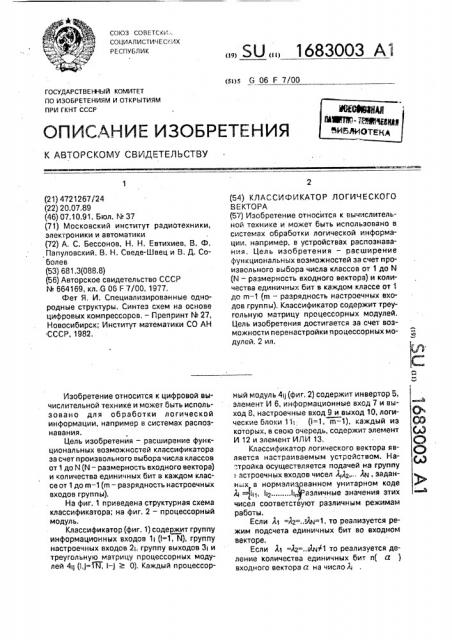

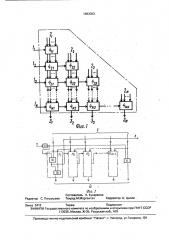

На фиг. 1 приведена структурная схема классификатора; на фиг. 2 — процессорный модуль.

Классификатор (фиг. 1) содержит группу информационных входов 1l (1=1, N). группу настроечных входов 2ь группу выходов 3l и треугольную матрицу процессорных модулей 4il (l,j-1N, l — j О), Каждый процессор„„SU„„1683003 А1 (54) КЛАССИФИКАТОР ЛОГИЧЕСКОГО

ВЕКТОРА (57) Изобретение относится к вычислительной технике и может быть использовано в системах обработки логической информации, например, в устройствах распознавания. Цель изобретения — расширение функциональных возможностей за счет произвольного выбора числа классов от 1 до N (N — размерность входного вектора) и количества единичных бит в каждом классе от 1 до m — 1(m — разрядность настроечных входов группы), Классификатор содержит треугольную матрицу процессорных модулей.

Цель изобретения достигается за счет возможности перенастройки процессорных модулей. 2 ил. ный модуль 4ij (фиг. 2) содержит инвертор 5, элемент И 6, информационные вход 7 и выход 8, настроечные вход 9 и выход 10, логические блоки 11 (i=1, m-1), каждый из которых, в свою очередь, содержит элемент

И 12 и элемент ИЛИ 13, Классификатор логического вектора является настраиваемым устройством. На:-.тройка осуществляется подачей на группу астроечных входов чисел АР12,. 3д, заданных в нормали ованном унитарном коде

4 (ч1, lip,..... „II азличные значению этих чисел соответствуют различным режимам работы.

EcllN А) =А =..Ы@=1, То реализуется ре жим подсчета единичных бит во входном векторе.

Если i4 = 2=..йдФ1 то реализуется деление количества единичных бит и(a ) входного вектора а на числоч

1683003

Если числа А различны, то реализуется режим классификации входного вектора а в зависимбсти от количества единичных бит п(a ) по классам

Q, и1,....QL-1 а е С 4, если и (а ) 6 (0, Õ, 1; а 6 Q, если п (а ) 6 (А, i4 + i4(; а Е Й, если и(а ) e (Л +Л Я1 +Л2 +Аз(1-2 L — 1 а 6 И -1,если п(а) Г, дД (1 =1 l-1 где о, ih...,. k.— < — длины интервалов значений количества единичных бит соответствующих классов;

L — количество классов.

Первый и второй режимы работы являются частными случаями третьего режима.

Рассмотрим третий режим работы классификатора, Каждый процессорный модуль выполняет функции согласно таблице.

Как следует из таблицы, в каждом столбце процессорных модулей 4 реализуется операция вычитания из текущего логического вектора сц,„„, который может быть рассмотрен, как число в разреженном унитарном коде, числа Я в нормализованном унитарном коде. При этом в выходном логическом векторе данного столбца а,„„, на 4 единичных бит меньше, чем во входном c4,„x,, следовательно, если в текущем логическом векторе при его n рохождении слева направо (см, фиг. 1) число единичных бит n(а ) > ч, то на I-м выходе группы формируется сигнал логического нуля. Если n(c4) с k, то на I-м выходе группы формируется сигнал логической еди. ницы.

Таким образом, на выходах группы классификатора формируется результат в нормализованном унитарном коде, соответесли 4x > О;

i4x авых = 0

Явись " "О если Яех - О, 35 ав - a x где Я х и Я ых -значения соответственно на настроечных входе и выходе процессорного модуля; а к и а цх — значения соответственно на информационных входе и выходе процессорного модуля. ствующий номеру класса, которому принадлежит входной вектор.

Формула изобретения

Классификатор логического вектора, со5 держащий треугольную матрицу размерности N процессорных модулей (i,j) (l,j=1 N, i-) М, N — размерность входного вектора), причем I-й вход группы информационных входов классификатора подключен к

10 информационному входу(1, 1)-ro процессорного модуля, информационный вход(1, к)-го процессорного модуля подключен к информационному выходу(1, к-1)-го процессорного модуля (к=2, N), i-й вход группы

15 настроечных входов классификатора подключен к настроечному входу(1, i)-го процессорного модуля, настроечный вход (к, 1)-го процессорного модуля (l--1, N— - 1) подклюЧен к настроечному выходу(к — 1, I)-го процессор20 ного модуля, настроечные выходы (l, N)-x процессорных модулей образуют группу выходов классификатора, о т л и ч а юшийся тем, что, с целью расширения функциональных возможностей эа счет про25 извольного выбора числа классов от 1 до N и количества единичных бит в каждом классе от 1 до m-1 (m — разрядность настроечных входов группы), каждый процессорный модуль выполнен с воэможностью реализации

30 следующей функции:

1683003

I l ! !! !

2 8 Рог.!

Фиг. Г

Составитель К. Кухаренко

Редактор С. Патрушева Техред M.Ìîðãåíòàë Корректор О. Ципле

Заказ 3413 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5,Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101