Устройство для анализа нечетких данных

Иллюстрации

Показать всеРеферат

Изобретение относится к технической кибернетике и может быть использовано при построении технических средств обработки нечеткой информации, моделирования нечетких рассуждений, автоматизации процедур выработки управляющих решений в нечетких условиях. Цель изобретения - расширение функциональных возможностей за счет обеспечения возможности упорядочивания десятичных чисел и выполнения операций объединения, пересечения и дополнения нечетких множеств. Устройство содержит блок 1 маскирования, к блоков анализа (БА) 2|-2 (к - количество десятичных разрядов унитарно-десятичного

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (si}s G 06 F 7/02

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4649574/24 (22) 13.02,89 (46) 07.10.91. Бюл. М 37 (71) Таганрогский радиотехнический институт им, В. Д. Калмыкова .(72) А. Н. Мелихов, В. П. Карелин и В. И, Кодачигов (53) 681.325.5(088.8) (56) Авторское свидетельство СССР

I4 1156060, кл. G 06 Г 7/02, 1984.

Авторское свидетельство СССР

O 1590999, кл. 6 06 F 7/02, 1988. (54) УСТРОЙСТВО ДЛЯ АНАЛИЗА НЕЧЕТКИХ ДАННЫХ

„, SU,, 1683004 А1 (57) Изобретение относится к технической кибернетике и может быть использовано при построении технических средств обработки нечеткой информации, моделирования нечетких рассуждений, автоматизации процедур выработки управляющих решений в нечетких условиях, Цель изобретения — расширение функциональных возможностей за счет обеспечения возможности упорядочивания десятичных чисел и выполнения операций объединения, пересечения и дополнения нечетких множеств, Устройство содержит блок 1 маскирования, к блоков анализа (БА) 2 -2 (к — количество десятичных разрядов унитарно-десятичного

1683004 кода анализируемых чисел), вход 3 начальной установки, тактовый вход 4, входы десятичных разрядов первого 5> — 5к и второго

61-6к чисел (А и В) УстРойства, входы 711-7mk анализируемых чисел C< — Сп (n — количество анализируемых чисел; m — количество унитарных разрядов унитарно-десятичного кода), управляющие входы 8, 9, 10, выходы

"1"11 — 11mk рЕЗуЛЬтата. БА СОдЕржИт П ЭЛЕментов ИЛИ и m узлов сравнения, входы 14 и выходы 15 маскирования; Каждый узел сравнения содержит группы элементов И, Изобретение относится к технической кибернетике и может быть использовано при построении технических средств обработки нечеткой информации, моделирования нечетких рассуждений, автоматизации процедур выработки управляющих решений в нечетких условиях.

Устройство предназначено для реализации операций определения максимального или минимального числа иэ группы чисел, сортировки чисел или в порядке убывания, или в порядке возрастания, а также для выполнения операций дизьюнкции, коньюнкции, Отрицания, импликации, штрих

Шеффера, стрелка Пирса над нечеткими перемен ными (высказы вани я ми) в нечеткой логике Заде и операций объединения или пересечения и нечетких множеств, дополнения нечеткого множества. Результат 9 операции диэъюнкции и нечетких переменных

Сь l=1, и, вычисляется по формуле

0-max=Сь результат К операции коьюнкции и-нечетких переменных С вычисляется по формуле K=minCt. Результат l операции импликации АФ С1 двух нечетких переменных А и С вычисляется по формуле 1=вах(1А, Ci), где l — А=А — есть отрицание (дополнение) нечеткой переменной А. Результат S операции штрлх Шеффера нечетких переменных А и В вычисляется по формуле Я=пах(1 — А, 1 — В). Результат Р операции стрелка Пирса нечетких переменных

А и В вычисляется по формуле P=mln(1 — А, 1-В).

Каждый элемент elf, где )=ф а Е— объединение нечетких множеств С1, W, Сп, вычисляется по формуле

el=max(Cl, CI... C l"), где C)6 Ct, а элемент

fl E F, где Р— пересечение нечетких множеста б, Съ .", ь -п, вычисляется по формуле

1 =пи п{С, С1,..., С ь). Элемент hl C Н, где. H

40 три элемента ИЛИ, элемент И, элемент И—

НЕ. Устройство может выполнять операции определения максимального и минимал Ного числа, сортировку чисел в порядке возрастания или убывания, операции дизьюнкции, конъюнкции, отрицания, импликации, штрих Шеффера, стрелка Пирса над нечеткими высказываниями в нечеткой логике Заде и операции объединения или пересечения и нечетких множеств, дополняя нечеткие множества, 3 ип. — дополнение нечеткого множества А, вычисляется по формуле hi=1-al, где al 6.А.

При определении экстремальных чисел и при сортировке сравниваемые числа представляются унитарно десятлчным кодом, так что каждый разрядный коэффициент исходного десятичного числа закодирован mразрядным унитарным кодом (один из m разрядов единичный, остальные нулевые).

При реализации перечисленных операций нечеткой логики числа А, В, С, О, К, l, Р, S, а, e, f, n из интервала (0,1) представляются

m — разрядным унитаpHblM кодом (Один раз ряд единичный, остальные нулевые), Цепь изобретения -- расширение функциональных возможностей за счет обеспечен,я воэможности упорядочивания десятичных чисел и выполнения операций обьединения, пересечения и дополнения нечетких множеств.

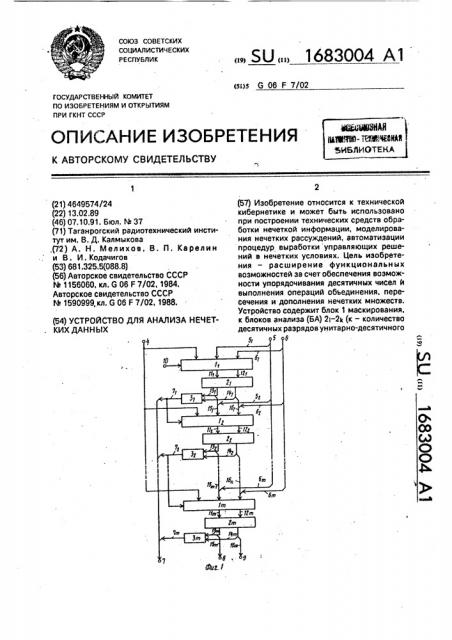

Схема устройства приведена на фиг. 1; на фиг. 2 и 3 приведены схемы I-го блока анализа (1=1; 2, ..., К) и блока маскирования.

Устройство содержит блок 1 маскирования, к блоков 2> — 2i< анализа, где k — количество десятичных разрядов унитарно-десятичного кода анализируемых частиц, вход 3 начальной установки, тактовый вход 4, входы 5,— 5 десятичных разрядов первого А и входы 6> — Gt-, второго В чисел ус-ройства, входы 711 — 7п анализируемых чисел С>, С2,...,Cn(п — количество анализируемых чисел; m — количество унитарных разрядов унитарно-десятичного кода), управляющие входы 81-8, 9>-9, 10 -10k, выходы 11 — 11п1k результата.

Блок 2 анализа содержит и элементов

ИЛИ 121-12П, и m узлов 13 -13ьп сравнения, входы 141 — 14, и выходы 15> — 15П маскирования, Каждый узел сравнения содержит группы элементов И 16> — 16п и 171 — 17п, элементы ИЛИ 18, 19, 20, элемент И 21, элемент И вЂ” Н Е 22.

1683004

45 ь0

Блок 1 маскирования содержит регистр

23 и группы элементов И 24 -24п и 251 — 25ne входы 261-26п и выходы 271 — 27, маскирования, На входы 5) и 6) где J=1,2„,m, k=1, 2...К поступает )-й унитарный разряд 1-ro десятичного разряда соответственно первого и второго чисел А и В. На вход ?j поступает

J-й унитарный разряд 1-го десятичного разряда I-ro ан лизируемого числа(М1, 2, ..., и).

На выходе 11у формируется )й унитарный разряд I-го десятичного разряда результата.

Единичный сигнал на i-м выходе 27i блока 1 маскирования означает, что 1-е число разрешено к анализу.

Устройство работает следующим образом.

При выделении максимального из и чисел, представленных в унитарно-десятичном коде, на входы 7 поступают числа С>, Cz, ..., Cn.

Регистр 23 блока 1 маскирования уста- новлен в нулевое состояние сигналом с входа

3. При этом на выходах2? блока 1 будугединичные сигналы, поступающие с инверсных выходов регистра 23. Эти сигналы поступают на входы 14 маскирования блока 21 анализа.

На входы 5, 6, 10, 13 всех блоков 2 подаются нулевые сигналы, а на входы 9 — сигнал логической "1". Так как единичными сигналами с входом 14 открыты все элементы И

16 -16 во всех узлах 13>-13 сравнения блока 21 анализа, то на выходах элементов

ИЛИ 18 образуется код, представляющий собой поразрядную дизъюнкцию унитар ных кодов сравниваемых в.блоке 2> первых (старших) десятичных разрядов чисел С>С>. Пусть в этом двоичном коде, образованном состояниями выходов элементов ИЛИ

18 всех узлов 13, старшая единица находится в первом разряде. Единичный сигнал с выхода элемента ИЛИ 18 в первом узле 131. через элемент И 21 поступает на выход 11> данного блока 21.анализа, так как на другом входе элемента И 21 также будет единичный сигнал, поступающий с выхода элемента ИНЕ 22 и обусловленный наличием нулевого сигнала, который с входа 8 поступает на второй вход элемента И-НЕ 22. Кроме того, единичный сигнал с выхода элемента ИЛИ

18 узла 13> сравнения проходит на выход элемента ИЛИ 19 данного узла 13> сравнения и далее на выходы элементов ИЛИ 19 всех младших узлов 13 -13 и поступает на вторые входы элементов И-НЕ 22 в этих младших узлах. На первые входы элементов

И-HE 22 вс:-.:-; узлов 131 — 13m поступает единичный сигнал, проходящий с входа 9 на выходы всей цепочки последовательно сое55

35 диненных элементов ИЛИ 20 всех уэлс :

13m-13> анализа. Поэтому на выходах элементов И вЂ” НЕ 22 во всех узлах, начиная с второго 13 -13m, будет нулевой сигнал, который запирает элементы И 21 в этих узлах, обуславливая тем самым нулевой сигнал на выходах 11г-11m независимо от состояния элементов ИЛИ 18 в этих узлах 13 сравнения. Пусть в коде, образованном состояниями элементов ИЛИ 18 всех узлов сравнения 13>-13, старшая единица находится в $-м разряде, где 2 S S m. В этом случае описание работы группы узлов 13,, 13 +>,...,13 анализа аналогично рассмотренному, если с выхода элемента ИЛИ 19 ($-1)-го узла 13s-< сравнения на вход элемента ИЛИ 19 и второй вход элемента И-HE 22 узла 13s+> поступает нулевой сигнал. Для рассматриваемого случая на выходах элементов ИЛИ 19 всех узлов 13> — 13s-> будет нулевой сигнал, так как во всех этих узлах на выходах элементов ИЛИ 18 имеется нулевой сигнал. На выходах 11 — 11s-> узлов

131-13s-1 сравнения будут нулевые сигналы. Таким образом, на выходах 11 -11m первого блока 2>,анализа будет унитарный код с единицей в S-м разряде, что соответствует унитарному коду максимального из сравниваемых первых десятичных разрядов чисел

С1, С2,..., Сп.

Одновременно единичные сигналы формируются на выходах тех элементов И 17, которые соответствуют числам, у которых первый десятичный разряд равен первому десятичному разряду максимального из чисел С. Эти единичные сигналы через элементы ИЛИ 12 проходят на соответствующие выходы 15 маскирования блока 2 анализа и разрешают дальнейший поиск максимального числа среди этого подмножества чисел С. Следующие блоки 2 работают аналогично.

Поиск минимального числа выполняется аналогично. При этом на входы 8 поступают единичные, а на входы 9 — нулевые сигналы.

Сортировка чисел по возрастанию или убыванию выполняется как п последовательных операций поиска максимального или минимального числа. При этом каждое вновь найденное число на следующих тактах маскируется единичным состоянием соответствующего разряда регистра 23 блока

1 маскирования.

При выполнении операции объединения и пересечения нечетких множеств в регистре 23 блока маскирования устанавливается нулевое состояние, что определяет единичные сигналы на выходах 27, 1683004

На входы 5, 6 всех блоков 2 анализа подаются нулевые сигналы, а на входы 10 — единичные сигналы. Если отыскивается объединение (пересечение), то устройство работает так же, как при поиске максимального (минимального) числа, с той лишь разницей, что каждый из блоков 2 работает независимо от других, что обеспечивается подачей единичного сигнала с входа 10 каждого блока на входы всех элементов ИЛИ

121-12п всех блоков 2. Таким образом, на всех входах 14 маскирования каждого из блоков 2 будут единичные разрешающие сигналы.

При выполнении операции отыскания дополнения нечеткого множества А унитарный m-разрядный код каждого 1-го элемента а! А, где i=1, k, подается соответственно на входы 5 каждого 1-го блока 2I На входы 6 и

7 каждого блока 2 подаются нулевые сигналы, а на входы 10 — единичные, В регистре

23 установлено нулевое состояние, что определяет единичные сигналы на входах 14 маскирования всех блоков 2. Подавая на входы 8 и 9 каждого блока 2 сигналы соответственно "Логический 0" и "Логическая

1", получают на выходах 11 1-ro блока 2 унитарный код числа а =1 — а, что в совокупности на выходах 11 всех блоков 21 — 2к определяет дополнение нечеткого множества А, Работа каждого блока 2 устройства при этом аналогична выполнению операции выделения максимального числа.

Выполнение операции отрицания а=1 — а нечеткой переменной а, представленной mразрядным унитарным кодом, осуществляется на одном из блоков 2 устройства. При этом его работа совпадает с работой при выполнении операции отыскания дополнения нечеткого множества А, с той лишь разницей, что работает лишь один блок 2, а остальные блоки в это время могут в зависи мости от настройки выполнять другие операции над нечеткими переменными, представленными также m-разрядным унитарным кодом.

Выполнение операции дизъюнкции и конъюнкции может производиться над неч ткими переменными, заданными как в унитарно-десятичном коде с q < k десятичными разрядами, так и в m-разрядном унита р нам коде. В первом случа е работа устройства при выполнении oneð4öèè дизьюнкции (конъюнкции) полностью совпадает с рассмотренной выше при отыскании максимального(минимального) из и сравниваемых чисел, Во втором случае каждая из операций может выполняться в каком-либо одном блоке 2 устройства. При этом на входы 7, где j=1, m, этого I-ro блока 2I подаются

j-е разряды m-разрядных унитарных кодов сравниваемых чисел, а на входы 5 и 6— нулевые сигналы. На входы 10 всех блоков

2 подаются единичные сигналы, что обуславливает независимую работу каждого блока 2. При выполнении в блоке 2 дизъюнкции на входы 8 и 9 этого блока подаются сигналы соответственно "Логический О" и

"Логическая 1", а при выполнении конъюнкции — наоборот.

Операции импликации, стрелка Пирса и штрих Шеффера могут выполняться над нечеткими переменными, значения которых представляются только а-разрядными унитарными кодами, Поэтому каждая из этих операций может быть реализована на одном из блоков 2 при независимой работе каждого из блоков, что обусловлено подачей единичных сигналов на входы 10 всех блоков 2.

При реализации операции импликации в блоке 2(разряды унитарного кода значения нечеткой переменной А подаются на входы 5 этого блока, а каждый j-й разряд унитарного кода переменной С подается на первый вход каждой группы входов 7 блока

2j. На все остальные входы 7 и входы 6 подаются нулевые сигналы, Блок 2i работает при этом в режиме поиска максимума, что определяется подачей на вход 8 логического

"0", на вход 9 — "1".

I pи выполнении операции стрелка Пирса (штрих Шеффера) в блоке 2 он работает как первый блок 2I,при выполнении операции IIQvlcKB минимального (максимального) числа, с той лишь разницей, что сравниваемые числа А и В подаются на входи 5 и 6 блока, а на все входи 7 подаются нулевые сигналы.

При одновременном выполнении разных операций нечеткой логики (из перечисленных) в блоках 2 устройства все. эти блоки работают независимо за счет подачи на входы 10 всех блоков единичного сигнала. Настройка входов каждого из блоков на реализацию тай или иной операции рассмотрена ви ше.

Формула изобретения

Устройство для анализа нечетких данных, содержащее блок маскирования и первый блок анализа, который содержит и элементов ИЛИ (и — количество анализируемых чисел) и m узлов сравнения {m- количество унитарных разрядов унитарно-десятичного кода анализируемых чисел), каждый узел сравнения содержит две группы элементов И, три элемента ИЛИ и элемент И, причем вход начальной устанонки устройства и тактовый вход устройства соединены соответственно с входом

1683004

10 начальной установки и тактовым входом блока маскирования, i-й выход которого, где

l-1, 2,...,п, соединен с 1-м входом маскирования первого блока анализа, входы j-x уни- . тарных разрядов первых десятичных 5 разрядов первого и второго чисел устройства, где j-1, 2...,m, соединены с входами j-x разрядов соответственно первого и второго чисел первого блока анализа, вход J-ro унитарного разряда первого десятичного раз- 10 ряда i-ro анализируемого числа устройства соединен с 1-м информационным входом j-й группы первого блока анализа, первые управляющие входы первой и второй групп устройства соединены соответственно с 15 первым и BTopblM управляющими входами первого блока анализа, J-й информационный выход первого блока анализа является выходом J-го унитарного разряда первого десятичного разряда результата устройст- 20 ва, в блоке анализа входы его J-x разрядов первого и второго чисел соединены соответ-. ственно с первым и вторым входами перво-го элемента ИЛИ (в+1-J)-го узла сравнения, i-й вход маскирования блока анализа соеди- 25 нен с первыми входами 1-х элементов И первой группы всех узлов сравнения, 1-й информационный вход J-й группы блока анализа соединен с вторым входом 1-го элемента И и первой группы J-ro узла сравне- 30 ния, в каждом j-м узле сравнения выход i-ro элемента И первой группы соединен с первым входом i-го элемента И второй группы и с (I+2)-м входом первого элемента ИЛИ, выход элемента И является J-м информаци- 35 онным выходом блока анализа и соединен с вторыми входами всех элементов И второй группы j-ro узла сравнения, выход i-го weмента И второй группы j-ro узла сравнения соединен с J-м входом 1-ro элемента ИЛИ, 40 выход которого является 1-м выходом маскирования блока анализа, о т л и ч а ю щ ее с я тем, что, с целью расширения функциональных возможностей за счет обеспечения возможности упорядочивания 45 десятичных чисел и выполнения операций объединения, пересечения и дополнения нечетких множеств, в него введены k 1 блоков анализа, идентичных первому блоку анализа, где k — количество десятичных разрядов унитарно-десятичного кода анализируемых чисел, а в каждый узел сравнения введен элемент И вЂ” НЕ, причем входы j-x унитарных разрядов I-го десятичного разряда первых чисел первой и второй групп устройства, где 1=2, 3,...,k, соединены.с входами j-x разрядов соответственно первого и второго чисел 1-го блока анализа, вход )-га унитарного разряда 1-го десятичного разряда I-го анализируемого числа устройства соединен с

1-м информационным входом i-й группы 1-го блока анализа, l-e управляющие входы первой и второй групп устройства соединены соответственно с первым и вторым управляющими входами l-ro блока анализа, J-й информационный выход 1-ro блока анализа является выходом J-ro унитарного разряда

1-го десятичного разряда результата устройства, I-й выход маскирования (1-1)-го блока анализа соединен с 1-м входом маскирования I-го блока анализа, 1-й выход маскирования к-го .блока анализа соединен с I-м входом маскирования блока маскирования, в каждом узле сравнения выход первого элемента ИЛИ соединен с первыми входами второго и третьего элементов ИЛИ, выход элемента И вЂ” НЕ соединен с вторым входом элемента И, в каждом блоке анализа его первый управляющий вход соединен с вторым входом второго элемента ИЛИ и с первым входом. элемента И вЂ” НЕ первого узла сравнения, выход второго элемента ИЛИ рго узла сравнения, где р=1., 2,..., (m-1), соединен с вторым входом второго элемента

ИЛИ и первым входом элемента И вЂ” НЕ (o+1)го узла сравнения, в каждом блоке анализа его второй управляющий вход соединен с вторыми входами третьего элемента ИЛИ и элемента И вЂ” НЕ m-го узла сравнения, выход третьего элемента ИЛИ (р+1)-го узла сравнения соединен с вторыми входами третьего элемента ИЛИ и элемента И вЂ” НЕ р-ro узла сравнения, q-й управляющий вход третьей группы устройства, где q=1. 2,..., К соединен с (m+1)-и входами всех элементов ИЛИ и

q-го блока анализа.

1683004

1683094

2А

Составитель В. Горохов

Техред М.Моргентал Корректор О. Ципле

Редактор Т. Юрчикова

Производственно-издательский комбинат "Патент", r. Ужгород, ул.Гагарина, 101

Заказ 3413 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35. Раушская наб., 4/5