Блок выбора направления обмена децентрализованной вычислительной системы

Иллюстрации

Показать всеРеферат

Изобретение относится к автомат/, п вычислительной технике и может быть использовано при реализации технических средств параллельной обработки информации Цель изобретенияповышение быстродействия децентрализованной вычислительной системы в режиме множественного доступа за счет исключения взаимных блокировок. Цель достигается введением схемы сравнения кодов приоритетов, элементов И, ИЛИ, НЕ Состояние взаимной блокировки блоков, сопровождающееся их непроизводительными простоями, автоматически исключается предлагаемым блоком на приоритетной основе с помощью схемы сравнения кодов приоритетен- 1 ил

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (sa)s G 06 F 15/16

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4745560/24 (22) 03.10.89 (46) 07.10.91. Бюл, ¹ 37 (71) Научно-производственное объединение интегрированных микроэлектронных систем (72) Ю,Н.Максименко и В,С,Ракошиц (53) 681,325(088,8) (56) Авторское свидетельство СССР

N 894701, кл. G Об F 7/00, 1980.

Авторское свидетельство СССР

¹ 1168961, кл. G 06 F 15/16, 1984, (54) БЛОК ВЫБОРА НАПРАВЛЕНИЯ ОБМЕНА ДЕЦЕНТРАЛИЗОВАННОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ

Изобретение относится к автоматике и вычислительной технике и может быть использовано при реализации технических средств параллельной обработки информации.

Цель изобретения — пэвышение быстродействия де централ изова н ной вычислительной системы в режиме множественного доступа за счет исключения взаимных блокировок.

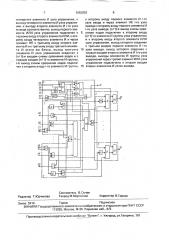

На чертеже представлена функциональная схема предложенного блока.

Блок содержит пузлов 1 ввода,,и узлов

2 вывода и узел 3 управления. Узел 1 ввода содержит первый и второй элементы ИЛИ 4 и 5, первый и второй элементы И 6 и 7, элемент НЕ 8. Узел 2 вывода содержит первый и второй элементы И 9 и 10 и элемент

Н Е 11. Узел 3 управления содержит схему 12 сравнения кодов, элемент И вЂ” НЕ 13. первый— четвертый элементы И 14 — 17, группу из и+1

„„. Ж„„1683026 А1 (57) Изобретение относится к автамати1;е и вычислительной технике и может быть использовано при оеализации технических средств параллельной обработки информации, Цельизобретения — повышение быстродействия децентрализованной вычислительной системы в режиме множественного доступа за счет исключения взаимных блокировак. Цель достигается введением схемы сравнения кодов приоритетов, элементов И, ИЛИ, НЕ. Состояние взаимной блокировки блоков, соправожда1още еся их непраизводите ьными простоями, автоматически искл1с Га тся предлагаемым блоком на приоритетной основе с помощыа схемы соВВ нения кодов приоритетос, 1 ил. элементов И 18, первый — третий элементы

ИЛИ 19 — 21 и элемент НЕ 22. Блок содержит информационные входь1 23, céácòâ| ííûé информационный вход 24, вход 25 запроса доступа, вход 26 квитирования, вход 27 контроля собственных направлений. вход 28 признака состояния смежных блоков, выход 29 квитирова1:ия запроса дасту-à,,выход 30 квитирования, выход 31 блокировки запроса доступа и информационные выходы 32.

Каждому блоку выбора направления обмена децентрализованной вычислительной системы соответствует cBGlt ресурс, который подключен к блоку с помощью входов

24, 25 и выходов 29, 31. Под ресурсом понимается элемент вычислительной системь

{процессор, блок памяти). который может находиться в активном или пассивном состоянии. Активное состояние ресурса характеризуется единичным состоянием входа 25

1683026 запроса доступа, а пассивное состояние— нулевым состоянием входа 25, Все блоки с помощью входов 23, 26 и выходов 30, 32 обьединены между собой и образуют заданную физическую структуру вычислительной системы. Все ресурсы вычислительной системы общедоступны, т.е, каждый активный ресурс системы (например, процессор) может затребовать доступ ко всем пассивным ресурсам системы. Поскольку вычислительная система децентрализованная, то в данный момент в системе может возникнуть несколько запросов на доступ к общим ресурсам. Множественный доступ к общим ресурсам — это организация децентрализованного упорядоченного доступа к общим пассивным ресурсам сигтемы, искл о lающая взаимные блокировки, Исключение взаимных блокировок и упорядочение доступа к общим ресурсам осуществляются на приоритетной основе. Каждый за рос доступа к ресурсам сопровождается своим приоритетом (номером). Блок выбора направления обмена обрабатывает наиболее приоритетный запрос, а в источник менее приоритетного запроса транслируется сигнал блокировки запроса, Рассмотрим работу блока в режиме множественного доступа к общим ресурсам, Источник запроса доступа к ресурсам (активный ресурс) формирует единичный потенциал запроса доступа к ресурсам и код своего номера (приоритета), которые поступят на блок по входам 24, 25, Если данный блок к этому моменту времени не охвачен запросами, поступившими or смежных блоков, то на выходе элемента ИЛИ 19 узла 3 управления будет нулевой потенциал, который через элемент НЕ 22 открывает элемент И 16 и разрешает поступление кода приоритета на (п+1)-й вход схемы 12 сравнения кодов. На (и+1)-м выходе схемы 12 формируется единичный потенциал, который через элемент ИЛИ 20 поступает на третьи входы элементов И 9 узлов 2 вывода.

Если по транзитным исправным Направлениям в данный блок не поступают запросы по входам 28, то на вторых и первых входах элементов И 9 устанавливаются единичные потенциалы, на выходе указанных элементов формируются единичные потенциалы, которые открывают элементы И

10. Код приоритета собственно запроса с выхода элемента И 16 через (и+1)-й элемент

И 18 и элемент ИЛИ 21 поступает на информационные входы элементов И 10 и с выходов этих элементов по выходам 32 транслируется в смежные блоки. Блок, подключенный к собственному источнику запроса доступа к ресурсам, является

55 центром формирования волны запроса, которая охватывает все блоки системы (если данный запрос наиболее приоритетный).

Рассмотрим обработку запросов в текущем блоке системы. Коды приоритетов запросов доступа к ресурсам поступают в блок по входам 23 и подаются на схему 12 сравнения кодов, На выходах схемы 12 формируются единичные потенциалы, соответствующие направлениям поступления приоритетных запросов, которые поступают на вторые входы соответствующих элементов И 6, Если приоритетное направление исправно, то на входах 27 контроля и

28 состояния соответствующего приоритетного направления устанавливаются нулевые IIoòåíциалы (соответствующими блоками контроля и состояния, не показанными на схеме). На выходе элемента ИЛИ 5 устанавливается нулевой потенциал, которь»й, инвертируясь элементом НЕ 8, открывает по первому входу элемент И 6, и единичный потенциал приоритетного запроса через элемент ИЛИ 19 поступает на третьи входы элементов И 9 узлов 2 вывода.

Элементы HE 11 подключают лишь те узлы вывода, которые не соответствуют приоритетным направлениям поступления запросов. Элементы НЕ 8 включают узлы вывода, соответствующие исправным направлениям, Таким образом, на выходах элементов И

9 фoрмируются единичные IloòåèHH алы, соответствующие тем исправным Н» равлениям, которые не пересекаются с направлениями поступления приоритетных запросов. Этим обеспечивается направленное распространение волны приоритетного запроса ресурсов по исправным направлениям и блокам, Код номера приоритетного запроса с выхода элемента ИЛИ 21 через подключенные элементы И 10 транслируются по шинам 32 в смежные блски. Процес,: распространения волны приоритетного запроса заканчивается на граничнь»х;3". эках системы, которые характеризуются наличием единичных потенциалов на всех первых выходах схемы 12 сравнения кодов. При наличии исправного состояния указанных направлений на выходах элементов И 6 формируются единичные потенциалы, которые через элементы ИЛИ 4 включат элемент

И 14, На выходе элемента И 14 формируется единичный потенциал квитирования запроса, который через подключенные элементы

И 7 по выходам 30 транслируется обратным кодом во все смежные блоки. Смежный блок

HB этапе квитирования работаетаналогично граничному блоку, В этом случае по любому исправному входному направлению в узел 1

1683026

30 сурсэм, в результате отказа и его ветвей или 40

55 ввода поступает либо потенциал квитирования по входу 26, либо потенциал приоритетного запроса с выхода элемента И 6, которые объединяются элементом ИЛИ 4 и поступают на вход элемента И 14, На выходе элемента И 14 формируется единичный потенциал, если данный блок охвачен сигналами квитирования или сигналами приоритетного запроса по всем и исправным направлениям, В блоке, соответствующем источнику волны запроса ресурсов, на входах 26 появляются сигналы квитирования по всем и исправным направлениям. На выходе элемента И 14 формируется сигнал логической "1", который поступает на второй вход элемента И 15, который управляется по первому входу потенциалом признака запроса доступа к ресурсам с входа 25. В блоке, соответствующем источнику волны запроса, на выходе элемента ИЛИ 19 будет нулевой потенциал, который через элемент

HE 22 включает элемент И 15. На выходе элемента И 15 формируется единичный потенциал квитирования запроса доступа к ресурсам, который по выходу 29 поступает в соответствующий источник запроса.

Если блок, запрашивающий доступ к ресурсам, охвачен волной запроса, поступившей по входу 23. от смежных блоков, то на выходе элемента ИЛИ 19 формируется единичный потенциал, который включает элемент И 17. На выходе элемента И 17 формируется единичный потенциал блокировки запроса доступа блока, который по выходу 31 транслируется в соответствующий ресурс, Ресурс по данному сигналу снимает свой запрос доступа на входе 25 и повторяет его через некоторое время, Если блок, запрашивающий доступ к ревсех его смежных блоков изолирован от системы, то на выходе элемента И вЂ” НЕ 13 формируется нулевой потенциал, который выключает элемент И 14 и блокирует формирование сигнала квитирования -апроса.

Формула изобретения

Блок выбора направления обмена децентрализован ной вычислительной системы, содержащий и узлов ввода (n — число смежных направлений), и узлов вывода и узел управления, причем каждый I-й узел ввода(1 =-1, и) содержит элемент НЕ, первый и второй элементы И и первый и второй элементы ИЛИ, каждый 1-й узел вывода содержит элемент НЕ и первый элемент И, а узел управления содержит первый и второй элементы И, первый элемент ИЛИ и элемент И-Н Е, при этом входы контроля собственного направления, признака состояния

20 смежного блока, квитирования и выходы квитирования соответствующих направлений блока выбора направления обмена децентрализованной вычислительной системы являются первым и вторым входами второго элемента ИЛИ, первым входом первого элемента ИЛИ и выходом второго элемента И соответственно i-го узла ввода, вход запроса доступа и выход квитирования запроса доступа блока выбора направления обмена децентрализованной вычислительной системы являются первым входом и выходом второго элемента И соответственно узла управления, выход второго элемента

ИЛИ 1-го узла ввода соединен с вторым входом первого элемента.ИЛИ l-ro узла ввода, с I-м входом элемента И вЂ” НЕ узла управления и через элемент НЕ 1-ro узла ввода с первым входом первого элемента И i-го узла ввода и с первым входом первого элемента

И I-го узла вывода, выход первого элемента

И I-ro узла ввода подключен к третьему входу первого элемента ИЛИ i-го узла ввода, к первому входу второго элемента И I-го узла ввода и к i-му входу первого элемента ИЛИ узла управления, выход первого элемента

ИЛИ i-го узла ввода соединен с I-м входом первого элемента И узла управления. выход которого подключен к в.,орым входам вторых элементов И узлов ввода и к второму входу второго элемента И узла управления, (i+1)-й вход первого элемента И узла управления соединен с выходом элемента И-НЕ узла управления, второй вход первого элемента И i-го узла ввода соединен с входом элемента HE I-го узла вывода, выход которого подключен к второму входу первого элемента И i-го узла вывода, о т л и ч а ю щ и й-с я тем, что, с целью повышения быстродействия децентрализованной вычислительной системы в режиме множественного доступа за счет исключения взаимных блокировок, в узел управления введены схема сравнения кодов, третий и четвертый элементы И, группа из и+1 элементов И, элемент НЕ и второй и третий элементы ИЛИ, в каждый узел вывода введен второй элемент И, причем i и информационный вход блока выбора направления обмена децентрализованной вычислительной системы соединен с i-м входом схемы сравнения кодов и с первым входом l-го элемента И группы, собственный информационный вход, вход запроса доступа, выход блокировки запроса доступа и l-й информационный выход блока выбора направления обмена децентоализованной вычислительной системы подключены к первому входу третьего элемента И узла управления, к второму входу третьего элемента И узла управления и к первому входу

1683026

Составитель В,Сычев

Редактор Т.Юрчикова Техред M.Ûîðãåíòàë Корректор В Гирняк

Заказ 3414 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35. Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101 четвертого элемента И узла управления, к выходу четвертого элемента И узла управления, к выходу второго элемента И i-го узла аывода соответственно, выход первого элемента ИЛИ узла управления подключен к первому входу второго элемента ИЛИ, к второму входу четвертого элемента И и через элемент НЕ к третьему входу второго элемента И и к третьему входу третьего элемента И этого же блока, выход третьего элемента И узла управления соединен с (п+1)-м входом схемы сравнения кодов и с первым входом (и+1)-го элемента И группы, i-й выход схемы сравнения кодов подключен к второму, входу i-ro элемента И группы, к второму входу первого элемента И 1-ro узла ввода и через элемент НЕ 1-го узла вывода к второму входу первого элемента И

i-ro узла вывода, (и+1 -й выход схемы срав5 нения кодов подключен к второму входу (п+1 -го элемента И группы узла управления и к второму входу второго элемента ИЛИ узла управления, выход которого соединен с третьим входом первого элемента И I-го

10 узла вывода, выход которого соединен с первым входом второго элемента И i-ro узла вывода, выходы элементов И группы узла управления через третий элемент ИЛИ узла управления подключены к вторым входам

15 вторых элементов И узлов вывода.